在工業控制領域,為了實現采集和控制功能,經常會使用到A/D,D/A模塊。在實際使用中A/D,D/A模塊和主機之間通信方式可以有很多選擇。比如RS 232,RS 422,網絡等接口方式。在該設計中A/D,D/A模塊通過CPCI總線與主機通信,通過A/D接口采集數據,經過伺服控制軟件處理,輸出模擬量驅動執行機構。

從而實現一個閉環的控制。另外通過對DSP軟件的修改,該模塊還可以單獨實現A/D或者D/A功能。

該設計中A/D,D/A模塊具備以下功能:

(1)提供2路16位A/D,輸入信號范圍±5 V,精度要求小于士16 LSB;

(2)提供2路16位D/A,輸出信號范圍±5 V,精度要求小于土8 LSB,受系統復位控制;

(3)使用TI公司DSP(TMS320VC33)作為板載處理器,該DSP主要實現管理A/D和D/A、運行控制算法、與主機通信功能,并受系統復位控制;

(4)DSP與主機采用雙口RAM(IDT7133)實現數據交換功能。

1 設計原理

如圖1硬件結構框圖所示,該模塊采用TI公司高性能CPU器件TMS320VC33為核心。模塊通過PCI9052芯片與CPCI總線連接,PCI9052的本地總線的信號連接到雙口RAM的一端。雙口RAM的另一端通過電平緩沖器連接DSP。

DSP核心電路包括DSP芯片TMS320VC33、數據RAM CY7C1041VC33、程序FLASH芯片SST39VF800A組成;DSP的地址、數據、控制總線通過電平緩沖器件連接雙口RAM、A/D芯片、D/A芯片、CPLD。DSP通過雙口RAM芯片與主控計算機進行數據交換;A/D芯片的初始化以及讀寫操作也由DSP負責完成;DSP控制D/A芯片輸出模擬信號;CPLD內部主要實現組合邏輯功能,將DSP輸入的控制信號譯碼,然后輸出給雙口RAM以及A/D,D/A等功能芯片使用。

雙口RAM芯片是實現智能板的重要組成,由于DSP與主控計算機的地址空間資源是分別進行獨立分配的,無法直接進行互相訪問,在兩者之間需要一個數據緩沖,雙口RAM的特點使其可以滿足這個要求。

2 實現方法

2.1 主要原器件選擇

在該設計中采用成熟技術,選用常用、可靠的控制芯片,結合一些常用的外圍電路和專用電路實現全部的功能。即選擇PC19052作為接口芯片,利用該芯片實現PCI總線從接口邏輯。

選擇TMS320VC33作為板載處理芯片,該芯片是TI公司推出的專門用于實現浮點運算的高性能DSP,數據處理能力強,并且包含豐富的外圍電路擴展接口。

為了實現模塊上的電平轉換功能,選擇應用比較廣泛SN74ALVC164245DL作為電平轉換緩沖芯片。

2.2 PCI9052與雙口RAM硬件接口實現

如圖3所示PCI9052與雙口RAM連接的本地總線信號包括地址、數據、控制信號3個部分。地址總線寬度為12位,數據總線寬度為16位,因此尋址空間為2 KB的16 b地址空間。控制信號包括讀寫控制信號和外設準備完成信號,當雙口RAM將外設準備完成信號拉低后,主機就可以通過輸出讀寫控制信號對雙口RAM進行讀寫的操作。

2.3 DSP設計核心電路設計

DSP是整個設計核心,DSP核心電路由DSP芯片、FLASH和RAM三個部分組成。DSP通過雙口RAM與處理計算機交換數據。

如圖3所示,DSP核心電路設計如下所述。DSP的電源包括核心工作電壓1.8 V與I/O電壓3.3 V兩種,分別由板上電源模塊提供。時鐘信號由外接晶振提供。復位信號由CPLD提供,由于DSP的I/O電壓為3.3 V,在與I/O電平標準為+5 V的信號連接時需要進行3.3~5 V之間的電平轉換。中斷信號同樣通過電平轉換器件連接到CPLD。地址和數據總線根據實際設計的需要連接功能器件。JTAG接口連接到模塊的一個標準的雙列14腳直插連接器上。Page0~3信號通過電平轉換器件連接到CPLD。

關鍵字:CPCI總線

2.4 電源設計

系統電源包括+5 V.3.3 V,1.8 V,+15 V,-15 V。

DSP芯片核心電壓為1.8 V,I/O電壓為3.3 V,所以需要該板提供3.3 V和1.8 V兩個電壓源。D/A芯片需要提供+15 V,-15 V兩種電源。+5 V電源是由系統提供,其他的電源均由+5 V電源轉換獲得。

對于線性穩壓來說,其特點是電路結構簡單,所需元件數量少,輸入/輸出壓差可以很大,但其致命弱點就是效率低,功耗高。DC-DC電路的特點是效率高,升降壓靈活,缺點是干擾和紋波較大。

對比凌特公司、國家半導體公司、德州儀器公司等的同類型電壓轉換芯片,選取德州儀器公司的TPS73HD318模塊作為3.3 V和1.8 V電壓轉換芯片。選用RECOM公:REC3-0515DRW完成+5 V和+15 V,-15 V之間電壓轉換。他們具有90%以上的轉換效率、簡單的外圍電路、更小的封裝、2.5%以下的紋波電壓等特點。

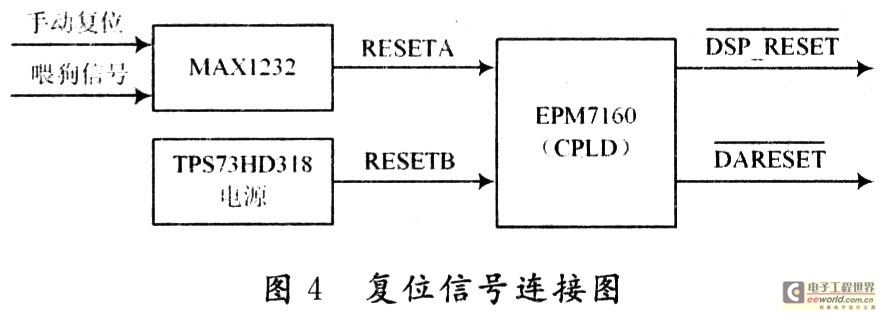

2.5 復位設計

如圖4所示,復位的輸入包括兩個部分:MAX1232輸出的RESETA和電源芯片TPS73HD318輸出的RESETB。MAX1232的輸入為手動復位信號輸入和看門狗喂狗信號輸入。手動復位信號來自復位按鈕,喂狗信號來自CPLD。復位輸出2個信號分別給DSP,D/A使用。

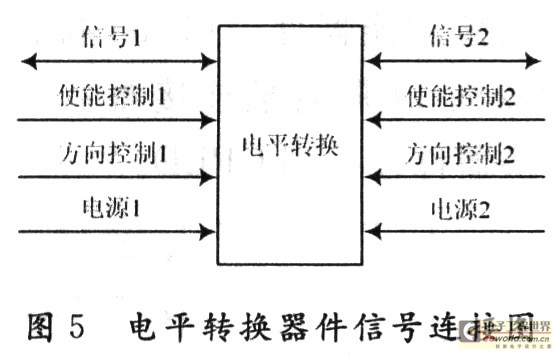

2.6 電平轉換設計

由于DSP的接口電平為3.3 V,CPLD和PC19052接口電平為5 V,為了將兩部分兼容起來,需要使用電平轉換緩沖芯片。如圖5所示該器件有兩個供電電源、兩個方向控制端、兩個使能端。通過連接不同的電壓源可以為器件的信號引腳提供不同的電平。

2.7 A/D,D/A設計

A/D和D/A芯片通過電平緩沖期間與DSP的地址數據總線連接,由DSP芯片負責A/D和D/A的初始化以及讀寫控制。

3 CPLD邏輯設計

CPLD片內邏輯實現描述框圖見圖6。在CPLD內部主要實現了三個的功能,與DSP總線的邏輯接口、內部的寄存器、控制邏輯。

與DSP總線的接口邏輯實現與DSP邏輯接口,使DSP對CPLD的內部寄存器可以進行訪問。狀態寄存器為只讀寄存器,用來讀取中斷狀態、與雙口RAM進行通信的標志位等信息;控制寄存器為只寫寄存器,用來控制中斷屏蔽、修改通信的標志位。組合邏輯主要用來進行地址譯碼、讀寫譯碼。

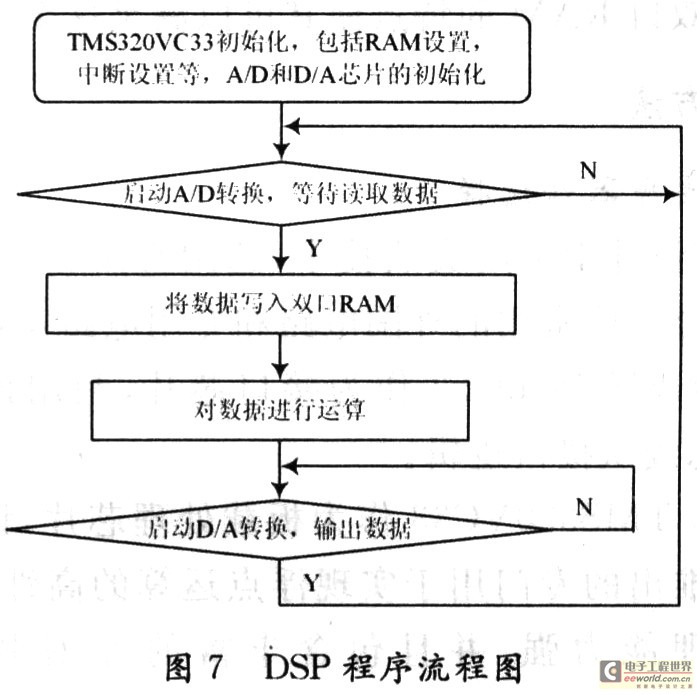

4 DSP軟件設計

DSP軟件開發主要是在TI提供的集成開發環境CCS下,充分利用實時操作系統DSP/BIOS的強大功能,結合自己特定的處理算法.快速構筑一個滿足需求的高效率的軟件系統。在設計中,對DSP的初始化是必須的,該設計主要應用于實時控制系統中,其電路的主要功能是用于采集、運算、輸出。程序流程圖如圖7所示,上電后存儲在FLASH內的程序開始運行,DSP開始依次初始化RAM存儲器、CPLD內部寄存器、A/D寄存器、D/A寄存器。初始化完成后開始讀取A/D輸入,由于A/D轉換速度比讀取的速度慢,在讀取過程中需要查詢A/D轉換狀態,等待A/D芯片輸出轉換完成信號。將讀取的數據寫入雙口RAM的指定位置,并刷新雙口RAM和CPLD內部的標志位,通知主機讀取數據。對A/D數據進行運算,根據運算結果控制D/A輸出,等待查詢D/A轉換完成之后,程序再次跳轉至讀取A/D。

5 結 語

將該設計用于某一伺服控制系統,實現了系統功能,同時對系統的穩定性和可靠性給予了足夠的關注。經長時間考核,本系統運行穩定可靠。