摘要:與通常采用外圍的CPLD器件和CPU來產(chǎn)生配置接口控制邏輯的方法不同,本文設計了采用嵌入到FPGA" title="FPGA">FPGA的Leon3" title="Leon3">Leon3開源CPU軟核來控制實現(xiàn)Virtex系列FPGA的SelectMap接口配置的方法,可將其應用于對FPGA芯片的在線配置。該方法設計成本低,不局限于某一類型的FPGA芯片,減少了外圍分立元件的使用,增強了設計的靈活性。仿真結(jié)果表明該設計滿足SelectMap接口配置所需控制邏輯要求,可以完成FPGA的并行配置。

關鍵詞:FPGA;嵌入式CPU;Leon3軟核;SelectMap接口

引言

嵌入式系統(tǒng)的硬件通常包括CPU、存儲器和各種外設器件,其中CPU是系統(tǒng)的核心,其重要性不言而喻。隨著FPGA和SOPC技術的發(fā)展,基于FPGA的嵌入式系統(tǒng)與傳統(tǒng)的嵌入式系統(tǒng)相比,具有設計周期短、設計風險和設計成本低、集成度高、靈活性大、維護和升級方便、硬件缺陷修復等優(yōu)點。基于FPGA的嵌入式系統(tǒng)設計技術和市場逐漸成熟,使得嵌入式CPU軟核(如Xilinx公司推出的MicroBlaze、Altera公司的Nios、歐空局開發(fā)的Leon3軟核等)的大量應用成為可能。

Virtex系列FPGA是Xilinx公司推出的一種高密度、大容量的現(xiàn)場可編程門陣列。該系列FPGA可支持動態(tài)重構(gòu),當FPGA邏輯功能需要轉(zhuǎn)換,如算法改進或是發(fā)現(xiàn)設計上的錯誤,或FPGA配置數(shù)據(jù)發(fā)生錯誤而導致功能失效(如在空間輻射環(huán)境下的單粒子翻轉(zhuǎn)效應導致配置數(shù)據(jù)錯誤等),則需要對FPGA進行重新配置。通常采用的配置系統(tǒng)由CPU、CPLD、FPGA和存儲器構(gòu)成。本文結(jié)合具體應用需求,介紹了利用嵌入式CPU Leon3軟核處理器對Virtex系列FPGA的配置進行控制的方法。此系統(tǒng)能夠?qū)崿F(xiàn)FPGA配置數(shù)據(jù)的重構(gòu),并且減少了外圍CPU和CPLD器件的使用,具有很好的應用價值。

1 Leon3軟核

Leon3是歐空局開發(fā)的32位CPU軟核,其標準版是一種開源的軟核,使用GNU LGPL授權(quán)協(xié)議,可以免費地應用于研究、教學和商業(yè)目的。Leon3軟核使用VHDL語言描述,與SPARC V8兼容,使用7級流水線,集成了全流水的IEEE-754浮點處理器,提高了對多處理器的支持。由于Leon系列指令集符合SPARC V8標準,外部總線符合AMBA標準,兼容軟件和IP核資源極其豐富,加上其開放源代碼的策略,對它的研究和應用受到了廣泛的關注。Leon3軟核具有良好的可配置性和可移植性,能夠根據(jù)需要靈活地選擇外圍控制器。并且該軟核不是FPGA廠商推出的,因此可以應用于不同類型的FPGA芯片。Leon3開源軟核的Grlib IP庫中提供了多種功能模塊,如串口控制器、存儲器控制器、通用可編程I/O等,把該軟核及其外圍的控制模塊集成到FPGA中,構(gòu)成一個嵌入式片上系統(tǒng)。

2 SelectMap接口配置系統(tǒng)設計

2.1 Virtex系列FPGA配置方式

Virtex系列FPGA基于SRAM工藝,共有4種配置方式:主串(master serial)、從串(slave setial)、SelectMap和邊界掃描(boundarysca-n)。串行(主串或從串)模式需要的配置信號少(PROGRAM、CCLK、DIN、INIT、DONE),F(xiàn)PGA在配置時鐘的上升沿接收1位配置數(shù)據(jù),該配置方式速度較慢。邊界掃描模式?jīng)]有存儲芯片,掉電后需重新配置,所以該種配置方式多用于調(diào)試階段。SelectMap模式是一種8位并行配置模式,它是Virtex系列FPGA最快的一種配置模式,其配置時鐘最高可達66MHz,每個配置時鐘周期內(nèi)有8位配置數(shù)據(jù)下載到FPGA內(nèi)。在對配置速度要求較高的一些應用場合,一般采用SelectMap配置方式。

SelectMap配置方式所需引腳及相應功能如表1所列。表中BUSY信號是握手信號,只有當配置時鐘的頻率超過50MHz時才起作用,本設計的配置時鐘頻率低于50MHz,因此不使用BUSY信號。M(2:0)是模式選擇信號,在SelectMap配置模式下,M(2:0)應置為110。

2.2 SelectMap接口配置硬件設計實現(xiàn)

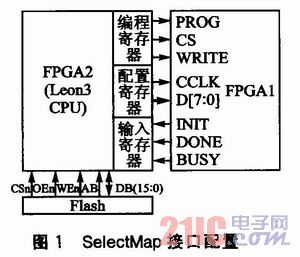

本文設計的SelectMap接口配置系統(tǒng)由兩片F(xiàn)PGA和存儲器(Flash)構(gòu)成,如圖1所示。設計中FPGA1選用了Xilinx公司Virtex系列芯片Virtex-5 XC5VSX95T" title="Virtex-5 XC5VSX95T">Virtex-5 XC5VSX95T,是需要進行配置的芯片。FPGA2內(nèi)部嵌入了Leon3 CPU軟核,可利用該CPU軟核的存儲控制器模塊對Flash進行讀寫控制;利用FPGA內(nèi)部豐富的資源,在FPGA2內(nèi)部集成一個自定義的SelectMap接口控制IP核,主要用來產(chǎn)生FPGA的配置信號,這些SelectMap配置信號的狀態(tài)由嵌入在FPGA2內(nèi)部的CPU Leon3軟核監(jiān)控。該設計采用開源的Leon3軟核CPU,并且充分利用了FPGA豐富的資源,與通常的SelectMap配置系統(tǒng)相比,設計成本低,設計較靈活。

Flash存儲器采用Intel公司的JS28F256P30T95,具有32 MB的存儲空間,用來存儲FPGA1的配置數(shù)據(jù)。因為Flash的每個地址空間中存儲著16位數(shù)據(jù),Leon3 CPU處理器讀取Flash地址中的數(shù)據(jù),然后把數(shù)據(jù)以字節(jié)形式傳送到FPGA2。這個過程中,CPU處理器所在的FPGA2為FPGA1提供配置時序控制信號。這些控制信號的產(chǎn)生由FPGA2內(nèi)部集成的SelectMap接口控制IP核實現(xiàn)。該IP核的功能模塊由3個寄存器組成:配置寄存器、編程寄存器和輸入寄存器。每次CPU對Flash進行讀或?qū)懖僮鲿r,這些寄存器存儲FPGA1的配置信號數(shù)據(jù)。其中配置寄存器和編程寄存器為只寫寄存器,輸入寄存器為只讀寄存器。詳細的邏輯框圖如圖2所示。CPU數(shù)據(jù)線在SelectMap接口控制IP核內(nèi)部寄存器的構(gòu)成如表2所列。

該配置邏輯模塊完成以下幾方面的功能:啟動FPGA1配置時序;向FPGA1內(nèi)部傳入配置數(shù)據(jù);監(jiān)測FPGA1是否正常配置。使用嵌入式CPU軟核配置FPGA1的流程如下:

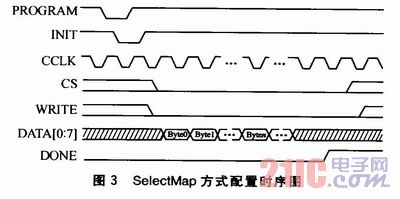

①啟動FPGA1的配置時序。CPU地址線選中FPGA2內(nèi)部編程寄存器,數(shù)據(jù)線輸出FPGA1配置控制信號CS、WRITE和PROGRAM,將CS和WRITE置低,PROGRAM置高。

②監(jiān)測FPGA的配置狀態(tài)。CPU地址線選中FPGA2內(nèi)部輸入寄存器,接收FPGA1的輸出信號INIT,若其值為高,那么CPU開始發(fā)出FPGA1的配置數(shù)據(jù),否則持續(xù)檢查INIT的值,直到其值為1。

③向FPGA1內(nèi)傳送配置數(shù)據(jù)。CPU地址線選中FPGA2內(nèi)部配置寄存器,數(shù)據(jù)線Data[15:8]輸出FPGA1的配置數(shù)據(jù),Data[0]產(chǎn)生配置時鐘CCLK,在CCLK的上升沿FPGA1接收配置數(shù)據(jù)。配置數(shù)據(jù)傳送分兩步,首先Data[0]置0,然后Data[0]置1。CCLK產(chǎn)生一個上升沿,在此過程中Data[15:8]數(shù)據(jù)保持不變。重復此過程,CPU輸出FPGA1全部配置數(shù)據(jù)。

④檢查FPGA1是否配置成功。FPGA1的配置數(shù)據(jù)被傳送至結(jié)束時,CPU地址線選中FPGA2內(nèi)部輸入寄存器,接收FPGA1的輸出信號DONE。若其值為高時,說明FPGA1配置成功,否則需要重新配置FPGA1。

SelectMap接口配置方式下FPGA的時序如圖3所示。

3 仿真及分析

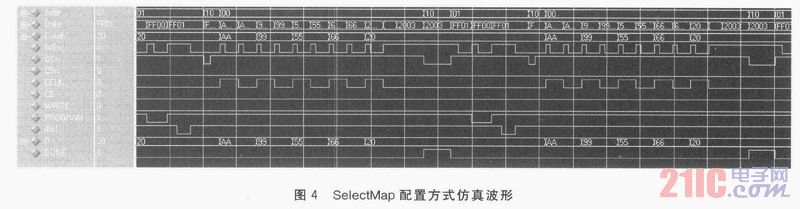

FPGA2采用Xilinx公司的Virtex-5 XC5VFX70T,SelectMap接口控制IP核采用VHDL語言實現(xiàn),嵌入式CPU軟核采用的是歐空局開發(fā)的Lcon3軟核。在XilinxISE 10.1平臺下完成對Lcon3 CPU軟核處理器、外圍控制器及自定義SelectMap接口控制IP核集成的設計、綜合,利用Modelsim SE6.0完成仿真。

SelectMap配置仿真波形如圖4所示。由于FPGA1(Virtex-5 XC5VSX95T)的配置數(shù)據(jù)較大,仿真出完整的配置過程是不現(xiàn)實的,圖中用5個字節(jié)的配置數(shù)據(jù)來代替FPGA的完整配置過程。為了把配置寄存器數(shù)據(jù)Data和并行配置的8位數(shù)據(jù)相對照,分離出了Data的高8位Data[15:8]。從圖中可以看出,在一次完整的配置過程中,CS和WRITE為低,PROGRAM為高,當監(jiān)測到INIT為高時發(fā)出配置數(shù)據(jù),在配置時鐘CCLK的上升沿接收8位配置數(shù)據(jù),DONE信號為高電平指示配置完成。該仿真結(jié)果和SelectMap配置方式的FPGA時序一致,證明了本設計的正確性及可行性。

結(jié)語

通過使用嵌入式Lcon3 CPU軟核和FPGA及開發(fā)板上的存儲器件,實現(xiàn)了對Xilinx公司的FPGA進行SelectMap配置的一種有效的方案。這種方法減少了外圍器件的數(shù)目,增加了硬件系統(tǒng)地靈活性。此外,該方法除了可以完成FPGA芯片的配置外,更重要的是可以靈活地在線升級系統(tǒng)、修改和調(diào)試FPGA程序。如果存儲空間夠大,可以存儲不同功能的FPGA程序代碼,這樣就可根據(jù)實際情況來加載不同代碼,甚至通過通信接口也可以方便地實現(xiàn)遠程下載代碼和更新系統(tǒng),使整個系統(tǒng)可在線配置,增強了系統(tǒng)的適用性和靈活性。