摘要:文中采用Quartus II開發平臺,基于可編程邏輯器件CPLD" title="CPLD">CPLD設計出多波形信號發生器" title="信號發生器">信號發生器,可輸出頻率、幅度可調的三角波、正弦波和方波。任意波形模塊可由用戶輸出用戶所需的特殊波形,滿足了教學實驗和開發新的實驗項目對特殊波形的要求。整個設計采用VHDL編程實現,其設計過程簡單,極易修改,可移植性強。另外,CPLD還具有可編程重置特性,因而可以方便地更換波形數據,且簡單易行。

關鍵詞:信號發生器:CPLD;D/A轉換" title="D/A轉換">D/A轉換

CPLD復雜可編程邏輯器件,是從PAL和GAL器件發展出來的器件,相對而言規模大,結構復雜,屬于大規模集成電路范圍,是一種用戶可根據需要而自行構造邏輯功能的數字集成電路。各種波形曲線均可以用三角函數方程式來表示,能夠產生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱為函數信號發生器。函數信號發生器在電路實驗和設備檢測中具有十分廣泛的用途。

1 系統設計

1.1 方案比較

方案1:直接頻率合成法

直接頻率合成技術即為用多個晶體分別產生不同頻率的振蕩信號,再經過具有四則運算功能的混頻器、倍頻器、分頻器和不同頻率的濾波器組合而成,用以實現特定頻率信號的產生輸出。

優點:頻率轉換時間短,理論上可產生任意小的頻率間隔。

缺點:由于其利用晶體產生的信號經過運算而成,所以其頻率間隔不能太多;由于采用了大量的倍頻器、分頻器以及混頻器,所以其輸出的波形信號附帶的噪聲較大;并且設備龐大,制造成本較高。

方案2:鎖相頻率合成

利用鎖相環的良好的窄帶跟蹤性能,可使頻率準確的鎖定在參考頻率或其N次諧波上,并使被鎖定頻率具有與參考頻率一致的頻率穩定度和較高的頻率純度。它由基準頻率產生器和鎖相環路兩部分組成。

優點:結構簡單,輸出頻率純度高,易于得到大量的離散頻率。

缺點:瞬時頻率穩定度較差,頻率轉換時間較長。

方案3:直接數字頻率合成技術(DDS)

直接數字頻率合成技術完全擺脫了傳統的頻率合成技術的思路,即是通過對相位的運算來進行頻率合成的,它的主要理論依據是Nyquist抽樣定理對模擬信號進行采樣,經量化后存入存儲器中,再通過尋址查找表輸出波形數據,經DAC及濾波后恢復原波形來實現頻率合成的。

優點:利用DDS頻率合成技術的器件功耗低,體積小,其工作頻率范圍寬,頻率分辨率極高,頻率轉換時間極短。

缺點:由于受限于器件可用的最高時鐘頻率,輸出頻率上限不能太高;由相位量化噪聲和幅度量化噪聲所形成的總輸出噪聲電平很高。

1.2 方案選擇

以上三種頻率合成技術是現代頻率合成技術的基礎,在性能上各有特點,相互之間起到了很好的互補作用。本文綜合三種技術采用的方案為:用CPLD開發板結合D/A芯片輸出模擬信號,實現信號發生器功能。作為信號發生器時,能夠產生三角波、正弦波和方波三種不同的波形,并且可以通過開發板上的按鍵來控制頻率和波幅的調節。

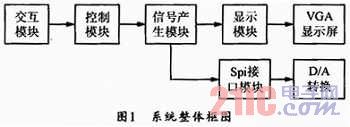

1.3 方案的總體框圖

圖1所示為系統的整體框圖。圖1中,控制模塊包括三個部分:外界輸入、命令分析和輸出指令。信號發生器模塊也包括指令輸入、選擇波形產生和輸出序列三個部分,其中在選擇波形產生中決定選擇波形的程序以及確定頻率和幅度的大小。

2 各模塊功能和實現

2.1 交互模塊

交互模塊的主要功能是按鍵輸入,交互模塊接口電路圖如圖2所示。

2.2 控制模塊

控制模塊的主要功能是接受按鍵信號,控制各模塊輸出數據格式其接口電路圖如圖3所示。

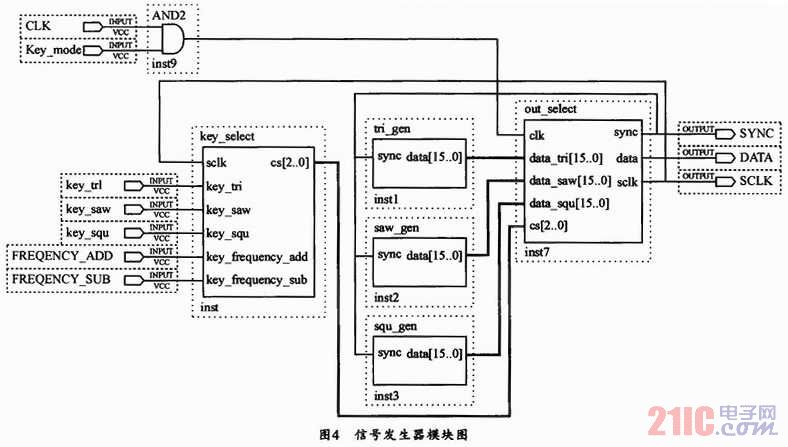

2.3 信號發生器模塊

該模塊實現信號發生器功能,接受控制模塊數據,處理并輸出給D/A芯片,信號發生器模塊接口電路圖如圖4所示。

數據處理模塊將從控制模塊接受到的數據轉化成波形、頻率、波幅信息,并將處理后的數據轉交給數據輸出模塊。

2.4 顯示模塊

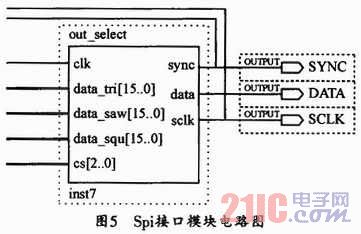

SPI是串行外圍設備接口,SPI接口主要應用在EEPROM、FLASH、實時時鐘、AD轉換器,還有數字信號處理器和數字信號解碼器之間。Spi接口模塊電路圖如圖5所示。

3 結束語

本文介紹了用CPLD開發板結合D/A芯片輸出模擬信號,實現了信號發生器功能。作為信號發生器時,能夠產生三角波、正弦波、鋸齒波和方波四種不同的波形,并可以通過開發板上的按鍵來控制頻率和波幅的調節。本設計通過VGA顯示,用戶界面友好,操作便捷,有較強的實用性。