鎖相環是倍頻電路的主要實現方式,直接決定倍頻的成敗。傳統的鎖相環各個部件都是由模擬電路實現的,隨著數字技術的發展,全數字鎖相環逐步發展起來,全數字鎖相環的環路部件全部數字化,通常由數字鑒相器、數字環路濾波器、壓控振蕩器以及分頻器組成,全數字鎖相環中的分頻器要求模可預置且可根據實際需要進行可逆分頻[2]。由于現有的電路均不能滿足上述要求,本文首先采用simuink 和FPGA 開發了應用于倍頻電路的變模可逆分頻器。

2. 變模可逆分頻器的工作原理

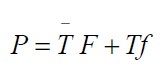

變模分頻器的基本原理是設置一個符合函數,在分頻過程中,觸發器的輸出與預置模比較,當觸發器的輸出與預置模一致時,則給出符合信號,強迫計數器進入所希望的狀態,即初始狀態,隨后計數器則按照卡諾圖確定的程序繼續工作,直到最后一個狀態,即由地址碼確定的第N-1 個狀態,再強迫分頻器回到初始狀態[3]。所以每個觸發器應當受到兩個控制函數的控制,即:

f—正常的由卡諾圖得到的控制函數;

F—強迫分頻器進入的希望狀態;

T—符合函數;

當符合函數T = 1時,F 不起作用,P = f ,分頻器按正常程序分頻;當T = 0,F 起作用,P = F ,強迫分頻器跳變到所希望的狀態。

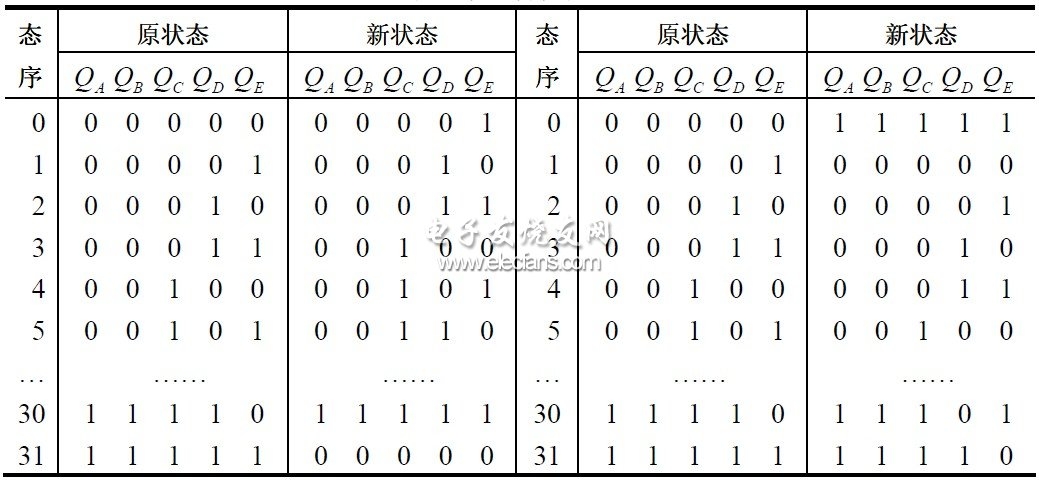

表1 狀態轉換表

(注:表1 為狀態轉換圖,其中左半部分為遞增分頻器狀態轉換表,右半部分為遞減狀態轉換表。表2 為計數值與各觸發器當前值的關系。)

表2 計數值與各觸發器當前值的關系

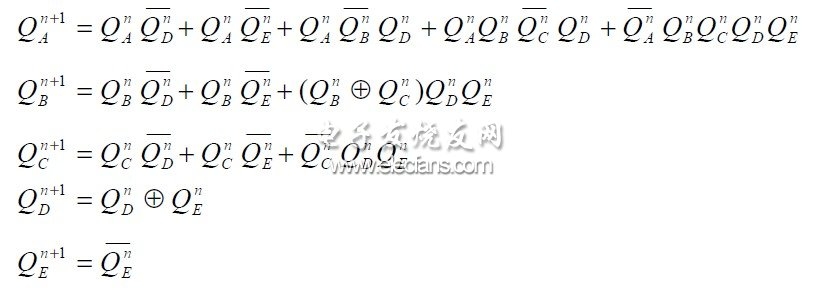

加法分頻器的驅動方程為:

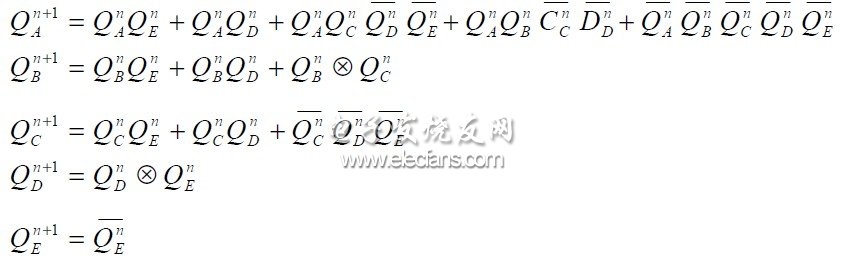

減法分頻器的驅動方程為:

各觸發器還受到可逆信號的控制,當I _ D信號為1時為遞增分頻器,反之為遞減分頻器。

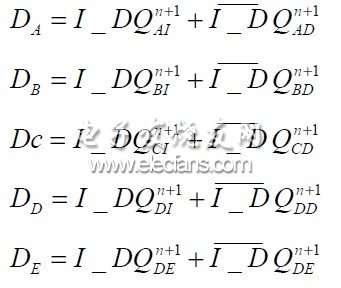

各觸發器的驅動函數為:

3. 基于simulink的可逆分頻器設計

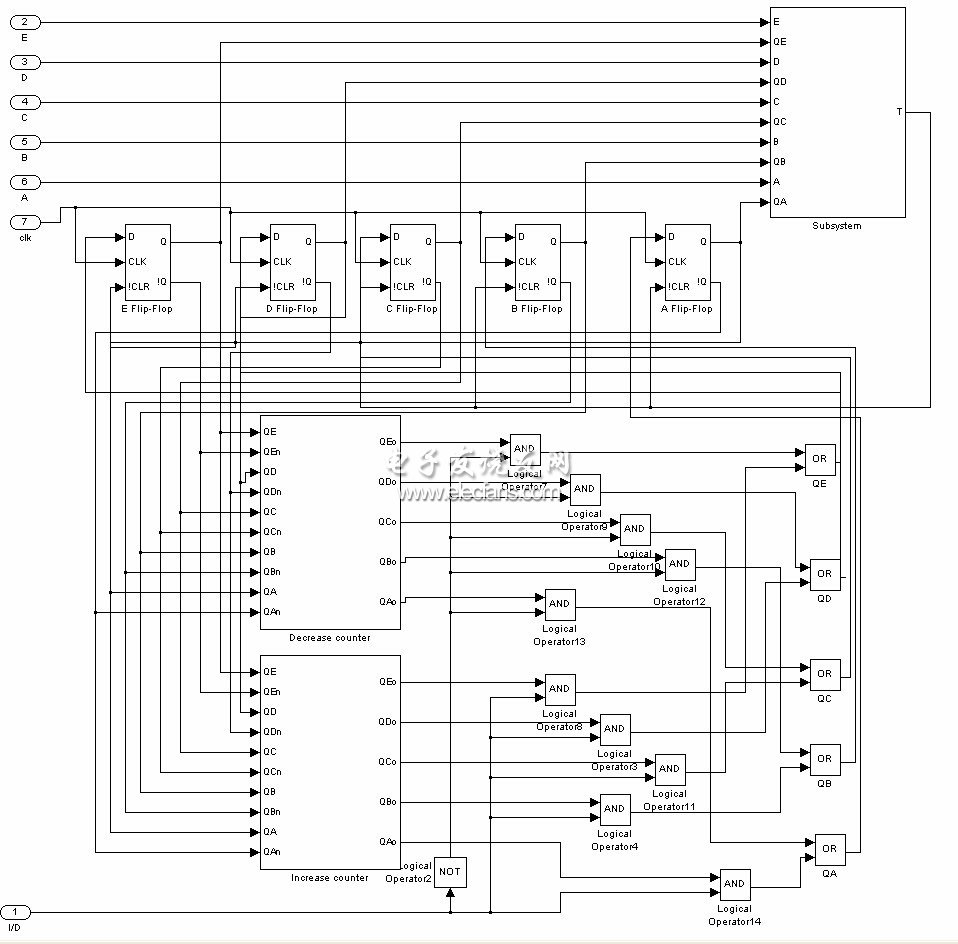

采用simulink 建立可逆分頻器模型,如圖1 所示。分頻器采用五級D 觸發器實現,輔之以必要的控制邏輯。輸入端A、B、C、D、E 為輸入模值,I _ D為1 時分頻器工作在遞增模式,當I _ D為0時分頻器工作在遞減模式,符合函數的輸出T連接至D觸發器的清零端,分頻器的工作波形如圖2 所示。從圖中可以看出分頻器能夠在預置模下完成遞增或遞減分頻器功能。

圖1 五級分頻器

圖2 分頻器的工作波形。

圖3 分頻器的仿真波形。

4. 基于FPGA的可逆分頻器設計

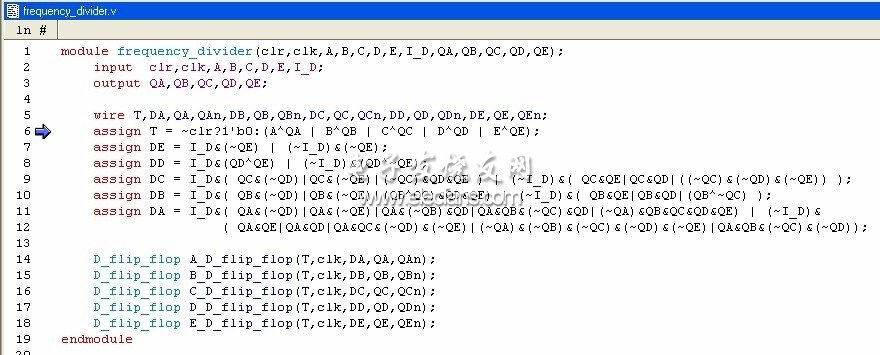

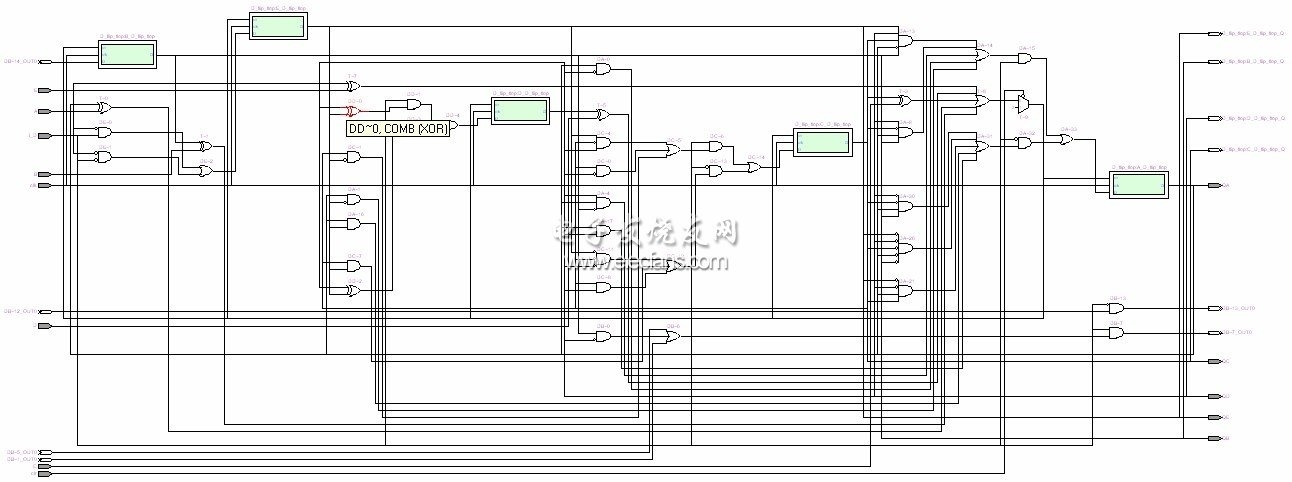

采用verilog 語言實現了可逆分頻器,其仿真波形如圖3 所示,分頻器可完成預置模以及遞增及遞減分頻功能。分頻器的verilog 代碼如圖4 所示,寄存器傳輸級網表如圖5 所示。

圖4 分頻器代碼。

圖5 寄存器傳輸級網表。

5. 總結

本文分析了變模可逆分頻器的工作原理,并分別采用simulink 和FPGA 實現了可逆分頻器。仿真結果表明分頻器能夠完成預置模,遞增和遞減分頻功能,滿足設計要求。