1 引言

生物電信號是由生物體發出的不穩定的微弱電信號,主要包括心電、肌電、腦電信號,其特點表現為信號弱、干擾強、精度高。因此,在生物體的多參數測量中,高精度尤為重要,這對信號采集速率、實時性和準確性等提出更高要求。

根據生物電信號特點,介紹一種基于Ez-USB FX2接口的生物電信號數據采集系統,它將傳統醫學儀器的優點與計算機強大的數據存儲能力以及良好的人機界面相結合,符合醫學儀器數字化、模塊化、小型化的發展趨勢,具有很好的應用前景。

2 EZ-USB FX2接口簡介

高速設備通常具有支持高速傳輸的USB控制器以實現高速傳輸,選用內置增強型微處理器8051、可動態加載固件的USB2.0控制器EZ-USB FX2(CY7C68013),該器件相對于其他USB控制器,功能強大,開發難度較小且性價比較高。

2.1 基本特性

EZ-USB FX2功能強大,既負責USB事務處理,也兼具微處理器的控制功能,可用作USB外設主控器件。該器件集USB2.0收發器、串行接口引擎、增強型 8051、I2C總線以及通用可編程接口于一體,體積小巧,性價比高,廣泛應用于存儲器、打印機、掃描儀等各種USB外設。

2.2 端點緩存

USB規范定義端點作為發送數據的起始點或接收數據的目的地址。EZ-USB FX2包含3個64 B的端點緩沖區和4 KB的可配置端點緩沖區。其中3個64 B的緩沖區分別用于EP0,EPlIN和EP1OUT,而4 KB的可配置緩沖區用于EP2,EP4,EP6和EP8。端點0默認為控制端點,支持OUT和IN雙向傳輸;端點1支持批量、中斷和同步傳輸;而端點2、 4、6和8則是高帶寬的數據傳輸端點,可配置成不同方式以適應不同帶寬要求。

2.3 GPIF接口

EZ-USB FX2系列器件提供3種可用接口模式:端口模式、從屬FIFO模式和GPIF主控制模式。端口模式下,所有I/O引腳都可作為8051的通用I/O接口;從屬FIFO模式下,外部邏輯或外部處理器直接與EZ-USB FX2的端點FIFO相連,外部設備作為控制器,像普通FIFO一樣對EZ-USB FX2中的端點數據緩沖區進行讀寫;而GPIF模式是一種內部主機控制模式,使用內部集成的高效控制邏輯取代外部微控制器來控制Ez-USB FX2端點FIFO。在EZ-USB FX2內部,GPIF內核就是一個可編程的狀態機。

EZ-USB FX2使用4個用戶定義的波形描述符控制狀態機.從而實現FIFO以及單字節數據的讀寫操作。每個GPIF波形描述符都由7段組成:S0~S6。執行完 S0~S6的動作后,進入idle狀態(S7)即空閑狀態,以準備啟動下一次GPIF動作。每個state可定義為無判斷不轉移態(NDP)或判斷轉移態 (DP)。當某個state定義為NDP時,這個state動作的執行只是簡單延時,用于確定產生指定電平的延續時間;當定義為DP時,它將根據 RDY0~RDY5上的輸入信號狀態,以及內部FIFO的可編程標志和內部自定義的Ready標志,將這些信號進行邏輯“與”、“或”、“異或”運算,并根據得到的邏輯結果在S0~S6中選擇一個即將執行的state。執行每個state時,都可指定CTL0~CTL5輸出用戶指定的狀態。通過RDYx和 CTLx以及內部一些標志位的組合,即能完成各種復雜時序電路的控制。由于GPIF接口的配置靈活,使得FX2可方便地和其他邏輯微處理器(例如單片機、 DSP、CPLD和FPGA等)進行數據的主動讀寫,這樣便大大擴展GPIF模式的使用范圍。GPIF模式下,8051可不參與數據傳輸,以突破高速、全速下的傳輸模式進一步接近EZ-USB FX2的傳輸帶寬480 Mb/s。同時根據生物電信號的頻率特征,將每個通道最大采樣頻率設為100 kHz,在GPIF接口模式下完全能夠滿足系統要求。

3 系統結構

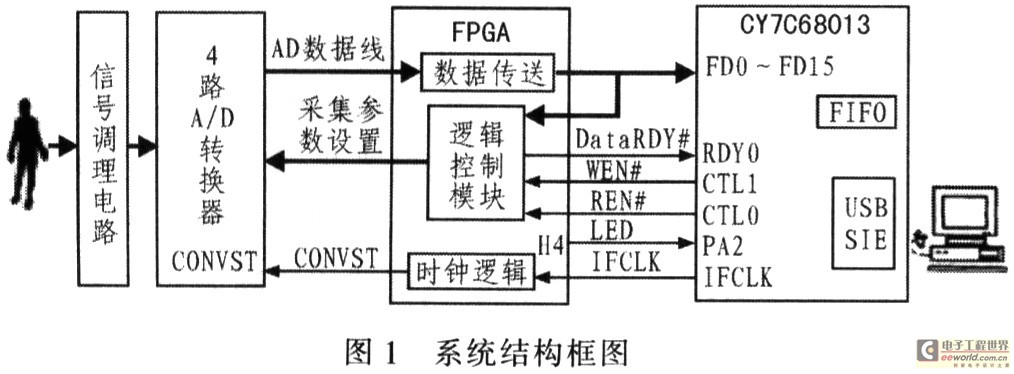

系統結構框架如圖1所示。通過導聯由人體采集到的心電、腦電、肌電等信號調理電路后,由FPGA內部邏輯控制A/D轉換對其采樣。將經采樣并通過A/D轉換后的數據暫時緩存到EZ-USB FX2的內部FIFO中,供PC機讀取。整個系統涉及A/D轉換及其通道選擇、信號放大、FPGA控制和EZ-USBFX2接口設計,這里主要介紹EZ- USB FX2接口設計,以及相應固件程序的開發與GPIF波形設計。

4 器件資源分配

4.1 EZ-USB FX2與FPGA的硬件連接

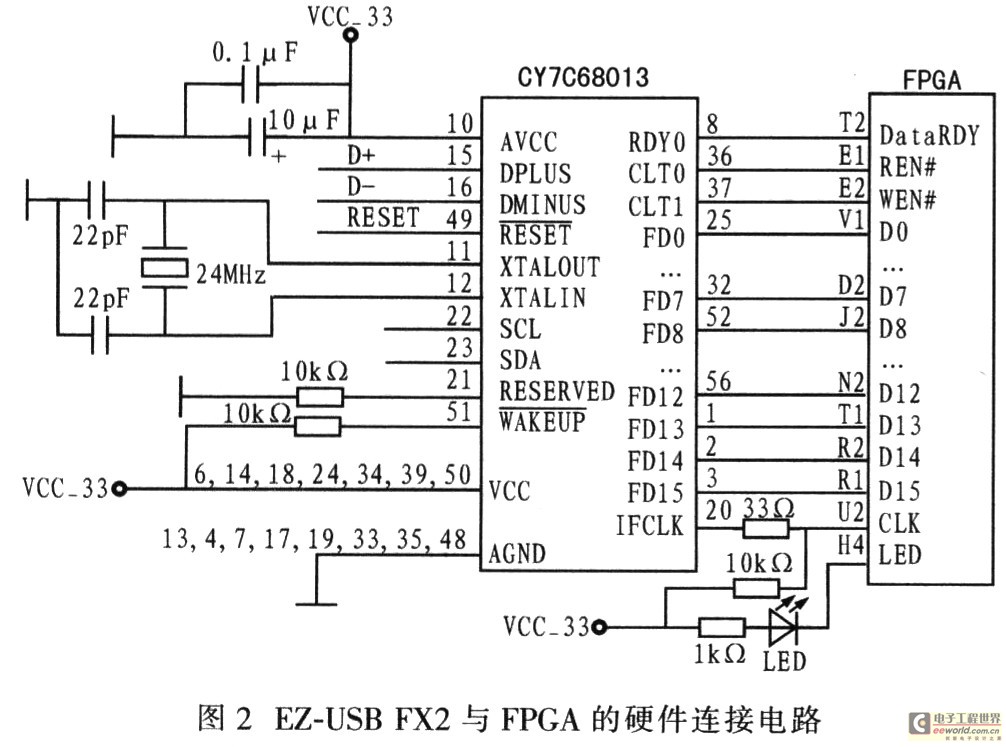

EZ-USB FX2采用GPIF接口和FPGA相連,其硬件連接電路如圖2所示。EZ-USB FX2與FPGA連接的引腳分配如下:FD0~FD15為GPIF雙向數據線,負責讀寫數據:CTL0、CTL1分別為讀(REN#)、寫(WEN#)使能信號;RDY0為FPGA發出的數據準備好信號;PA2與FPGA的H4引腳連接,用于數據采集開始時點亮LED。

4.2 端點分配

系統中數據通道分為數據上傳通道以及配置和控制命令通道,根據設計需要,選擇其中兩個端點分別作為發送和接收端點。配置如下:EP2用于從USB向FPGA傳輸采集控制命令,4×512字節緩沖,傳輸類型為批量OUT傳輸方式;EP6用于從 FPGA向USB傳輸數據采集結果,4×512字節緩沖,傳輸類型為批量IN傳輸方式。EZ-USB FX2相當于一個中轉站,一方面將FPGA發來的采集數據傳輸給主機,另一方面將主機發送的數據采集參數傳輸至FPGA,便于控制A/D轉換。

5 固件程序設計

固件是設備運行的核心,其主要功能是控制EZ-USB FX2處理驅動程序請求(如請求設備描述符、請求或設置設備狀態及設備接口等USB2.0標準請求)、向FPGA發送采集參數、通過EZ-USB FX2緩存數據并實時上傳至PC等。

本系統中,即使使用外部邏輯和內置通用可編程接口,在沒有CPU的干涉下能夠通過4個端點FIFO處理高速帶寬數據,固件還需器件初始化、GPIF波形初始化、控制和監測GPIF的動作。

5.1 器件初始化

同件初始化函數為TD_Init(),主要負責對EZ-USB FX2的初始化,在同件開始運行時調用該甬數。其初始化工作主要分為以下步驟:

(1)設置EZ-USB FX2的IFCLK輸出頻率,將時鐘頻率設置為內部時鐘48 MHz;

(2)設置EZ-USB FX2的EP2為BULK、OUT傳輸方式,EP6為BULK、IN傳輸方式,均為4倍緩沖;

(3)復位EP2 FIFO并設置為Auto OUT模式,復位EP6FIFO并設置為Auto IN模式;

(4)調用GpifInit()函數,初始化GPIF所需的寄存器;對EP2OUT、GPIF使用EF標志,對EP6IN,GPIF使用FF標志;

(5)初始化PA2為輸出引腳并置為低電平,高電平時點亮LED。

5.2 GPIF波形設計

EZ-USB FX2固件程序可指定某個波形為4個端點中的任意一個工作,GPIF將在接口產生使能信號和握手信號,將數據送入或送出端點FIFO。在本系統中,對 FPGA寫命令時則通過FIFO Write實現;讀取所采集到的數據時,則通過FI-FO Read實現。波形設計如下:

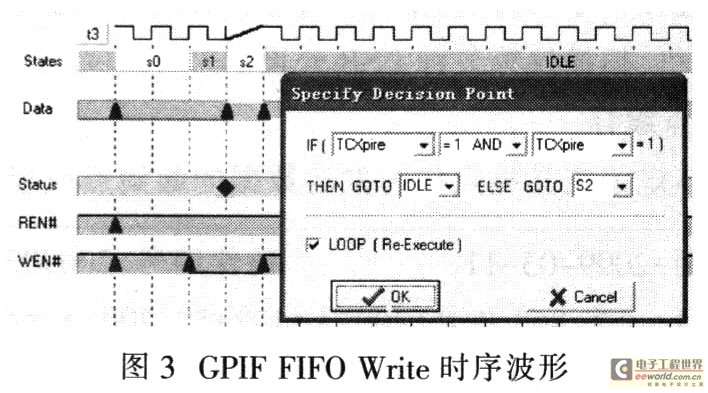

(1)圖3為FIFO Write時序波形,用于向FPGA發送采集控制參數。S0為非活動狀態,當WEN#置低時跳入S1狀態,S2設為Next FIFO Data,依次將數據寫入FPGA的寄存器中。

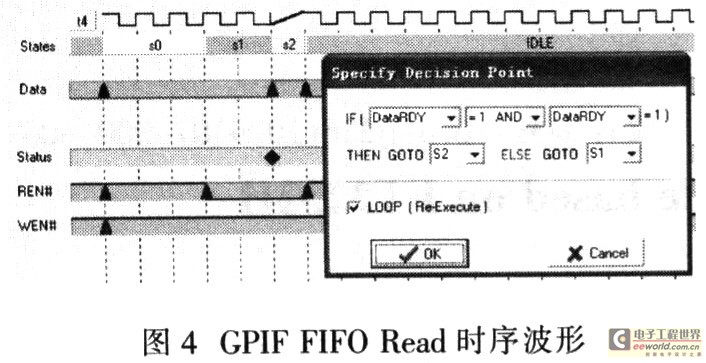

(2)圖4為FIFO Read時序波形,它描述了采集數據的讀傳輸,S0為非活動狀態,S1為讀操作的引導狀態并將REN#置低。當接收到FPGA發送的DataRDY=1 后,跳入S2。將S2設為FlowState,邏輯控制數據從FPGA中讀出并操作REN#的狀態,即當Tcxpire=1時,將REN#置高,跳入 IDIE狀態。在FlowState狀態下,WEN#置高,寫使能關閉。

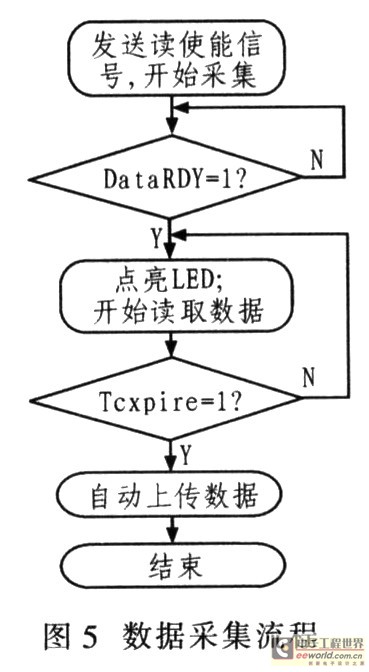

5.3 數據采集流程

程序開始,主函數調用TD_Init()和Gpiflnit()函數,初始化寄存器,并通過2個自動指針寄存器AUTOPTR1和AU-TOPTR2,把生成的GPIF波形程序調入器件的RAM,然后狀態機開始運行,產生所設計的控制波形。采集參數下傳后,FPGA解析參數,延時,EZ-USB FX2向FPGA發送讀使能信號,開始采集數據,數據采集程序流程如圖5所示。如果FP-GA返回DataRDY=1,在TD_Poll()函數中執行讀取數據傳輸程序。完成該過程后,程序根據主機請求,開始自動上傳數據。

6 結束語

基于FPGA控制電路、EZ-USB FX2高速傳輸的數據采集系統,可同時采集16位生物電信號;EZ-USB FX2采用GPIF接口模式,8051可不參與數據傳輸,以突破高速、全速下的傳輸模式,解決了外圍設備和EZ-USB FX2接口之間存在的傳輸瓶頸問題:同時A/D轉換脫離了EZ-USB FX2,而由FPGA完全控制,避免了直接上傳時的數據丟失。該系統設計具有結構簡單、數據不丟失且傳輸速率高等優點,因此在生物電信號數據采集中具有良好的實用價值和應用前景。