摘要:出租車計費器一般采用以單片機為核心的設(shè)計方法,設(shè)計不夠靈活方便。為此,在此介紹了采用EDA技術(shù)的層次化設(shè)計方法設(shè)計出租車計費器的方法。即用VHDL編寫各個功能模塊,實現(xiàn)低層設(shè)計;用原理圖輸入方式描述各模塊間的關(guān)系,實現(xiàn)頂層設(shè)計。采用FPGA可編程邏輯器件為系統(tǒng)控制單元,無需添加外圍電路,更新功能僅需修改軟件。實驗表明,該設(shè)計方法簡單快捷,所設(shè)計的系統(tǒng)性能可靠。應(yīng)用該方法設(shè)計的數(shù)字電子系統(tǒng)具有很強的靈活性。

關(guān)鍵詞:EDA;VHDL;層次化;出租車計費器

0 引言

EDA使用戶在無需實際芯片、電路板和儀器儀表的情況下進行電路設(shè)計和分析;采用在系統(tǒng)編程技術(shù),在現(xiàn)場對系統(tǒng)進行邏輯重構(gòu)和升級,實現(xiàn)硬件設(shè)計軟件化。

EDA技術(shù)以可編程邏輯器件FPGA和CPLD及其開發(fā)系統(tǒng)為硬件平臺,以EDA開發(fā)軟件如Max+PlusⅡ為開發(fā)工具,基于邏輯功能模塊的層次化設(shè)計方法設(shè)計數(shù)字系統(tǒng)。Max+PlusⅡ設(shè)計可采用原理圖、硬件描述語言(VHDL)等多種輸入方式,并支持這些文件的任意混合設(shè)計。對于不同層次,可采用不同的輸入方式進行設(shè)計。由于VHDL擅長描述模塊的邏輯功能,所以在對底層模塊設(shè)計中,常采用VHDL進行描述,而原理圖則擅長描述模塊間的連接關(guān)系,故在頂層設(shè)計中,常采用原理圖輸入方法。出租車計費器通常以單片機為核心進行設(shè)計,本文以為它例介紹基于EDA技術(shù)的數(shù)字系統(tǒng)混合設(shè)計方法。

1 出租車計費器功能

出租車計費器的功能要求:

(1)實現(xiàn)出租車按行駛里程收費,起步費為7.0元;

(2)行駛3 km后再按2元/km計費,車停時不計費;

(3)能預(yù)置起步費和每公里收費,并能模擬汽車啟動、停止、車速等狀態(tài)。

根據(jù)VHDL特點,設(shè)計者不再需要考慮選擇固定功能的標(biāo)準(zhǔn)芯片,而是從實現(xiàn)系統(tǒng)功能與性能出發(fā)來,建立出租車計費器系統(tǒng)模塊,如圖1所示。

2 出租車計費器的設(shè)計與實現(xiàn)

本系統(tǒng)分底層和頂層2個層次設(shè)計,底層設(shè)計采用VHDL編寫各個功能模塊,頂層設(shè)計采用原理圖方式描述各模塊間的連接。

2.1 底層文件的設(shè)計

底層模塊包括:出租車車速控制模塊;計費器里程計數(shù)模塊;計費器計費計數(shù)模塊3個模塊。

以出租車車速控制模塊為例介紹。

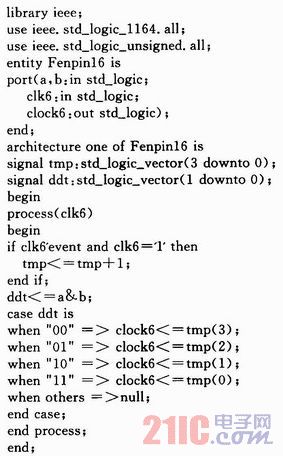

出租車車速控制模塊用于控制出租車的車速。圖1中,當(dāng)起/停開關(guān)及清零信號RESET都為“1”時,汽車啟動就開始進入里程計數(shù)和計費器工作狀態(tài)。通過改變“車速選擇”端的輸入值可以控制汽車行駛快慢。用CLK6作為車速控制模塊的時鐘輸入,CLOCK6作為輸出,用A、B作為車速選擇變量,分別取值從“00”→“01”→“10”→“11”時,車速越來越塊。其VHDL程序代碼如下:

以上程序代碼經(jīng)過編譯后生成相應(yīng)模塊符號,如圖2所示,供頂層設(shè)計時調(diào)用。

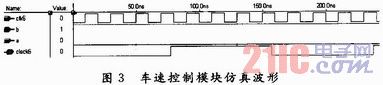

程序經(jīng)過時序仿真后的波形,如圖3所示。

2.2 頂層原理圖設(shè)計

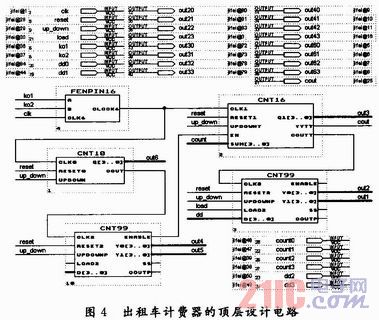

頂層設(shè)計采用原理圖輸入方式。通過調(diào)用生成的各模塊符號,并將它們作適當(dāng)連接以實現(xiàn)頂層文件的設(shè)計。出租車計費器的頂層設(shè)計電路,如圖4所示。

圖4中,ko1,ko2為車速控制開關(guān);clk為時鐘信號;reset為復(fù)位信號;up_down為起/停控制信號;count為預(yù)置每公里收費的信號;load為預(yù)置使能信號;dd為預(yù)置起步費信號;out5,out4為記錄里程的整數(shù)位;out6為記錄里程的小數(shù)位;outl,out2為記錄費用的整數(shù)位;out3為記錄費用的小數(shù)位。

2.3 頂層文件仿真與下載

頂層原理圖經(jīng)過編譯后生成頂層文件,對頂層文件進行仿真,結(jié)果正確后,利用Altera公司的FPGA芯片EPF10K3LC84—3及其SE-5M型開發(fā)系統(tǒng)進行下載。下載結(jié)果顯示,所設(shè)計的出租車計費器完全符合設(shè)計要求。

3 結(jié)語

由上述設(shè)計實例可見,采用EDA技術(shù)設(shè)計數(shù)字系統(tǒng)則是一種基于邏輯功能模塊的“自上而下”層次化設(shè)計方法。即從整個系統(tǒng)功能與性能優(yōu)化出發(fā),將系統(tǒng)分解為各功能模塊,由VHDL描述模塊的邏輯功能,生成滿足相應(yīng)邏輯功能的新器件,實現(xiàn)底層設(shè)計;再采用原理圖輸入方式,將生成的新器件連成系統(tǒng)圖,實現(xiàn)頂層設(shè)計。另外,由于新器件內(nèi)部電路是用程序構(gòu)建的,硬件的邏輯關(guān)系由語言來描述,所以只要修改語句則可修改硬件的邏輯關(guān)系。由此可見這種設(shè)計方法,可大大提高工作效率,設(shè)計更加靈活、快捷,可減少器件的數(shù)量,避免復(fù)雜的接線,縮小系統(tǒng)的體積,降低消耗,提高系統(tǒng)的可靠性、繼承性、移植性。