隨著計算機技術、網絡通信技術的進步,組建分布式網絡化測試系統,提高測試效率、共享信息資源,已成為現代測試系統發展的方向。分布式測試系統通過網絡等通信媒介把分布于各測試點、獨立完成特定功能的測試設備連接起來,以達到測試資源共享和協同工作等目的。時鐘同步是分布式系統的核心技術之一,其目的是維護一個全局一致的物理或邏輯時鐘,使得系統內各個節點中與時間有關的信息、事件及行為有一個全局一致的解釋。IEEE1588精確時鐘協議是當前分布式測試系統中時鐘同步研究的熱點。采用硬件支持的IEEE1588協議能夠在以太網中不同結點之間實現納秒級的時鐘同步,為工廠自動化、測試和測量以及通信等領域需要高精度時鐘同步的應用提供了一種有效的解決方案。本文采用具有IEEE1588精確時鐘協議硬件支持功能DP83640芯片在基于ARM和WinCE的嵌入式系統平臺上實現IEEE1588協議,為基于嵌入式系統的智能測試儀器組成分布式測試系統奠定了基礎。

1 IEEE1588協議原理

IEEE1588的全稱是“網絡測量和控制系統的精密時鐘同步協議標準”,簡稱精確時鐘協議(Precision Time Protocol,PIP)。IEEE1588協議是通用的提升網絡系統定時同步能力的規范,在起草過程中主要參考以太網來編制,使分布式通信網絡能夠具有嚴格的定時同步,并且應用于工業自動化系統。基本構思是通過硬件和軟件將網絡設備(客戶機)的內時鐘與主控機的主時鐘實現同步,提供同步建立時間小于10μs的運用,與未執行IEEE1588協議的以太網延遲時間1000μs相比,整個網絡的定時同步指標有顯著的改善。

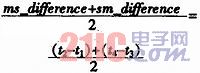

IEEE1588時鐘協議在進行時鐘同步時,主時鐘設備按照一定的時間間隔(一般為2 s)周期性地以廣播方式發送同步報文(Sync)和同步跟隨報文(FollowUp),且在FollowUp報文中記錄Sync報文的發送時間戳t1,而從時鐘設備接收Syne報文記錄接收時間戳為t2;然后,從時鐘設備節點定期發送延遲請求報文(Delay_Req)(一般4~60 s發送一次),并記錄其發送時間戳t3,主時鐘設備接收判延遲請求后,記錄接收時間戳t4,并給相應從節點發送延遲請求響應報文(Delay_Resp),該報文信息中包古時間戳t4。通過得到的4個時間戳,可以計算出主從時鐘之間的偏移量Toffset和網絡傳輸的線路延遲ms_delay,其過程如圖1所示。

得到了從時鐘與主時鐘之間的時間偏移值,就可以采用適當的調節算法來調節從時鐘,最終使得從時鐘與主時鐘同步。從時鐘并不是每個同步周期都需要進行時間同步,而是根據從時鐘與主時鐘之間的時間偏移值等時間信息來決定是否需要進行時間同步。當主從時鐘之間建立起穩定的同步關系后,從時鐘還需周期性地監聽來自主時鐘發布的Sync報文,一旦出現主從時鐘之間不處于時間同步的狀態,就重新進行上述的時間同步過程,直到重新達到主從時鐘之間的時間同步。

IEEE1588協議的運行是由時間戳驅動的,時鐘同步精度主要歸結為時間戳的定時精度。IEEE1588使用UDP協議發送網絡同步報文,基于UDP協議傳輸的過程都是在TCP/IP協議模型下進行數據包的逐層封裝和傳遞的。要使時鐘獲得的報文發送時間和報文接收時間相對精確、穩定,且把發送延遲和接收延遲不相等這種因素對計算傳播延遲產生的影響減小到最低,最好的解決辦法就是在TCP/IP協議棧的底層即物理層對同步報文標記時間戳,標記時間戳的操作越接近物理層,計算得到的主從時鐘的時間偏移量和傳播線路延遲就越準確。要實現這一目的就必須加入專門的硬件設備。美國國家半導體公司(National Semiconductor)推出的DP83640芯片就是一款集成IEEE1588精確時鐘協議硬件支持功能的以太網收發器。芯片內置高精度IEEE1588時鐘,并具有由硬件執行的時間戳標記功能,可為接收及發送信息包加入時間標記。采用DP83640的同步系統,可獲得納秒級的同步精度。

2 硬件設計

由于IEEE1588協議運行于以太網,在基于ARM的嵌入式系統上采用DP83640芯片移植IEEE1588協議的硬件基確是為系統增加以太網接口電路。以太網接口電路主要由媒體訪問控制(Medium Access Control,MAC)器和物理層(Physical Layer,PHY)收發器兩部分構成。MAC控制器芯片實現OSI模型數據鏈路層的功能,提供尋址機構、數據幀的構建、數據差錯檢查、傳送控制、向網絡層提供標準的數據接口等功能。PHY芯片實現OSI模型物理層的功能,定義了數據傳送與接收所需要的電與光信號、線路狀態、時鐘基準、數據編碼和電路等,并向數據鏈路層設備提供標準接口。ARM處理器、MAC芯片與PHY芯片三者之間的關系是MAC芯片向上通過其處理器接口(Processor Interface)與ARM處理器的高級外設總線(APB)連接,向下通過其媒體獨立接口(Media Independent Interface,MII)接口與PHY芯片連接。最終,PHY芯片與RJ45接口連接。

本文使用SAMSUNG公司的S3C2440A型ARM處理器,其內部設有集成MAC控制器,而DP83640芯片只是PHY收發器,因此二者之間還需要增加MAC芯片。由于目前常用的以太網控制器都集成了MAC控制器和PHY收發器,這里選用DAVICOM公司的DM9000以太網芯片,其特點是:具有MII接口可以和片外PHY芯片連接;寄存器操作簡單有效;成本低廉。

實現S3C2440A與DM9000連接,必須對兩者間的數據、地址、控制三大總線進行連接和轉換,其連接關系如圖2所示。

S3C2440A的數據線D[15:0]與DM9000的地址、數據復用數據線SD[15:0]連接用來實現S3C2440A與DM9000之間的數據傳輸。芯片選擇信號AEN與S3C2440A的片選使能信號nGSC4連接,當訪問0x20000000-0x27FF FFFF這個范圍的地址時會激活片選使能信號nGCS4。DM9000默認I/O基地址為300H。CMD引腳用于設置COMMAND模式,與S3C2440A的ADDR2連接CMD為高電平時,選擇數據端口。CMD為低電平時,選地址端口。數據端口和地址端口的地址碼由下式決定:

DM9000地址端口=高位片選地址+300H+0H

DM9000數據端口=高位片選地址+300H+4H

高位片選地址由S3C2440A芯片的nGCS4提供,即為:0x20000000。因此DM9000的地址IO基址為0x20000000,數據IO基址為0x2000 0004。向地址IO寫數據時不會激活ADDR2,CMD為低電平,所以向DM9000傳送的數據為地址,而向數據IO寫數據時會激活ADDR2,CMD為高電平,向DM9000傳送的數據為數據。S3C2440的輸出使能引腳nOE連接DM9000的讀引腳IOR,寫使能引腳nWE連接DM9000的寫引腳IOW。DM9000的中斷請求引腳INT連接S3C2440的外部中斷請求引腳EINT7,使得S3C2440A能夠響應DM9000的中斷。

DM9000與DP83640之間通過標準MII接口連接,RXD[3:0]為接收數據線,TXD[3.0]為發送數據線,CRS為載波檢測信號,COL為沖突檢測信號,RX_DV為數據有效信號,RX_ER為接收錯誤信號,RX_CLK為接收時鐘信號,TX_CLK為發送時鐘信號,TX_EN為發送使能信號,MDIO是管理數據的輸入輸出雙向接口,MDC為管理數據接口提供時鐘信號。需要注意的是DM9000默認使用片內PHY,因此在驅動程序初始化DM9000時,必須主動置位網絡控制寄存器NCR的EXT_PHY位以選擇使用片外PHY即DP83640。

3 軟件設計

軟件設計分為兩個步驟:1)是基于DM9000和DP83640進行以太網通信的驅動程序設計;2)是通過DP83640進行時鐘同步的應用程序設計。

本文使用WinCE5.0操作系統,WinCE5.0系統下網絡驅動程序的編寫必須符合網絡驅動接口規范NDIS(Network Driver Interface Stan dard)。NDIS的層次結構如圖3所示,其中最上層的Winsock是提供給應用層的接口。NDIS位于協議驅動層下面,硬件驅動Miniport Driver之上。協議驅動層通過調用NDIS封裝的接口函數,實現與底層硬件驅動的交互。WinCE下網絡驅動程序的設計主要是在NDIS構架下,針對實際的硬件編寫代碼,實現相應的中間層Miniport Driver接口函數。其主要完成的功能有:DM9000與DP83640的初始化;網絡數據包的發送;網絡數據的接收和中斷。

實現了以太網通信的驅動程序的基礎上,用于時鐘同步功能的應用程序通過UDP協議發送、接收時鐘同步報文,并進行加入、提取和解析時間戳等操作,這些操作通過讀寫DP83640內部的1588基本寄存器組(PTP 1588 BASEREGISTERS)和1588配置寄存器組(PIP 1588CONFIGURATION REGISTERS)完成。

4 結論

IEEE1588協議通過在以太網上發送和接收同步報文來實現時鐘同步,同步的精度取決于記錄報文發送和接收時間的時間戳的精度,因此要實現高精度的時鐘同步必須通過硬件支持在通信協議的底層加入和提取時間戳。本文通過在ARM-WinCE嵌入式系統平臺上設計了使用DP836 40芯片作為PHY收發器的以太網接口電路及其驅動程序,實現了IEEE1588協議在ARM-WinCE平臺上的移植,并達到了不低于1 μs的同步精度,為基于ARM-WinCE平臺的測試儀器組建分布式測試系統奠定了基礎。