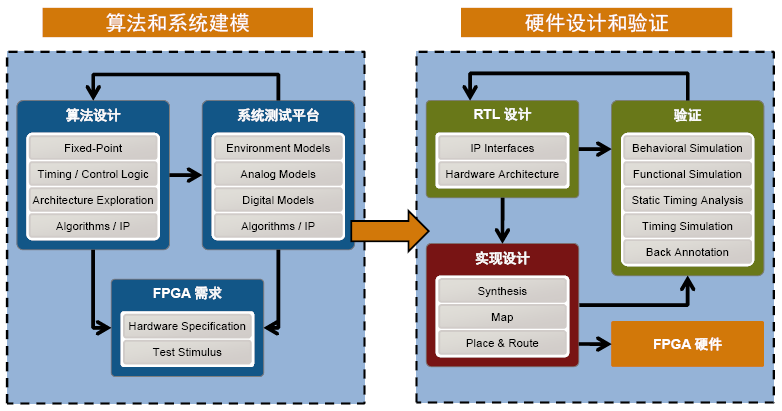

了解系統設計流程的人員都知道,從系統建模到硬件實現的過程是一個設計復雜、需要不斷測試與不斷調整的迭代過程。作為上層的系統設計工程師,他們側重于系統本身的性能,關注整個系統的算法設計與系統建模,而非過多得考慮系統的可實現性。但對于硬件工程師來說就不一樣了,他們更側重于整個系統的硬件實現,即在給定指標的情況下將系統以硬件的形式呈現出來,而不去考慮系統性能如何。

正是因為這兩類工程師的側重點不一樣,使用的工具不一樣,開發流程也是不同的,這就造成了兩個環節之間存在巨大的鴻溝。需要浪費大量的時間去迭代,完成設計驗證與設計測試。這個過程中還可能需要通過另外一套完全不一樣的工具來進行溝通。這種方式使得我們設計或調試一個簡單的系統時,可能需要幾個星期甚至幾個月的時間完成一次迭代。

圖1 從系統建模到硬件實現的簡化流程

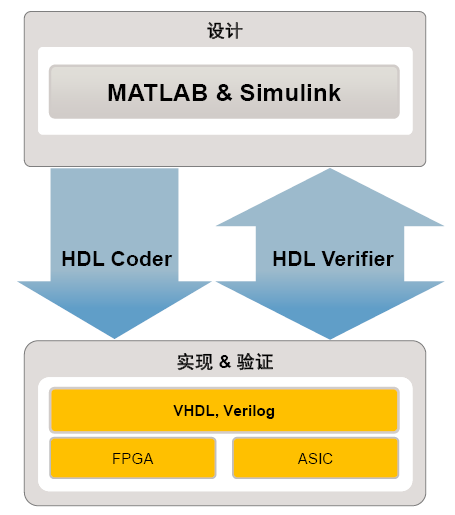

而今年春天Mathworks公司推出的2012a(R2012a) 版 MATLAB 和Simulink 產品系列幫助設計者解決了這一難題。新版本的 MATLAB 和Simulink引進了HDL Coder,可以從MATLAB 或Simulink中 自動生成HDL 代碼,用于FPGA 或 ASIC 上的原型設計和實現;此外,還發布了HDL Verifier,用來取代EDA Simulator Link 并增加Altera FPGA 硬件在環支持。有了這兩個產品,MathWorks 現在可提供利用MATLAB 和Simulink 進行HDL 代碼生成和驗證的能力。R2012a 還更新了84 種其它產品,包括Polyspace 嵌入式軟件驗證產品。

HDL Coder 利用MATLAB 功能和Simulink 模型生成可移植和可綜合的VHDL 和Verilog 代碼,可用于FPGA 編程或ASIC 原型開發和設計。因此,工程師隊伍再也不用手動編寫HDL 代碼,也不再需要手寫HDL測試平臺了。就可以立即識別出針對硬件實現的最佳算法。Simulink 模型和所生成HDL 代碼之間的可追溯性同時也支持開發遵循DO-254 和其他標準的高完整性應用程序。

這款工具的發布,跨越了系統設計與硬件設計鴻溝。幫助系統工程師在設計的初期考慮更多硬件實現因素,從而使得系統設計更加貼近可實踐性。幫助硬件工程師加深對系統全局的理解,真正將精力放在關鍵之處。它不僅降低了系統設計復雜度、縮短了設計周期,提高了設計效率,還對設計中的一些環節進行了優化,例如浮點到定點的自動轉換、算法和HDL之間的可追溯性、HDL資源優化和報告等。

圖2 HDL Coder 為FPGA和ASIC設計生成VHDL和Verilog代碼

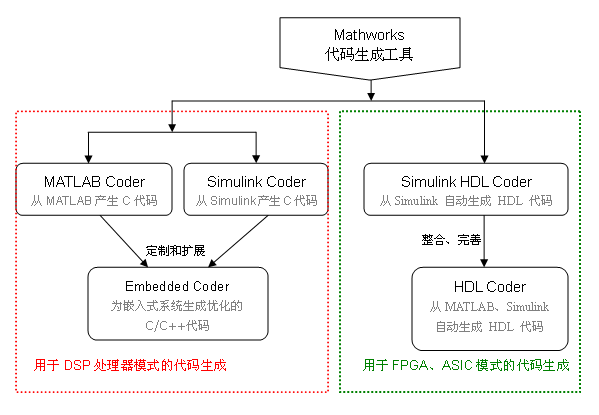

題外話:Mathwork代碼生成類工具族譜

HDL Coder與之前的Simulink Coder、MATLAB Coder、Embedded Coder和HDL Coder共同構成了Mathworks代碼生成類工具系列。現在我們把集中工具所針對的不同應用領域做一個歸納。

更多信息