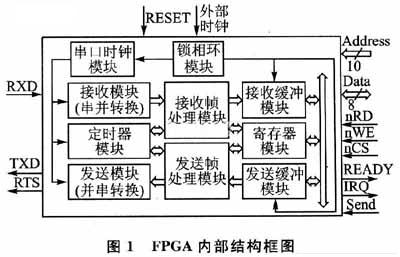

FPGA和ARM的Profibus-DP主站通信平臺設計

孫倩華,滿慶豐,夏繼強 北京航空航天大學

摘要: 提出一個使用FPGA和ARM微控制器實現Profibus-DP主站(1類)通信平臺的解決方案;解析了Profibus-DP通信協議,重點是令牌輪轉協議;給出了該主站通信平臺的系統構建。該通信平臺可以獨立實現Profibus-DP主站(1類)與其他主站(1類和2類)的令牌傳遞的主主通信功能,以及其與從站的主從通信功能。

Abstract:

Key words :

摘要:提出一個使用FPGA和ARM微控制器實現Profibus-DP主站(1類)通信平臺的解決方案;解析了Profibus-DP通信協議,重點是令牌輪轉協議;給出了該主站通信平臺的系統構建。該通信平臺可以獨立實現Profibus-DP主站(1類)與其他主站(1類和2類)的令牌傳遞的主主通信功能,以及其與從站的主從通信功能。

Profibus-DP是由西門子公司推出的一種開放式現場總線標準,用于現場級分布式自動化外設之間的高速數據傳輸。Profibus在2007年4月突破2000萬節點大關。據PI(世界性的現場總線Profibus用戶組織)稱現在已經超過2 500萬個節點,并希望在2012年突破5 000萬個節點,年銷售芯片450萬個。

目前國內業界對于Profibus-DP的研究和相關產品的開發都是基于國外提供的專用協議芯片(主站多數采用西門子推出的ASPC2,從站多采用SPC3等智能通信芯片),而沒有協議芯片樣機開發的相關報道。對于主站的開發,國內一些科研院所(北航706教研室、中科院、浙大等)也曾利用可編程邏輯器件配合MCU設計出簡單主站的試驗產品,但是這些產品僅能實現單主站的功能,對于組成強大的Profibu-DP網絡還望塵莫及。為了打破國外芯片的壟斷,推動國內相關芯片及產品的開發,本文提出了一種FPGA與ARM相結合的方式解決Profibu-DP 1類主站的主主通信及主從通信問題,實現了比較完整的主站研制方案。

1 Profibus-DP主站通信機理及技術特性

1.1 Profibus-DP主站通信協議

Profibus協議的結構以OSI為參考模型,DP使用第1層、第2層和用戶接口,第3層到第7層未加以描述。一個DP系統既可以是一個單主站結構,也可以是一個多主站結構,本文涉及的是多主站結構。多主站結構使用混合的總線訪問控制機制,主站之間采取令牌控制方式;令牌在主站之間傳遞,擁有令牌的主站擁有總線訪問控制權;主站與從站之間采取主從的控制方式。

令牌是一種特殊的報文,如下所示:

SD DA SA

SD為開始分界符,DA為目的地址,SA為源地址。令牌環是所有主站的組織鏈,按照主站的地址構成邏輯環。在這個環中,令牌在規定的時間內按照地址的升序在各主站間依次傳遞,用戶通過編寫令牌傳遞程序保證每個主站在一個確切規定的時問內得到令牌,之后該主站就可以在規定的時間內與所屬從站通信,也可與所有主站通信。其中主站與所屬從站間的數據通信由主站按已確定的循環順序自動地進行處理。

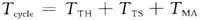

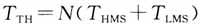

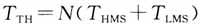

1.2 令牌循環時間分析

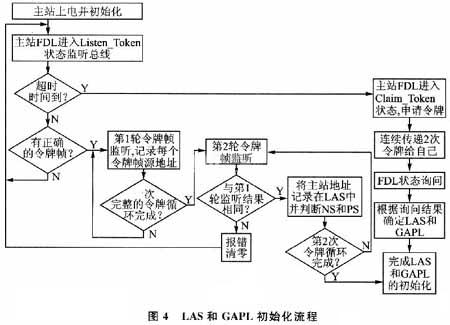

最壞情況下令牌循環時間為:

其中,TTH為站點令牌保持時間,TTS為令牌的整體傳輸延遲,TMA為令牌維護時間。在不考慮出錯重發的前提下,N個主站令牌的整體傳輸延遲TTS=N·TTK,TTk是發送令牌PDU(協議數據單元)需要的時間。高優先級報文的傳送時間為THMS,報文數量為M;低優先級報文的傳送時間為TLMS,報文數量為L。假設所有站點的報文服務均含有應答,則 代入上述公式可得:

代入上述公式可得:

代入上述公式可得:

代入上述公式可得:

2.2 ARM控制器部分程序設計

ARM控制器程序對應于Profibus通信協議數據鏈路層之上的DDLM直接數據鏈路映射程序、主站通信狀態機、應用層數據接口及應用層。

本設計對Profibus-DP協議按層次封裝為函數,層層調用。

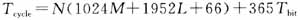

2.2.1 Slave_Handler狀態機

Slave_Handler狀態機功能塊負責實現主從通信功能,根據從站狀態做出相應處理,有固定的處理次序,每次調用Slave_Handler狀態機產生一個DDLM請求,從而控制從站進入相應的通信狀態。Slave_Handler狀態轉換圖如圖2所示。

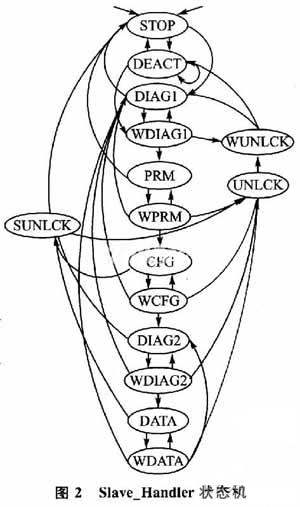

2.2.2 Scheduler和FDL_Controller狀態機

Scheduler狀態機功能塊負責實現對Slave_Handler狀態機的控制。它向Slave_Handler狀態機發送從站輪詢控制信號,控制其逐步與從站建立數據交換關系。

FDL_Controller狀態機由10個FDL狀態組成并在這些狀態間轉換,如圖3所示。

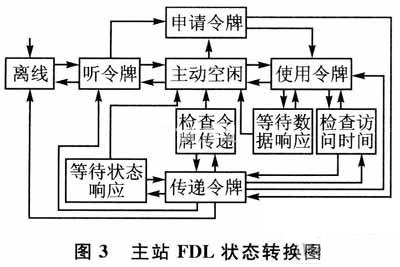

邏輯令牌環的建立主要工作是對LAS和GAPL的初始化。LAS和GAPL的具體初始化流程如圖4所示。

LAS的形成標志著邏輯令牌環初始化的完成。接下來就是邏輯令牌環運轉的維護階段,令牌將按照LAS進行循環傳遞,得到令牌的主站有權進行對其所屬從站的輪詢。傳遞過程中主站將以固定的時間間隔,通過Request FDLStatus主動幀來詢問自己GAP范圍內的所有地址,并根據詢問結果修改LAS和GAPL。在主站活動表生成之后,前驅站詢問ReqtJest FDL Starus,主站回復準備進入邏輯令牌環,并從Listen_Token狀態進入Active_Idle狀態(主站的前驅站會修改自己的GAP和LAS,并把該主站作為自己的后繼站)。主站在Active_Idle狀態*總線,能夠對尋址自己的主動幀作應答,但沒有發起總線活動的權力,直到前驅站傳送令牌給它,它保留令牌并進入Use_Token狀態,在此狀態下驅動Scheduler狀態機工作。主站持有令牌后,首先計算上次令牌獲得時刻到本次令牌獲得時刻經過的時間(即實際輪轉時間tRR),并與用戶設定的目標輪轉時間tTR比較,如果tRR小于tTR,則主站開始處理傳輸任務。首先處理高優先級傳輸服務,所有高優先級服務處理完畢后處理低優先級服務。在這個過程中,每一個完整的報文循環之后,主站就重新計算tTR—tTH。若結果小于0,主站進入PassToken狀態,將令牌傳遞給后繼站,未完成的任務留到下一次令牌持有的時候再執行。所有傳輸服務都完成后,不管是否有時間剩余,主站都交出令牌。如果主站接到令牌時發現tTR—tTH<O,則只發送一個高優先級報文,完成后交出令牌。主站在令牌傳遞成功后,進入Active_Idle狀態,直到再次獲得令牌。

3 系統工作過程

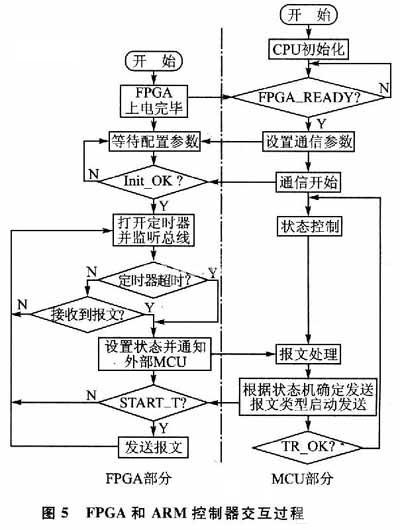

系統工作過程主要是ARM控制器和FPGA的通信交互過程,如圖5所示。從系統安全性上考慮,FPGA和ARM建立通信必須有雙方的確認信號,雖然Altera Cyclone系列FPGA從上電到穩定之前引腳沒有輸出,從系統安全性角度考慮還是不夠的。

這里FPGA_READY信號的設計是考慮到FPGA內部鎖相環模塊PLL穩定工作之前需要建立時間,而其未穩定時是不能對其進行操作的。通信的狀態通過ARM控制器上的狀態機(FDL控制狀態機、調度狀態機和主從通信狀態機)進行轉換,根據定時要求、從站響應幀給出的信息,以及錯誤檢查等信息,狀態機能夠應付一般的異常并自行恢復到正常的通信之中。

4 結論

Profibus-DP協議用任何微處理器都能實現,只要微處理器配有內部或外部的異步串行接口(UART),但當數據傳輸速率較快(超過500 kb/s)時,用ASIC芯片來實現更安全可靠。本文充分利用了FPGA實時性好和ARM核微控制器便于開發的優點,實現了Profibus-DP 1類主站,經過搭建簡單測試環境進行測試,能和市場上的成品主從站建立通信連接并進行基本的主主、主從通信。

來源:國外電子元器件

此內容為AET網站原創,未經授權禁止轉載。