這幾天復習了一下Verilog的語法知識,就借此寫寫我對這些東西的想法吧。感覺呢,是和C語言差不多,具有C語言基礎的朋友學起來應該沒什么問題,和C語言相同的地方就不說了吧,重點說一下不同點吧。

1、模塊的結構

模塊呢,是Verilog的基本設計單元,它主要是由兩部分組成,一個是接口,另一個是邏輯。下面舉一個小例子說明一下:

module xiaomo (a,b,c,d);

input a,b;

output c,d;

assign c=a|b;

assign d=a&b;

endmodule

所謂接口就是第二,三行,說明了一個模塊的信號流向,很明顯,a,b是輸入,c,d是輸出;第四第五行是邏輯,即輸入和輸出之間的關系即c的值是a或b的結果。assign 是連續賦值語句,這個以后再說。

第一行是模塊的端口聲明,即說明一個模塊具體有那幾個接口,有多少接口寫多少,直接套模板就可以module(接口1,接口2……);endmodule代表此模塊結束;

2、模塊的內容

模塊的內容包括3個部分,I/O說明,內部信號說明和功能定義。

關于I/O說明有三種格式,即輸入、輸出、輸入輸出,第三種格式代表信號可以雙向傳送。在寫I/O說明的時候要注明信號位寬,即由幾位組成,例 如 input [7:0] xiaomo;代表輸入一個8位的信號“小墨”,注意這里要用中括號,第一位是位寬減1,接一個冒號,再接數字0,再接端口名;

關于內部信號說明要用到和端口有關的wire和reg類型變量的聲明。模板和上面類似,關于reg和wire變量后面再說。

關于功能定義是模塊中最重要的部分,有三種方法可在模塊中產生邏輯

(1)用assign聲明語句,assign 語句主要用于組合邏輯電路

(2)用實例元件,例如 and #2 u1(q,a,b);(這個我自己概念也有點模糊,不知道怎么解釋)

(3)用always塊,例如 always @(clk or clr)

begin

………

end;

always語句既可以用于描述組合邏輯,也可以描述時序邏輯,但主要以描述時序邏輯電路為主。

小結

在verilog語法中,所有的過程塊(包括initial塊,always塊),連續賦值語句,實例引用都是并行的,也就是說在一個模塊中遇 到這些語句就是同時執行的,而且沒有先后次序。只有連續賦值語句assign和實例引用語句可以獨立于過程塊存在于模塊的功能定義部分,即這兩種語句可以 不用在那兩個過程塊里執行,也可以在模塊的功能定義部分執行,例如第一個例子。

這些和C語言有點不同,對于初學者來說應該都要弄明白。

3、數據類型、變量、常量

對于初學者來說,數據類型只要掌握好reg,wire,integer和parameter型就夠了,其他類型可以暫時不用去理會。

(1)常量就不說了,比較基礎。

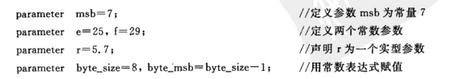

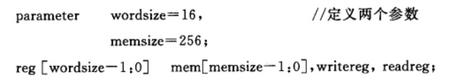

(2)參數型(parameter型)

parameter是用來定義一個常量的,個人理解和C語言里面的int,float 語句一樣,不一樣的是parameter既可以定義整型,也可以定義浮點型或者是表達式。例如

(3)變量

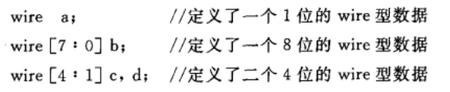

wire型數據常用來表示用以assign關鍵字指定的組合邏輯信號。Verilog程序模塊中輸入、輸出信號類型默認時自動定義成wire型。例子

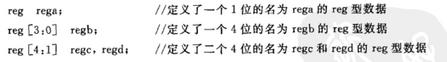

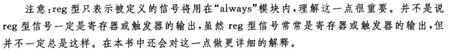

reg型數據是寄存器變量,常用來表示always塊中的指定信號,常代表觸發器。注意,在always塊中被賦值 的每一個信號都必須定義為reg型

。

上面這句話表示不理解,求大神解釋...先放這兒吧..

memory型

由于Verilog中沒有多維數組的存在,memory數據就是通過擴展reg型數據的地址范圍來生成的,他的格式為

reg[n-1:0] 存儲器名[m-1:0];

我舉個例子,比如我定義 reg[7:0] xiaomo[255:0];

這句話的意思是說,我定義了一個名叫“小墨”的存儲器,這個存儲器中有256個8位reg型寄存器,只要理解了這句話,就差不多了。注意,當沒有中括號時代表的是一位,例如

reg xiaomo[m-1:0];代表一個名為“小墨”的存儲器,里面有m個1位的reg型寄存器。

還有個地方我感覺不太明白,見下圖,誰知道這句話上面意思...求大神解釋...

下面這幾句話需要注意

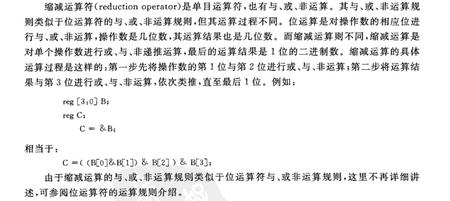

4、運算符及表達式

這里和C語言幾乎一樣,就不做過多解釋了吧。就說一下位拼接運算符和位減運算符,這里C語言里面沒有。

直接看個例子就可以

5、賦值語句

賦值語句共有兩種,即非阻塞賦值,和阻塞賦值。

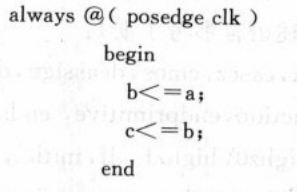

(1)非阻塞賦值

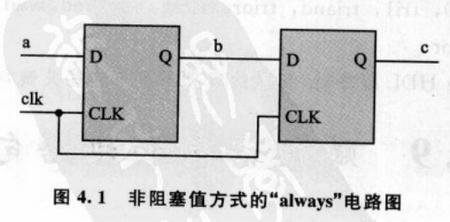

非阻塞賦值方式所賦值的變量不能立即就為下面語句所用,只有當塊結束后才能得到上一次所附的值,這種賦值方式是編寫可綜合的時序邏輯時常用的賦值方式。例如

這個例子的意思是,當時鐘上升沿到來時,a的值給b,b的值給c,但是只有當塊結束時才完成賦值,這么說吧,假如原來a=1,b=2那么當時鐘上升沿到來時a=1,b=2,c=2;當塊結束時,a=b=c=1;

這么理解對嗎?求大神指點...

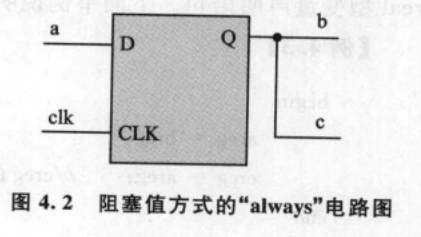

(2)阻塞賦值

與非阻塞賦值不同,賦值語句執行完后塊才結束,b 的值在賦值語句結束后立刻改變,但是在時序邏輯電路中可能會出問題。

always @(clk or clr);

begin

b=a;

c=b;

end

假如開始a=1;當當時鐘上升沿到來時,a=b=c=1;然后塊結束