摘 要: 給出了一種1輸入6輸出頻標分配電路的設計及硬件實現。采用電壓串聯負反饋電路實現信號的放大及分配,閉環增益穩定性比開環增益穩定性提高了1+A0F倍;通過PCB布線優化設計,補償通道間時延差。測試結果表明,設計的頻標分配電路可滿足1~140 MHz的頻標信號分配。

頻標分配電路將一路頻率輸入信號分成功率均等、相位一致的多路輸出信號,在電子系統中經常被用于擴展輸出或提供多路信號源[1]。例如在通信系統中,將同源頻標、同頻測試信號、同源定時控制脈沖信號分配至多臺終端設備,且各設備輸入信號滿足功率相同、頻率相同和相位一致。本文結合頻率分配的電路原理,給出了頻標分配電路的設計及硬件實現方案,最后給出了性能分析及測試結果。

1 頻標分配電路原理

頻標分配電路將一路輸入信號(射頻信號或音/視頻信號)功率均等地分成多路輸出信號,具有一個輸入端和若干輸出端,可采用集成運算放大器實現。在放大電路的設計中,利用負反饋穩定放大電路的工作點,增加增益的恒定性,同時起到減少非線性失真、抑制噪聲、擴展頻帶等作用。放大器加入了負反饋環節后,雖然會犧牲一部分增益,但對放大器一系列性能指標產生很大的有益影響。根據實際情況的需要,采用電壓串聯負反饋方式的電路實現信號的放大及分配。

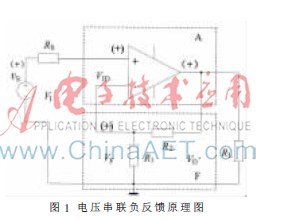

電壓串聯負反饋電路原理圖如圖1所示[2]。基本電路是一只集成運放,用A表示;反饋網絡是由電阻R1和R2組成的分壓器,用F表示。在放大電路的輸入端接入輸入信號vs,由它引起電路各節點的電位極性如圖中(+)號所示,輸入信號vs接在運放的同相輸入端,則VO與vs同極性,VO經反饋網絡而產生的反饋電壓VF亦同極性,VF抵消了VI的一部分,整個放大電路的電壓增益將降低。

電壓負反饋電路的特點是電路的輸出電壓趨向于維持恒定。例如當VI一定時,負載RL減小而使輸出電壓VO下降,則電路的電壓將進行以下自動調整:

RL↓→VO↓→VF↓→VID↑

VO↑

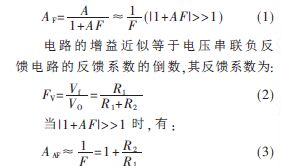

這樣,反饋的結果牽制了VO的下降,從而使VO基本維持恒定。反饋深度對放大電路性能影響較大,在深度負反饋的條件下,放大電路的增益可近似為:

因此在深度負反饋的條件下,可通過調整反饋電阻R1和R2確定工程中所需要的電路增益。

2 電路設計

設計目標是由1路頻標輸入信號產生6路相參頻率輸出,其工作頻率范圍為10~60 MHz,輸入/輸出功率為0~13 dBm。

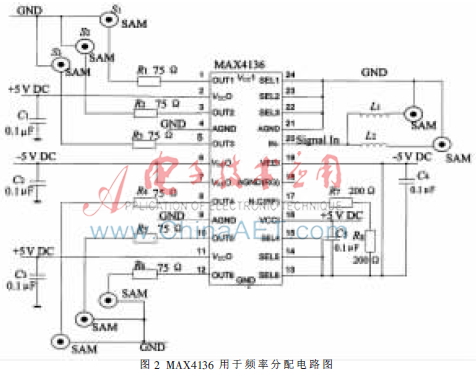

頻標分配電路選用1輸入6輸出電壓反饋式放大集成芯片[3] MAX4136實現1路輸入多路輸出的功能。MAX4136最大輸入信號帶寬為140 MHz,轉換速率為1 000 V/s,通道匹配時間小于25 ns。該器件應用在頻標分配電路設計中,可以對視頻信號進行高速匹配并分配放大。

MAX4136的每一個輸出端口可以驅動5個150 Ω的負載,當然隨著負載的增大,信號的失真度也將增加,所以在負載設計時應考慮到芯片的最大負荷,使信號輸出最佳。根據反饋電路原理,可通過調節外接電阻RF、RG的阻值調整電路增益,這里取RF=200 Ω,RG=200 Ω,實現2倍電路增益。

芯片采用TTL/CMOS兼容的數字控制電平(SEL)來控制每一個輸出放大器,當SEL為低電平時輸出放大器導通,為高電平時輸出截止,導通/截止的時間小于25 ns。圖2 為MAX4136用于頻率分配的電路圖。

3 性能分析

頻綜信號的多通道分配等應用對分配器的增益穩定性、損耗等技術指標提出了較高的要求。

(1)增益穩定性

放大器的增益穩定性常通過放大倍數的相對變化率來反應。因此dA/A的大小可以衡量增益的穩定性,該值越小,放大器的穩定性越高。由于晶體管參數ρ隨溫度變化,放大增益的穩定性也要發生變化。對式(1)進行微分可得:

![J)QK]TJ`VYAWXUXGN_4FOAI.png J)QK]TJ`VYAWXUXGN_4FOAI.png](http://files.chinaaet.com/images/2015/06/11/6356965524453794326347879.png)

即引入負反饋后,閉環增益的穩定性比開環增益穩定性提高了1+AoF倍。

(2) 分配損耗

輸入至輸出的分配損耗L(dB)與頻標分配電路的功率分配比有關:

L=10log(1/N) (5)

其中N為分配器路數。對于1輸入6輸出頻標分配電路,根據計算可得分配損耗約為8 dB。

4 實現及測試結果

硬件實現過程中,為了減小電源單元產生的電磁干擾[4],結合應用背景選擇鋰電池供電方案,同時電源模塊應盡量遠離分配電路的輸入電路。為了提高通道間相位一致性,要求芯片MAX4136輸出端至分配電路輸出端口的布線長度要一致,在PCB設計時,通過布線優化來實現。

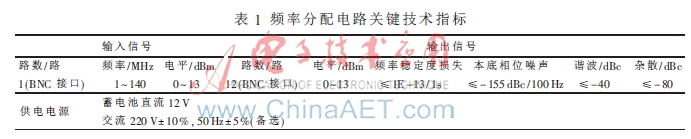

經測試,頻標分配電路的關鍵技術指標總結如表1所示。

本文通過電壓串聯負反饋電路原理分析,給出了頻標分配電路的設計及硬件實現。分析了系統性能,采用電壓串聯負反饋電路實現信號的放大及分配,閉環增益穩定性比開環增益穩定性提高了1+AoF倍;對于1輸入6輸出頻標分配電路,根據計算可得分配損耗約為8 dB。硬件實現及測試結果表明,設計的頻標分配電路可很好地滿足同源頻標、測試信號、脈沖信號的放大及分配。

參考文獻

[1] 韓曉英.負反饋電路的應用[J].山西電力,2011(3):41-43.

[2] 康華光,陳大欽.電子技術基礎[M].北京:高等教育出版社,1999.

[3] 董葉梓,張鵬,毛陸虹.采用噪聲抵消技術的高增益CMOS寬帶LNA設計[J]. 電子技術應用,2013,39(5):44-47,50.

[4] 楊世平,葉向德.電壓并聯負反饋電路的低噪聲化條件[J].延安大學學報(自然科學版),2003,22(4):49-50.