文獻標識碼: A

文章編號: 0258-7998(2014)11-0036-03

0 引言

近年來,大規模集成電路的快速發展使其在計算機視覺領域得到了廣泛的應用。而運動目標檢測技術是計算機視覺的重要組成部分,因此吸引了世界各國科學研究者投入到對這一技術的研究[1-2]。

目前,運動目標檢測最常用的是幀間差分算法、背景差分算法和光流法3種算法。通過比較,本系統采用易于硬件實現、實時性好的幀間差分算法[3-4]。FPGA內含豐富的邏輯資源,加之內嵌著DSP塊,有著出色的計算能力;同時FPGA采用的體系是并行體系且具有流水性的工作方式,可以加快數據流的數據。因此,本設計采用FPGA模塊作為主控制和算法處理單元。

1 系統的總體結構

整個系統由視頻信號采集單元、控制和算法實現單元、數據緩存單元和視頻信號顯示單元四部分組成,如圖1所示。

視頻采集單元在FPGA的控制下,對帶有運動目標的模擬視頻進行采集,并轉換為數字視頻信號傳輸到FPGA進一步處理;FPGA主要負責對其他模塊進行功能控制以及對傳入的視頻信號進行灰度化、幀間差分和閾值分割,以實現運動目標的檢測; 數據緩存單元是在FPGA的控制下,完成對視頻圖像數據的緩存,配合FPGA進行圖像處理;視頻信號顯示單元是在FPGA的控制下對處理前后的視頻圖像進行顯示,可以直觀地觀察檢測效果。

2 系統硬件設計

2.1 視頻信號采集單元

本系統使用的CCD(Charge Coupled Device)相機輸出PAL制式視頻。而FPGA只能處理數字視頻信號,因此需要將PAL制式信號轉換為標準的數字視頻格式。飛利浦公司研制的SAA7113H是一款功能強大的9位視頻解碼芯片,它可以自動檢測視頻制式,并且可以輸出包含YUV4:2:2在內的不同格式的數字視頻。圖2所示為本系統中視頻解碼模塊的電路圖。

本設計僅使用4路輸入通道中的1路即可,將SAA7113H解碼后的數字視頻信號傳輸給FPGA進行下一步處理,片選信號CE接高電平時,芯片選通;像素時鐘接口LLC外接27 MHz時鐘信號。

2.2 視頻圖像緩存單元

在完成運動目標檢測的過程中,需要至少緩存一幀圖像。為了節省FPGA內部有限的存儲資源,緩存數據量巨大的視頻圖像時,本系統采用外接DDR SDRAM來進行數據緩存。Hynix公司研制的存儲容量為2 M×4 Banks×16 bit的HY57V281620FTP-H型號SDRAM滿足本設計要求。其各引腳功能如表1所示。其中WE#無效時進行讀操作;A0~A11為行列地址選擇信號,當列有效時,使用A0~A8表示列地址,當行有效時,使用A0~A11表示行地址,其中A10還是自動預充的標記[5]。

2.3 視頻圖像顯示單元

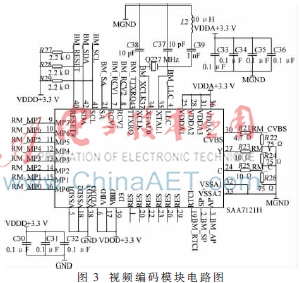

經過FPGA處理輸出的視頻信號為數字信號,而一般的顯示器只能顯示模擬信號,因此需要將數字視頻信號轉換為模擬視頻信號進行顯示。飛利浦公司的視頻編碼芯片SAA7121H轉換效率高,設計簡單,可以將FPGA處理輸出的YCbCr格式的數字視頻信號編碼成可以直接顯示的PAL制式的模擬視頻信號,本設計采用此芯片完成視頻編碼并進行顯示。其電路如圖3所示。

MP0~MP7是8個數字視頻數據輸入端口;RCV1、RCV2是行、場同步信號接口;LLC是27 MHz像素時鐘信號接口;SCL、RESET和SDA分別是串行時鐘信號線、復位信號以及雙向串行數據信號線,設計時這3個接口都要外接一個2.2 kΩ的上拉電阻。CVBS是CVBS信號的輸出端口,與顯示屏連接可顯示視頻圖像。

3 系統軟件設計

3.1 幀間差分算法

幀間差分算法是對視頻信號中相鄰幀或者多幀圖像中同一位置的像素點進行差分運算。現在以相鄰幀的幀間差分算法為例,其基本流程如圖4所示。設第k-1幀圖像中(x,y)位置處的像素值為fk-1(x,y),第k幀相同位置處的像素值為fk(x,y),先對二者按式(1)進行差分運算得到?駐k(x,y),再將?駐k(x,y)按式(2)進行二值化處理。

其中,T為預設“閾值”,可以從0~255中取值,具體大小與實際環境有關。當k(x,y)≥T時,Rk(x,y)=1,此時判斷該像素點為運動區域像素點;當?駐k(x,y)<T時,Rk(x,y)=0,此時判斷該像素點為靜止區域像素點。

幀間差分算法中兩幀圖像相差的時間短,使得環境中光線變化等不可控因素對設計的影響較小,因此具有良好的抗干擾性,且對動態環境有很強的適應能力。

3.2 幀間差分算法的實現

系統開始工作后,FPGA先通過I2C總線對SAA7113H和SAA7121H進行初始化,使視頻采集及視頻顯示單元能夠正常工作。配置流程如圖5所示。

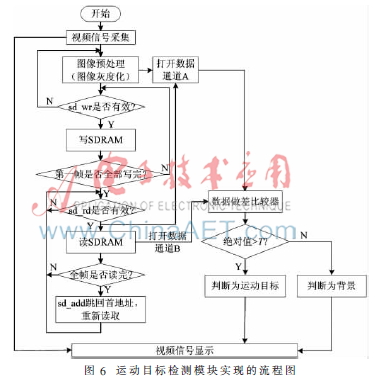

視頻信號采集單元采集的有效視頻數據分兩路傳輸:一路直接傳輸給視頻信號顯示單元進行顯示,用來與處理后的結果進行對比分析;另一路傳輸給圖像預處理模塊進行灰度化處理,以備后續處理。經過圖像預處理模塊后的視頻數據僅有Y分量;同時需要設置A、B兩個數據通道進行傳輸。當寫信號sd_wr有效,提取的Y分量數據開始寫入SDRAM中,當讀信號sd_rd有效時,同時將A、B兩個數據通道打開;此時A數據通道傳輸的數據是第n+m幀圖像數據的Y分量,而B數據通道的數據卻是第n幀圖像數據的Y分量。A、B兩通道的數據同時傳入“數據做差比較器”中進行差分運算,即能得出視頻中第n+m幀圖像的像素點與第n幀圖像的像素點的差分結果。若差分結果的絕對值大于預先設定的閾值t(t值取25),則判定此像素點發生較大的變化,為運動目標區域的像素點。設計流程如圖6所示[6]。

4 系統試驗結果與分析

利用幀間差分算法對運動目標檢測后,為完善檢測效果,需要進行“閾值分割”處理,而這個“閾值”需要根據具體實驗測試環境提前設定。選用與最終實驗測試攝像頭采集的視頻環境類似的一段視頻進行軟件仿真,分別選用“閾值”為10、20、25、30、40、50進行仿真分析,結果如圖7所示。

從圖7中可以看出,當“閾值”小于25時,出現了很多誤判,導致檢測效果不理想;當“閾值”大于25時,雖然干擾像素點減少,但檢測出的運動目標出現了“空洞”,“閾值”越大,“空洞”越大。因此,“閾值”選定為25。

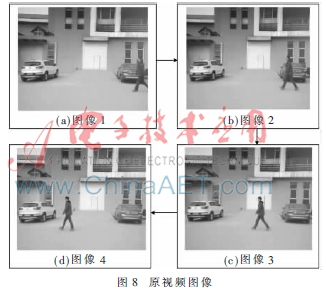

搭建實驗平臺對系統進行測試,顯示屏顯示的原視頻圖像的其中4幀圖像如8所示;經過硬件電路端處理以后的視頻圖像的其中4幀圖像如圖9所示。

分析以上實驗結果,不難發現,圖9(a)和圖9(b)所示的檢測結果出現了較多的“空洞”,因為在這兩個時間段,運動中的人經過一輛與背景顏色相近的汽車前面,在檢測時,把運動目標上的部分像素點誤認為是背景圖像,故出現了“空洞”;圖9(c)所示的檢測效果更好,因為這段時間運動目標顏色與所處背景顏色差異較大,在進行幀間差分檢測時,運動目標能更好地從背景中分割出來;圖9(d)所示的檢測結果中,運動中的人臉部位出現了空洞,因為此時人臉膚色與目標所處的背景顏色接近。

5 結論

本文設計了一種基于FPGA的運動目標檢測系統,以FPGA為控制核心和算法實現單元,加上外圍的采集和顯示電路,可以實時地檢測運動目標并顯示。在軍事公安、工業生產、生物醫學等各個領域都有廣泛的應用前景。

參考文獻

[1] 郭浩.基于FPGA的運動目標檢測系統設計與實現[D].武漢:武漢理工大學,2013.

[2] 劉攀.車輛目標檢測和跟蹤技術研究[D].太原:中北大學,2011.

[3] 王瑾琦.復雜背景下運動目標檢測與跟蹤方法研究[D].太原:中北大學,2012.

[4] 高美鳳,劉娣.分塊幀差和背景相融合的運動目標檢測[J].計算機應用研究,2013,30(1):299-302.

[5] 程曉東,鄭為民,唐志敏.基于DDR SDRAM控制器時序分析的模型[J].計算機工程,2005,31(17):182-184.

[6] 田耘,徐文波.Xilinx FPGA開發實用教程[M].北京:清華大學出版社,2012.