景德勝1,2

(1.中航工業西安航空計算技術研究所,陜西 西安 710068;2.中國民航大學 適航學院,天津 300300)

摘要:低功耗是嵌入式計算機的發展趨勢,是彈載計算機設計要解決的關鍵問題。以基于多核處理器的彈載計算機為例,介紹了功率消耗產生的原理,從處理器、軟件設計、Cache設計和可編程邏輯設計等方面對影響彈載計算機系統功耗的因素進行了分析,并提出了低功耗設計的方法和技巧。

關鍵詞:多核;彈載計算機;嵌入式系統;低功耗

0引言

彈載計算機是實時嵌入式系統,用于接收、處理導引系統的信號,控制導彈飛行實現對攻擊目標的檢測、捕獲和跟蹤,是導彈制導系統的關鍵組成部分。隨著技術的發展,新一代導彈要具備攻擊高速、高機動目標的能力,具備全方位攻擊的能力,同時對導彈的探測能力、反隱身和抗干擾能力都提出了更高的要求,使得彈載計算機需要處理的數據復雜度越來越大、實時性要求越來越高。

彈載計算機因應用環境特殊,安裝在導彈狹小的制導艙內,發射后由導彈上電池供電,對系統功耗和產品尺寸提出了嚴格要求。高性能、低功耗成為實現彈載計算機功能需求的基礎。基于單片異構體系架構的多核處理器以其優越的處理性能、靈活高速的存儲結構和豐富的對外接口很好地解決了彈載計算機對高性能的要求,因此如何通過改進彈載計算機軟硬件設計降低系統功耗,成為系統設計中需要研究和解決的重要問題。

1影響功耗的因素

低功耗設計技術大致可以分為兩類:靜態技術和動態技術。靜態技術是指從系統構造、工作原理方面著手,降低系統功耗,如選用低功耗器件,采用異步電路體系設計等;動態技術是通過改變系統的運行行為來達到降低系統功耗的目的,如在系統工作過程中,根據運行狀況將器件從工作狀態轉入睡眠狀態。彈載計算機由印制電路板、元器件和軟件等組成,主要功耗由元器件中的集成電路產生。

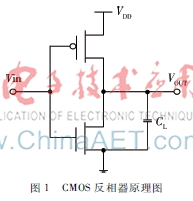

CMOS反相器[1]是集成電路的重要組成部分,是所有集成芯片設計的核心,邏輯門、加法器、乘法器和微處理器等比較復雜電路的電氣特性都可通過分析組成其CMOS反相器的特性得到,然后通過邏輯門和加法器等部件特性來分析處理器等的特性,CMOS反相器對分析集成電路延遲時間和功耗有重要意義。

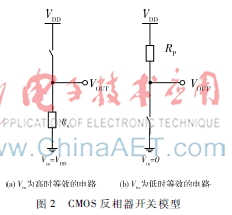

圖1是一個靜態CMOS反相器的電路圖,晶體管是一個具有無限關斷電阻和有限導通電阻的開關。當Vin為高并等于VDD時,NMOS管導通、PMOS管截止,見圖2(a)等效電路,此時輸出Vout為0 V;當Vin為低等于0 V時,PMOS管導通、NMOS管截止,見圖2(b)等效電路,此時輸出Vout為高電平VDD,由此達到反相器的功能。

圖2CMOS反相器開關模型CMOS 反相器的功耗包括動態功耗、靜態功耗和短路功耗等三部分,總功耗組成見式(1)。

P=PD+PSC+PS=α·CL·V2DD·f+ISC·VDD+Ileak·VDD(1)

其中:PD是動態功耗,與電源電壓VDD、負載電容CL、工作頻率f 和開關活動率α 相關;PSC是短路功耗,在輸入電平處于VTN至(VDD + VTP)范圍內時會使CMOS電路中的PMOS和NMOS晶體管都導通,產生短路電流ISC,從而引起開關過程中的附加短路功耗,短路功耗與(VDD - 2VT)有強烈依賴關系;PS是靜態功耗,理想情況下CMOS電路的靜態功耗是零,但實際處于截止態的MOS晶體管存在泄漏電流Ileak,會引起一定靜態功耗。在集成電路中,動態功耗是整個CMOS集成電路功耗的主要組成部分,占到90%以上,靜態下漏電流所產生的功耗占總功耗的比例不足1%,幾乎可以忽略。

除集成電路占主要功耗外,有源開關器件在狀態轉換時,其純電阻元件上、非理想元件等效電阻和印制板中連線等在工作中也會消耗一定能量。

2低功耗設計技術

以使用TI多核處理器TMS320C6678的彈載計算機為例[2]。TMS320C6678整個系統由TeraNet將8個內核、網絡協處理器、共享存儲管理器、多核導航器、外設及其他功能部件連接起來,處理單元由8個相同的內核組成,互連網絡TeraNet為分層結構的總線形式,且內核通過共享存儲管理器共享容量為4 MB的共享存儲器,從體系結構上看類似于并行計算機中的對稱多處理機(SMP),該架構支持8位、16位、32位、64位、128位和256位數據,可根據功耗和性能等因素折中選擇。

2.1軟件設計

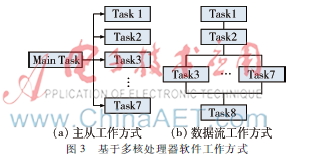

為了在有效發揮多核處理器系統的運算處理和數據傳輸能力的前提下,降低功耗,獲得多核處理器實際應用時的最佳性能,要根據實際任務需要,考慮每個內核之間的任務分配和信息傳輸[3]。多核處理器任務執行主要有兩種運行方式:主從方式和數據流方式。主從方式即一個核管理主任務,由主任務對其他核任務進行管理;數據流方式即任務按照數據的傳輸來運行,由一個任務推動另外一個運行,見圖3。主從方式7各個內核工作情況差異較大,在完成相同任務情況下,無法通過降低整個處理器的時鐘頻率來降低處理器功耗;數據流方式每個圖3基于多核處理器軟件工作方式內核工作情況比較統一,實時性高,與主從方式相比可適當選用較低的時鐘頻率,降低整個處理器的功耗,但數據流方式要求對整個任務的協同和并行工作流程非常清晰。

軟件設計中盡量使用中斷方式代替查詢方式,中斷方式下處理器可以什么都不做,甚至可以進入等待模式或停止模式。而在查詢方式下處理器必須不停地訪問寄存器,造成很多額外功耗。用宏代替子程序,讀RAM會比讀FLASH帶來更大功耗,處理器在調用子程序時,需要先保存現場,調用完畢后再恢復現場,彈棧壓棧至少帶來2次對RAM的操作,在編譯宏時會展開,處理器執行時只是順序執行指令,避免了彈棧壓棧操作,且片內FLASH的大小完全可以滿足編譯后代碼量的增加,編程時工作量幾乎相同,低功耗性能突出的ARM在處理器設計上僅允許一次子程序調用。對于非必須實時計算的參數,使用常量或查表的方式替代處理器的實時計算。使用移位運算來代替乘除法運算等也可有效降低處理器的功耗。

2.2Cache設計

數據的時間和空間局部性是內存系統優化設計研究的重要部分[4],核心問題在于內存結構的優化無法適應每個應用程序。不同研究者關于Cache參數對處理器性能及功耗影響的相同分析結論為:Cache面積增大會降低失效率,但功耗會隨之增大;減小Cache面積帶來的高失效率和較大時間延遲依然會使整個系統功耗上升;增加Cache組相聯度會增加Cache命中率,進而可以降低功耗。因此采用相關優化算法讓Cache在運行時動態可重構,可取得較優的效能。彈載計算機應用程序一旦確定,執行相對單一和固定,考慮到彈載計算機的可靠性和執行任務的特點,對不同Cache空間的大小和組數的執行應用程序進行命中率仿真測試,根據仿真結果配置合適的Cache空間和組數,可降低Cache消耗的功率。

2.3可編程邏輯設計

可編程器件的選擇對功耗影響較大[5],例如寄存器傳輸級(RTL)器件比門級器件可以減少更多的功耗。RTL級的轉換可以在一個周期內判斷出電路正在計算結果的部分是否為有用操作,被判定為在一個時鐘周期內進行無用操作的時序或組合電路會被采用的門控時鐘或睡眠模式關閉。可編程邏輯設計時,降低邏輯電路的時鐘頻率,僅保留必須在高速時鐘域運行的邏輯電路;保持較小的邏輯電路面積,對無速度要求的邏輯電路進行優化設計;將電壓降低到數據手冊規定的最小值;避免I/O管腳上拉、下拉沖突等方法也可達到降低功耗的目的。

2.4印制板設計

印制電路板是電子元器件的支撐體,是電氣連接的提供者。為了降低在印制板上的功率耗散,印制板設計在滿足電氣連接的穩定性、電磁兼容和布局合理等要求的前提下,要對信號的走向及電源和地線網絡進行整體規劃,布線時要求走線盡可能短,線寬要根據器件本身和周邊器件的情況進行考慮,盡量寬,走線拐角最好大于90°,盡量設計為具有一定尺寸的均勻圓弧線,相鄰兩面走線應避免相互平行,以減少寄生電容耦合。

2.5其他設計

集成電路未使用引腳的處理方法也會影響功耗的差異[6],例如在集成電路未使用輸入引腳上極易產生電荷積累,根據公式U=Q/C,式中Q為電量,C為電容,U為電壓,當累積電荷達到一定程度時,就會產生影響輸入引腳狀態的電壓,輸入引腳邏輯狀態變得不可控,當電平處在邏輯0和1的過渡區時,CMOS反相器的NMOS管和PMOS管都會導通,這將帶來很大的功耗浪費,因此一定要對集成電路的未使用引腳進行上拉或下拉處理,此種處理方法也可使未使用的引腳處于一個固定邏輯狀態。

3總結

低功耗對彈載計算機十分重要,相關設計研究眾多,隨著處理器技術的發展,研究對象逐漸以基于多核處理器的彈載計算機為主。各種低功耗設計在彈載計算機上應用形式多樣,但主要集中在體系架構設計、低功耗元器件的選用、供電管理和軟件優化幾個方面。體系架構設計應以異步設計為主,對性能和時序要求嚴格的部分采用同步設計;選擇采用高K/金屬柵和動態閾值等技術的CMOS器件,是降低功耗的最直接辦法;選用具有電源調節或低功耗模式的處理器等器件,可在不增加太大工作量的情況下,通過供電管理的方式降低功耗;軟件的設計優劣對整個彈載計算機的運行十分重要,合理調節各個部件的運行狀況,在滿足性能要求的情況下可通過減少電路的活動時間降低功耗。

彈載計算機應用對象特殊,對性能、可靠性和實時性等有非常嚴格的要求,彈載計算機是否能良好工作直接決定導彈執行任務的成敗,因此設計者必須根據實際應用要求剪裁使用低功耗設計技術。

參考文獻

[1] RABAEY J M.數字集成電路—電路、系統與設計[M].周潤德,譯.北京:電子工業出版社,2010.

[2] 汪安民,張松燦.TMS320C6000DSP實用技術與開發案例[M].北京:人民郵電出版社,2008.

[3] 王江.多核系統中提升啟動速度之策略[J].電子技術應用,2014,40(3):2528.

[4] 何勇,肖斌,陳章龍,等. 一種低功耗的動態可重構Cache設計[J]. 計算機應用與軟件,2009,26(8):247250.

[5] 張偉棟,李濤.一種基于FPGA的高集成度技術研究設計[J].微型機與應用,2015,34(4):1113,25.

[6] 張興,杜剛,王源,等. 超低功耗集成電路技術[J].中國科學,2012,42(12):15441558.