李春雨

(浙江機電職業技術學院,浙江 杭州 310053)

摘要:在基于mTCA規范的媒體網關系統中,兩塊主控制板要求熱備份,當一塊主控板故障時,另一塊主控板需自動升主,替代故障板。對現有的主備倒換方案進行了分析,并改進了現有方案,該方案通過高低溫老化測試,工作可靠。

關鍵詞:媒體網關;CPLD;主備倒換;熱交換;主控板;背板;

中圖分類號:TN79文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2016.24.012

引用格式:李春雨. 媒體網關系統中的主備倒換設計改進方案[J].微型機與應用,2016,35(24):40-41,49.

0引言

主控板是媒體網關中的大腦,管理和維護系統中的其他單板,與上位機通信,傳遞信令信息,要求全年無故障工作,主備倒換技術是提高通信設備可靠性的重要解決方案之一[1],因此媒體網關中的主控板需要熱備份,當一塊板故障后,另一塊備用板立刻升主,平滑切換。本文著重研究小型媒體網關中主控板的主備倒換。

1主控板的硬件設計

媒體網關中主控板管理其他業務板,加載其他業務板,分發時鐘,監控風扇板和電源板的狀態。主控板的框圖如圖1所示。

處理器采用RMI公司的XLS408,通過可編程邏輯器件接三個外設:(1)FPGA:主要實現32路智能管理總線,管理、監控、加載業務板。(2)SA8000:該芯片是時鐘芯片,產生高精度的38.88 MHz時鐘。(3)SA586:該芯片是E1信號收發芯片。

鑒于主控板的重要地位,它要求全年無故障工作,需支持主備板熱備份。所謂熱備份,即媒體網關機框上電時,有兩塊電路結構完全相同的主控板,根據所在的槽位是奇槽位還是偶槽位區分出主板和備板,完全啟動之后,業務都運行在主板上,備板不參與業務控制,但主板會將自己保存的信息同步到備板上,這個過程稱為熱備份[2]。

2現有的主備倒換方案

方案1:基于FPGA的主備倒換方案[3],該方案實現框圖如圖2所示。

圖2基于FPGA的主備倒換方案該方案基于FPGA實現主備倒換邏輯,圖2所示6個信號通過背板實現本板和備用主控板的傳遞,在CPU控制下實現倒換,其優點是穩定性好,但缺點是FPGA基于RAM結構,每次上電FPGA代碼都要從一個外部存儲設備加載到內部的RAM中[4],系統上電時由控制器讀出配置數據再傳送給FPGA進行配置[5]。這個配置過程和配置數據大小與配置時的加載時鐘關系很大,一般需要幾秒鐘甚至幾分鐘,延長了倒換時間。

方案2:基于CPLD的主備倒換方案[6],該方案實現如圖3所示。

該方案用CPLD代替FPGA,可以解決FPGA加載慢的問題,CPLD內部代碼存儲采用Flash機制,不需要從外部加載,啟動時間為1 ms,因此使用CPLD倒換速度會大大提高。

但是在實際異常測試和振動試驗中發現,該方案存在雙主的故障,即兩塊主控板同時作為有效的主用板工作,造成輸出信號沖突。經分析,由于媒體網關上板卡多,信號多,高密度互連背板通常使用專用的連接器,如華為的UAP6600上主控板使用的背板連接器中用的FCI公司的AIRMAX連接器,而且要用圖4所示的7組連接器[7],在產品的振動試驗中發現經常出現雙主現象。因此上述基于CPLD的主備倒換方案也存在問題。

3改進的主備倒換方案

3.1硬件改進措施

基于異常測試和可靠性測試結果,下面分析方案2出現雙主的原因。

媒體網關上有多塊板卡插在背板上,主控板和背板的連接器采用圖4所示方案,7個54管腳的AIRMAX連接器壓接到背板上,圖5是對板主備指示信號(ACT_VS信號)在連接器上的位置。

由于壓接工藝的關系,存在連接器不平整、AIRMAX連接器沒有短針、單板拔出時插穩信號還沒斷開但是ACT_VS脫離等現象;單板插入時,也會出現插穩信號已接觸到而ACT_VS還沒有連接, 從而ACT_VS檢測不到,導致本板認為對板已經降備,因此本板升主,出現雙主現象。

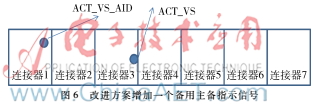

改進方案是:增加一個輔助對板主備指示信號,靠近邊緣的連接器,輔助對板主備指示信號靠近插穩信號,如圖6所示。

3.2邏輯代碼改進措施

機框上電后,兩塊主用板同時為主,但是偶槽位主控板在18個CPLD工作時鐘后就退出主用狀態,奇槽位主控板一直為主。CPLD內代碼用Verilog[8]語言編程實現,程序流程圖如圖7所示。

3.3改進方案的倒換時間計算

機框上電后,18個CPLD時鐘周期后,偶槽位8號主控板退出主用,31個時鐘周期后,奇槽位7號主控板退出主用,所以正常情況都是7號槽位的單板處于主用狀態。工作后,從圖7可以看出,如果8號槽位單板4個時鐘周期檢測不到對板送來的ACT_VS和ACT_VS_AID信號,則本板升主,如CPLD工作時鐘為15 ns,則倒換時間為4×CPLD CLK=4×15 ns=60 ns。

4結論

媒體網關上背板和主控板連接信號很多,各類信號超過350個,必須采用適合高密度背板的連接器,而連接器由于壓接工藝的問題,存在主用板接收不到ACT_VS信號的情形,采用上述解決方案,進行多次異常測試和振動測試,未出現問題。

參考文獻

[1] 李潔,黃婷熙,潘濤濤. 高可靠性通信設備主備倒換軟件實現方法[J]. 電視技術,2013,37(11):170 172.

[2] 張玉峰,孫知信. 基于熱備份的主備倒換在高端路由器中的應用[J]. 計算機技術與發展,2010,20(3):172 175,179.

[3] 譚宇,姚亞峰,陳登,等. 基于FPGA主備倒換的電路設計與實現[J]. 電視技術,2014,38(11):82 85,102.

[4] 李春雨,張麗霞. 利用CPLD提高FPGA加載速度[J]. 電子器件,2013,36(4):550 553.

[5] 李春雨.基于CPLD的FPGA從并快速加載方案[J].中興通訊技術,2014,20(4):57 59.

[6] 施世華,高西全,靳松杰,等.高可靠性通信設備的主備倒換設計[J].電子科技,2007(7):47 50.

[7] Fleck Research.AirMax VS Connector System[EB/OL].(200909xx)[2016 07 19]http://www.fci.com/.

[8] 王靜霞.FPGA/CPLD應用技術(Verilog語言版)[M].北京:電子工業出版社,2011.