近年來,我國電子信息產業和市場高速增長,DSP 芯片產品需求量持續增大,雖然有一些集成電路設計企業從事 DSP 系統及相關產品的開發與應用,但在 DSP 芯片的研發上,只在某些大學、科研院所做過預研性課題,還沒有形成自己的獨立知識產權的技術,因此對 DSP 處理器的設計有不可估量的作用,而體系結構的設計是處理器設計的靈魂,處理器的設計首先從體系結構的設計開始,DSP 處理器的體系結構一直緊緊圍繞著 DSP 算法和各種應用的不斷發展而改進和優化,隨著各種并行處理技術(VLIW,SIMD,超標量,多處理機等)、可重構技術和低功耗體系結構技術的出現,使各種新的 DSP 處理器體系結構不斷涌現,使得如今的 DSP 處理器性能不斷提高,并使它們在通信、自動控制、雷達、氣象、導航、機器人等許多嵌入式實時領域得到了廣泛應用。而這些領域都要求處理器是高速、低功耗的。因此我們在對當前 DSP 體系結構的最新發展的全面考察的基礎上,考慮到低功耗、低成本、高性能等要求,設計了一個 16 位嵌入式定點 DSP 處理器μDSP 的體系結構,如圖 1。

下面就μDSP 的總線結構、流水線設計、特殊的指令系統、尋址方式、強大的控制部件和高速的運算單元等幾個方面對μDSP 的體系結構設計進行了詳細的闡述。

1.改進型哈佛總線結構

由于 DSP 處理器主要應用于各類數據運算,數據吞吐率都非常大。特別是進行乘累加運算時,需要 2 個甚至 3 個數據同時參與運算,傳統的馮?諾曼結構無法滿足數據和指令存取的需求,所以,DSP 處理器普遍采用哈佛總線結構。雖然哈佛結構使用采取分開的程序存儲器和數據存儲器,以滿足同時存取數據和取指令的需求,但是這種結構由于缺乏指令和數據存儲空間的靈活性,使得存儲器空間不能得到靈活、充分的使用。

為進一步提高性能,μDSP 采用了改進的哈佛結構,在采用分開的程序存儲器和數據存儲器的同時,允許數據存儲在程序存儲器中,數據存儲器和程序存儲器統一編址。程序存儲器的大小為 32K*24bit(指令為 24 位寬),數據存儲器大小為 32K*16bit(數據位寬為 16)。

采用 4 總線結構,這 4 條總線分別是程序地址總線(PMA)、程序數據總線(PMD),數據地址總線(DMA)、數據數據總線(DMD)。存儲器采用同步 SRAM,并采用流水線方式存取數據和指令,完成一次訪問需經過兩級流水線。為進一步提高存取靈活性,程序總線既可以取指令,又可以存取數據,既可訪問程序存儲器,又可以訪問數據存儲器。另外,為了減少存儲器的訪問周期,增加了一個片內指令 Cache,用來存放常用的指令,Cache 的大小為 64*43bit,可存儲 64 個指令-地址對。指令 Cache 采用組相聯映射方式,并采取最近最少使用(LeastRecentlyUsed)替換策略。

這種改進的哈佛結構不僅提高了指令和數據存取的效率,還提高了存儲器的利用率,是一種比較好的結構。

2.六級流水線設計

流水線設計是現代處理器設計的核心。流水線的設計要考慮諸多的因素,比如流水線各級的平衡、流水線的吞吐率以及流水線的結構復雜度等方面,我們采用六級流水線設計,每一級的名稱及需要完成的如下功能:

(1)Look-AheadAddress(LA):這一階段程序控制器從各個地址來源中選出本時鐘進入流水線的指令的地址,把指令地址放在 PMA 總線上,它也用于解決總線沖突問題。因為 PMA 總線可能同時被 LA 和 AD 兩個階段使用,這時總線發生沖突,程序控制器就查找這條指令是否在 Cache 里。如果命中(Hit),指令就從 Cache 中提前取出,使得 AD 可以使用總線;如果不命中(Miss),就讓 AD 優先使用總線,程序控制器在下一個周期得到 PMA 總線。

(2)PrefetchAddress(PA):這一階段把指令地址送到存儲器,開始取指令。由于使用的是同步兩級流水 SRAM,這一階段指令并沒有馬上被取出,要到下一周期結束時才完成取指過程。

(3)FetchAddress(FA):這一階段指令通過 PMD 總線從存儲器取出。因為存儲器需要兩個周期的時間完成訪問,即從地址放在總線上到得到數據需要兩個周期,所以上一周期開始的取指令到這個周期結束。

(4)AddressDecode(AD):指令的某些部分被譯碼,比如 DAG 操作。如果指令需要存儲器數據,這個數據的地址就放在適當的地址總線上。同時將沒有解碼的部分送到下一級。

(5)InstrucTIonDecode(ID):這個階段對指令的其余部分譯碼。同時也用于等待存儲器訪問,由于取數據同樣要兩個周期。

(6)Execute(PC):這一階段執行指令,設置各狀態標志位,并把結果寫到適當的寄存器中。

3.特殊的指令系統

處理器的設計首先從指令系統設計開始,不同的指令系統也決定了不同的處理器結構設計,μDSP 的指令系統非常豐富,可以完成各種 DSP 算法所要求的功能,大體來說,需要設計以下 4 大類指令:程序流控制指令,數據移動指令,運算指令和多功能指令。必須滿足以下要求:

(1)24 位指令寬度;

(2)高密度指令編碼;

(3)提供多功能指令,使得一條指令可完成多個操作;

(4)支持雙字指令;

(5)提供零開銷循環指令;

(6)與主流 DSP(ADI 公司的 ADSP219x 系列)兼容。

4.靈活的尋址方式

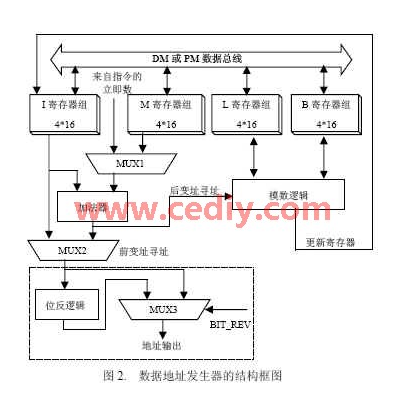

由于 DSP 算法的獨特性,一般通用處理器的普通尋址方式不能滿足要求,所以 DSP 處理器一般采用許多特殊的、靈活的尋址方式。μDSP 中主要有 6 種尋址方式:直接尋址、前變址尋址、后變址尋址、循環尋址、位反尋址、分頁尋址。要實現這些尋址方式,設計了一個數據地址發生器(DAG),如下圖 2,考慮到μDSP 可以同時對程序存儲器和數據存儲器進行訪問,設計了兩個 DAG,它們的不同之處在于:DAG1 只能產生數據存儲器地址,但有位反功能;DAG2 可以產生數據存儲器地址也可以產生程序存儲器的地址,但是沒有位反功能。它有 4 個寄存器組:索引寄存器組(IRegisters)、修改寄存器組(MRegisters),長度寄存器組(LRegisters)和基址寄存器組(BRegisters)。每個寄存器組有 4 個 16 位的寄存器,可以通過 DMD 總線進行讀寫。I 寄存器組存放訪問存儲器的實際地址,M 寄存器組用于保存地址偏移量,L 寄存器組和 B 寄存器組則是專門用于循環尋址的,前者保存循環尋址中數據塊的長度,后者保存循環尋址的首地址。圖中虛線框中部分為 DAG1 所獨有。

5.強大的控制部件

控制部件是完成整個 DSP 處理器各個部分之間協調工作的重要部件。控制部件主要負責指令地址的產生、流水線的控制以及處理各種相關、異常、中斷等工作,以保證數據通路的正常工作。控制部件的任務是非常艱巨的,沒有一個功能強大的控制部件,整個 DSP 處理器將無法正常工作。μDSP 的控制部件按照功能可以大致分為指令地址選擇邏輯、流水線控制邏輯、循環控制邏輯和中斷控制器等幾部分。

6.高速的運算單元

運算單元是 DSP 處理器的執行部件,是實現各種 DSP 算法的核心部分。所有算法的實現都是由運算單元的基本功能組合而成,所有的其他部件如控制部件、數據通路都是為運算單元服務的,為運算單元提供各種控制和充分的數據。μDSP 有 3 個功能強大的高速運算單元:算術邏輯單元(ALU),乘法累加單元(MAC),移位器(Shifter)。

處理器的設計是一個非常復雜的工作,體系結構的設計是處理器設計的靈魂,設計者面臨的任務非常復雜,要確定處理器的應用目標,針對應用目標需求判斷哪些特征是最重要的,然后在不超出成本的范圍內力求性能最高。

本文的創新點:主要對μDSP 的體系結構設計進行了詳細的闡述,對哈佛總線結構進行了改進,定義了六級流水線的名稱和功能,指出了特殊的指令系統應達到的要求,給出了μDSP 的體系結構的結構圖,并詳細介紹了一個數據地址發生器的設計等。