編者按:Cadence公司發布了突破性新產品Integrity 3D-IC平臺,該工具運用系統級思維,將設計規劃、物理實現和系統分析統一集成于單個管理界面中。設計工程師可以利用該平臺集成的熱、功耗和靜態時序分析功能,實現由系統來驅動的PPA 目標。日前,Cadence公司數字與簽核事業部產品工程資深群總監劉淼接受了記者專訪,詳細介紹Integrity 3D-IC的獨特之處。

過去10年,整個業界都在追求趨勢摩爾定律,硅材料的極限很難有突破的前提下,從2D走向3D的封裝技術,從系統角度出發推進了芯片的功耗和性能空間。

Cadence公司數字與簽核事業部產品工程資深群總監劉淼表示,2.5D和3D封裝技術使得芯片里或功能間的連線變短了,一方面降低了線上能量損失,另一方面減小了信號的延遲,從而獲得了低功耗和高性能。

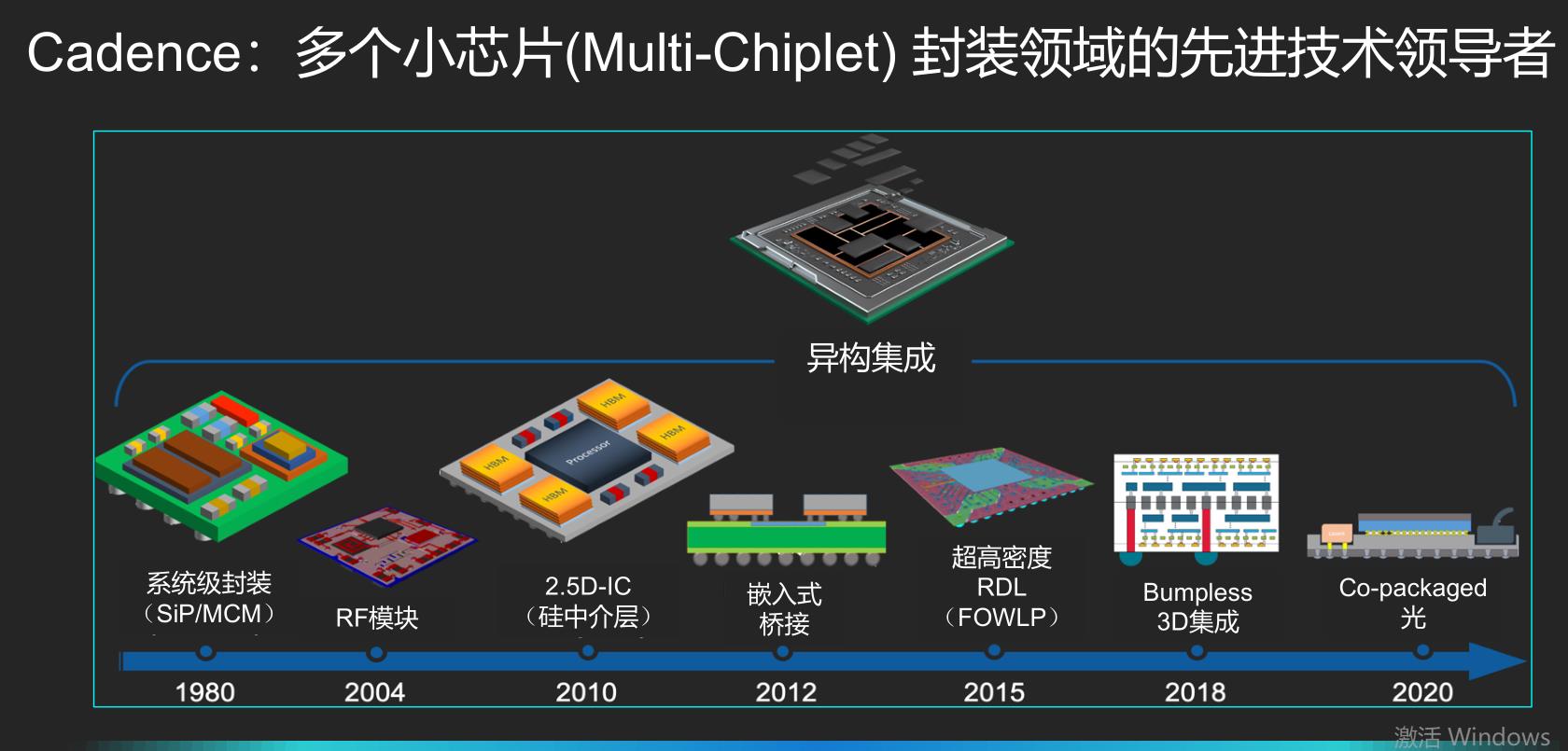

據劉淼介紹,Cadence在多芯片(Multi-Chiplet)封裝領域已經耕耘了20多年,從1980年就開始在做系統級的封裝,2004年做RF模塊,2010年研發2.5D封裝設計技術,2012年推出了嵌入式鍵橋技術,2015年推出了超高密度RDL(FOWLP),2018年的3D集成工具Bumpless,以及2020年的硅光集成工具Co-package。

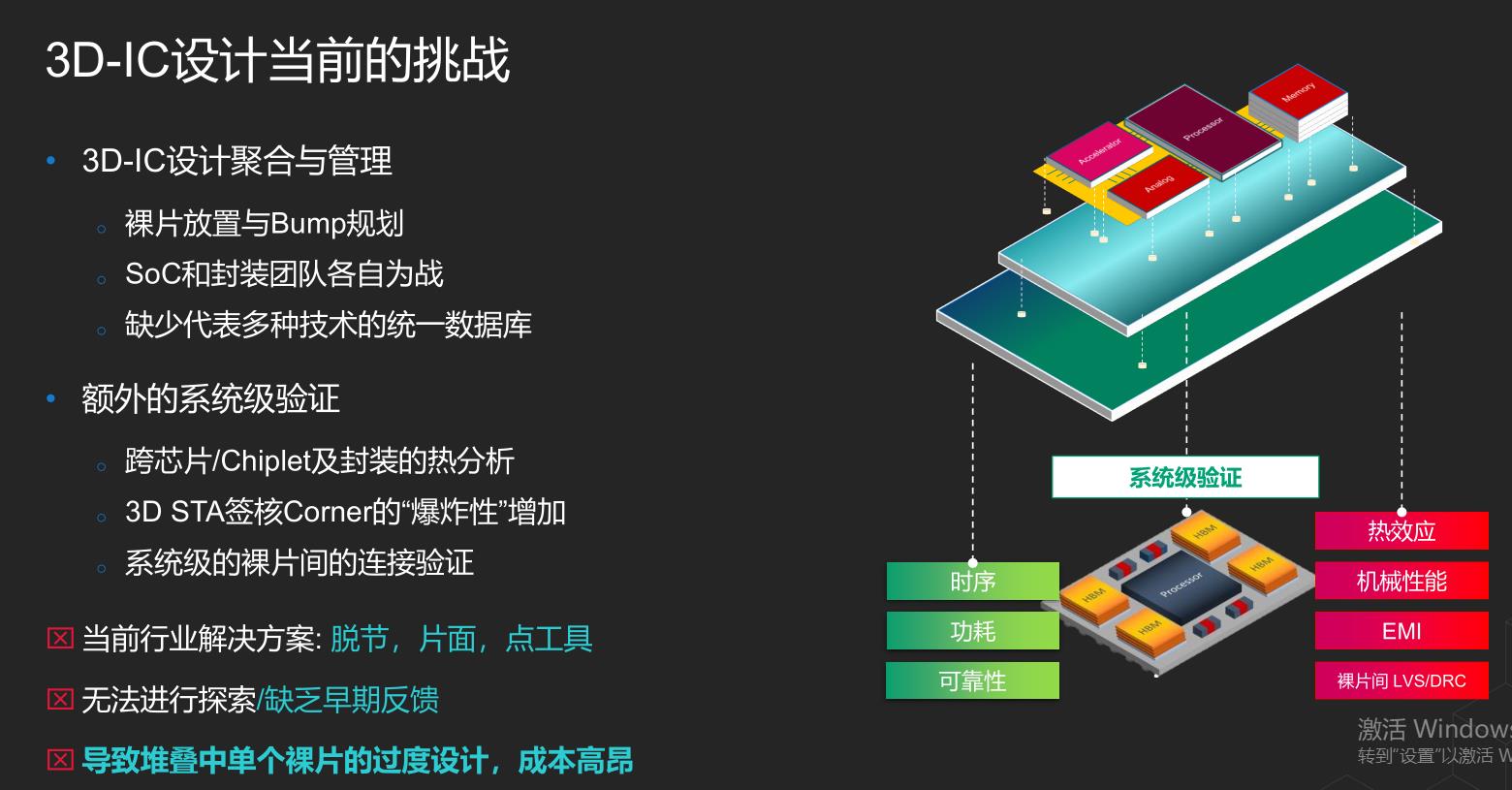

封裝技術向著3D進軍的過程中,設計師面臨著很多挑戰。

首先要進行Bump規劃,即討論嘗試找到芯片放置的最佳方案;其次,實現3D封裝要解決數字技術部分和模擬技術部分間的通訊和連接問題,這需要數字工程師和模擬工程師緊密協作,這里面有溝通效率的挑戰,第三個挑戰就是系統級驗證工作,這是一項需要調動更多設計部門參與的工作,比如跨芯片/Chiplet及封裝的熱分析和系統級裸片的連接驗證;第四是STA的簽核,3D封裝設計里的STA的簽核會有爆炸性的增加,2D時代的手工完成幾乎不可能。

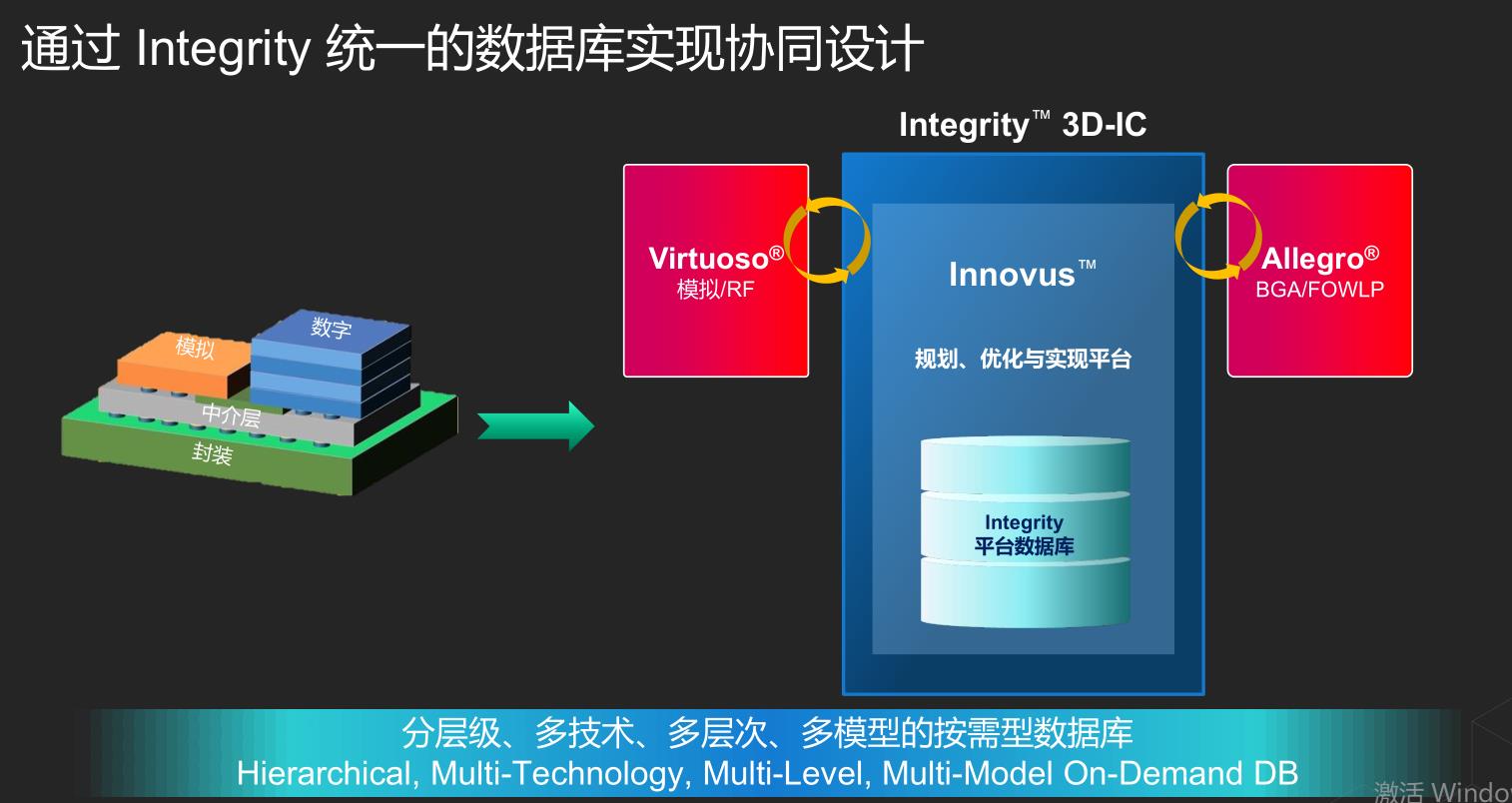

為了應對上述挑戰,Cadence公司最新推出Integrity 3D-IC開放平臺,這是一個跨集成電路全流程的平臺工具,橫跨芯片設計,芯片設計實現,以及到系統規劃、系統分析的全流程產品。

Intgrity 3D-IC平臺作為Cadence廣泛3D-IC解決方案的組成部分,在數字技術之上同時集成了系統、驗證及IP功能。

廣泛的解決方案支持軟硬件協同驗證,通過由Palladium ? Z2和Protium X2平臺組成的Dynamic Duo系統動力實現全系統功耗分析。

平臺同時支持基于小芯片的PHY IP互聯,實現面向延遲、帶寬和功耗的PPA優化目標。另外,Intgrity 3D-IC平臺支持與Virtuoso設計環境和Allegro技術的協同設計,通過與Quantus ExtractionSolution提取解決方案和Tempus Timing Signoff Solution時序簽核解決方案提供集成化的IC簽核提取和STA,同時還集成了Sigrity技術產品,Clarity 3D Transient Solver,及Celsius Thermal Solver熱求解器,從而提供集成化的信號完整性/功耗完整性分析(SI/PI),電磁干擾(EMI),和熱分析功能。

劉淼表示,全新Integrity 3D-IC平臺和更廣泛的3D-IC解決方案組合,建立在Cadence SoC卓越設計和系統級創新的堅實基礎之上,是Cadence公司能系統設計(Intelligent System Design)戰略的代表產品之一。