數(shù)字芯片設(shè)計(jì)驗(yàn)證經(jīng)驗(yàn)分享:將ASIC IP核移植到FPGA上

2024-08-12

作者:Philipp Jacobsohn,SmartDV首席應(yīng)用工程師 等線Sunil Kumar,SmartDV FPGA設(shè)計(jì)總監(jiān)

來源:智權(quán)半導(dǎo)體

本系列文章從數(shù)字芯片設(shè)計(jì)項(xiàng)目技術(shù)總監(jiān)的角度出發(fā),介紹了如何將芯片的產(chǎn)品定義與設(shè)計(jì)和驗(yàn)證規(guī)劃進(jìn)行結(jié)合,詳細(xì)講述了在FPGA上使用IP核來開發(fā)ASIC原型項(xiàng)目時(shí),必須認(rèn)真考慮的一些問題。文章從介紹使用預(yù)先定制功能即IP核的必要性開始,通過闡述開發(fā)ASIC原型設(shè)計(jì)時(shí)需要考慮到的IP核相關(guān)因素,用八個(gè)重要主題詳細(xì)分享了利用ASIC所用IP來在FPGA上開發(fā)原型驗(yàn)證系統(tǒng)設(shè)計(jì)時(shí)需要考量的因素。

在上篇文章中,我們介紹了將ASIC IP移植到FPGA原型平臺(tái)上的必要性,并對(duì)原型設(shè)計(jì)中各種考量因素進(jìn)行了總體概述,分析開發(fā)ASIC原型驗(yàn)證設(shè)計(jì)時(shí)需要考慮到的IP核相關(guān)因素,以及經(jīng)驗(yàn)分享的八大主題的第一主題“明了需求、發(fā)現(xiàn)不同”。本篇文章是SmartDV數(shù)字芯片設(shè)計(jì)經(jīng)驗(yàn)分享系列文章的第二篇,將繼續(xù)分享第二到第四主題,包括FPGA原型的基本概念、常見挑戰(zhàn)和基本調(diào)整。

作為全球領(lǐng)先的驗(yàn)證解決方案和設(shè)計(jì)IP提供商,SmartDV的產(chǎn)品研發(fā)及工程應(yīng)用團(tuán)隊(duì)具有豐富的設(shè)計(jì)和驗(yàn)證經(jīng)驗(yàn)。在國(guó)產(chǎn)大容量FPGA芯片和IP新品不斷面市的今天,SmartDV及其中國(guó)全資子公司“智權(quán)半導(dǎo)體”愿意與國(guó)內(nèi)FPGA芯片開發(fā)商、RISC-V IP和其他IP提供商、集成電路設(shè)計(jì)中心(ICC)合作,共同為國(guó)內(nèi)數(shù)字芯片設(shè)計(jì)公司開發(fā)基于本地FPGA的驗(yàn)證與設(shè)計(jì)平臺(tái)等創(chuàng)新技術(shù)與產(chǎn)品。

主題1:一款原型和最終ASIC實(shí)現(xiàn)之間的要求有何不同?

主題2:當(dāng)使用FPGA進(jìn)行原型設(shè)計(jì)時(shí)會(huì)立即想到哪些基本概念?

主題3:在將專為ASIC技術(shù)而設(shè)計(jì)的IP核移植到FPGA架構(gòu)上時(shí)通常會(huì)遇到哪些困難?

主題4:為了支持基于FPGA的原型,通常需要對(duì)ASIC IP核進(jìn)行哪些更改?

主題5:我們?nèi)绾未_保在FPGA上實(shí)現(xiàn)所需的性能?

主題6:在時(shí)鐘方面必須加以考量的因素有哪些?

Topic 7:如果目標(biāo)技術(shù)是FPGA,而不是ASIC,那么需要如何測(cè)試IP核的功能?

主題8:設(shè)計(jì)團(tuán)隊(duì)還應(yīng)該牢記什么?

主題2:在使用FPGA進(jìn)行原型設(shè)計(jì)時(shí)會(huì)用到哪些基本概念?

可重用性對(duì)IP核至關(guān)重要:這些內(nèi)核應(yīng)該盡可能使用通用RTL代碼來描述。這是確保用于ASIC實(shí)現(xiàn)的電路描述,也可以在原型設(shè)計(jì)環(huán)境中使用而無需進(jìn)行重大更改的唯一方法。這是非常重要的,因?yàn)樵驮O(shè)計(jì)的任務(wù)之一就是檢查RTL代碼的正確性。

實(shí)現(xiàn)中的任何偏差都會(huì)帶來風(fēng)險(xiǎn),使用通過ASIC邏輯綜合的RTL代碼來替換特定用于FPGA實(shí)例的時(shí)候,都會(huì)產(chǎn)生功能性錯(cuò)誤。使用盡可能完全相同的代碼庫(kù),就可以增加在原型設(shè)計(jì)期間已經(jīng)得到驗(yàn)證的功能在ASIC實(shí)現(xiàn)中加以保留的可能性。關(guān)于不可能總是避免特定于FPGA組件實(shí)例化的原因,我們將在接下來的主題4中進(jìn)行更詳細(xì)的討論:為了支持基于FPGA的原型,通常需要對(duì)ASIC IP核進(jìn)行哪些更改呢?

使用已經(jīng)在ASIC目標(biāo)架構(gòu)中經(jīng)過流片驗(yàn)證的IP核,并且之前也已經(jīng)被IP提供商成功移植到FPGA組件中,就可以提供巨大的優(yōu)勢(shì)。這意味著不僅創(chuàng)建電路所需的工作量可以大大減少,而且通過使用已經(jīng)在該領(lǐng)域被廣泛使用的預(yù)先定制電路組件,在ASIC流片后檢測(cè)出故障的概率也大大降低。在這種情況下,重要的是不僅可以重用純RTL代碼,而且還可以減少創(chuàng)建邏輯綜合和布局布線(P&R)設(shè)置腳本以及其他所需約束文件的工作量,因?yàn)檫@些通常與IP核一起提供。所有這些都可以大大簡(jiǎn)化IP核的集成。

其他有利于原型設(shè)計(jì)的標(biāo)準(zhǔn)是:1)FPGA的選擇和2)專用EDA工具的使用。原則上來說,通過選擇容量盡可能大且速度快的FPGA,或使用已經(jīng)商業(yè)化的預(yù)先定制的基于FPGA的原型設(shè)計(jì)開發(fā)板,都可以大大簡(jiǎn)化原型設(shè)計(jì)的工作。

圖2:Digilent Genesys 2 FPGA開發(fā)板是一個(gè)普遍適用的原型設(shè)計(jì)平臺(tái)的案例(圖片?Digilent)

將IP核集成到一個(gè)復(fù)雜的ASIC設(shè)計(jì)中,通常也帶來了在FPGA上實(shí)現(xiàn)相同功能的期望。必須在兩種用例之間做出區(qū)分:一方面,用于原型設(shè)計(jì)場(chǎng)景;另一方面,通過利用可重構(gòu)平臺(tái)來進(jìn)行物理驗(yàn)證,可支持在早期階段(即在可提供ASIC芯片之前)就對(duì)相關(guān)的固件和軟件進(jìn)行測(cè)試。

由于FPGA的可編程性,在電路驗(yàn)證中使用FPGA已成為既定的標(biāo)準(zhǔn)方法,即可通過迭代方法檢測(cè)和消除電路實(shí)現(xiàn)中的錯(cuò)誤。與純模擬手段相比,F(xiàn)PGA支持更多的測(cè)試周期,因此它可以發(fā)現(xiàn)和消除在純模擬性驗(yàn)證方法中可能難以發(fā)現(xiàn)的錯(cuò)誤。其結(jié)果是,驗(yàn)證覆蓋率得到了顯著的增加。由于驗(yàn)證要么是實(shí)時(shí)執(zhí)行的,要么是以稍微降低的時(shí)鐘速率執(zhí)行,甚至可以進(jìn)行長(zhǎng)期測(cè)試。

主題3:將專為ASIC技術(shù)設(shè)計(jì)的IP核移植到FPGA架構(gòu)時(shí)通常會(huì)遇到哪些困難?

與人們的假設(shè)相反,IP核的使用通常不是一個(gè)純粹的“即插即用”過程,即并不是通過使用標(biāo)準(zhǔn)化的組件,就可確保即刻可用的電路功能。如果目標(biāo)架構(gòu)是FPGA,則結(jié)果更是如此。相反,IP核的使用需要對(duì)各種參數(shù)進(jìn)行精確的規(guī)劃。非常重要的是,這里應(yīng)該特別考慮到許多IP核是專為ASIC而設(shè)計(jì)的,并且最初根本沒有打算將其移植到FPGA架構(gòu)上。

此外,IP核通常是為了滿足各種各樣的電路實(shí)現(xiàn)的要求而創(chuàng)建的。一個(gè)用戶可能需要內(nèi)核的某些特性,而另一個(gè)用戶可能需要不同的特性、設(shè)置或約束條件。這意味著IP核在其本身的實(shí)現(xiàn)期間就必須考慮所有可能的應(yīng)用場(chǎng)景,并且必須測(cè)試所有可能的配置。

需要考慮以下準(zhǔn)則:

在ASIC上實(shí)現(xiàn)的電路的運(yùn)行時(shí)鐘頻率通常可以比FPGA的時(shí)鐘頻率更高。因此,在FPGA實(shí)現(xiàn)中應(yīng)該只使用實(shí)際需要的特性。在使用IP核時(shí),如果使用參數(shù)化來創(chuàng)建相關(guān)的RTL代碼,并且這些代碼可以很容易地適應(yīng)各自的需求,這將帶來巨大的幫助。這也可以確保在沒有重大延遲的情況下提供所需的功能。

在某些情況下,仍然有必要降低FPGA的系統(tǒng)頻率(例如,降低到ASIC時(shí)鐘頻率的二分之一或十分之一)。特別是對(duì)于接口類IP來說,這可能是一項(xiàng)復(fù)雜的工作,需要對(duì)外設(shè)以及相關(guān)的軟件和固件進(jìn)行額外的更改。在創(chuàng)建功能時(shí),采取預(yù)防措施以降低系統(tǒng)時(shí)鐘速率對(duì)于IP供應(yīng)商來說是很重要的。

雖然諸如PHY這樣的模擬電路可以用在ASIC上,但將電路功能移植到FPGA上時(shí),情況并非如此。在某些情況下,模擬接口可以通過使用FPGA SerDes IO(在所有現(xiàn)代FPGA器件上通常都有提供)或高速收發(fā)器來實(shí)現(xiàn),或者通過創(chuàng)建一個(gè)數(shù)字“仿真PHY”來模擬,以消除對(duì)外部PHY設(shè)備的需求。然而,為了提供與ASIC功能相同的模擬PHY接口,基于FPGA的原型需要使用這種外部硬件組件。重要的是要確保IP和PHY之間接口的通信,這樣各個(gè)不同的組件之間不僅可以“交談”,而且還可以相互“理解”。

主題4:為了支持基于FPGA的原型,通常必須對(duì)ASIC IP核進(jìn)行哪些更改?

如前所述,IP核應(yīng)該使用通用的RTL代碼來描述。通用代碼的創(chuàng)建意味著應(yīng)該盡可能避免FPGA上諸如存儲(chǔ)、IO處理模塊、時(shí)鐘緩沖區(qū)等特定組件的實(shí)例化。這在某些領(lǐng)域是可能的,但由于各種不同原因并不總是能夠?qū)崿F(xiàn)。這樣做的原因有很多,這里的一個(gè)例子是使用內(nèi)存的實(shí)現(xiàn):

存儲(chǔ)組件。ASIC版本的RTL代碼可能包含從ASIC的單元庫(kù)中選擇的、用于實(shí)現(xiàn)的實(shí)例化內(nèi)存組件。這樣的實(shí)例并不能直接映射到FPGA中,因?yàn)镕PGA邏輯綜合工具不能理解ASIC庫(kù)文件;因此,來自單元庫(kù)的組件是未知的,導(dǎo)致FPGA工具流中形成黑盒。因此,不能夠?qū)⑦@種存儲(chǔ)組件直接映射到FPGA上提供的存儲(chǔ)結(jié)構(gòu)。專門為ASIC原型而設(shè)計(jì)的專用FPGA邏輯綜合工具可以讀取ASIC單元庫(kù),但此類工具成本極高,并且必須單獨(dú)購(gòu)買。如果ASIC RTL包含來自某家供應(yīng)商單元庫(kù)的實(shí)例(例如TSMC 28),有必要通過使用FPGA上提供的存儲(chǔ)結(jié)構(gòu)來建模一個(gè)存儲(chǔ)單元,該單元可提供與從ASIC單元庫(kù)中選擇的存儲(chǔ)單元具有相同的功能。

參數(shù)化法。由于IP核被用于各種各樣的應(yīng)用中,因此希望能夠用參數(shù)來進(jìn)行描述。例如,能夠從頂層控制整個(gè)IP核的存儲(chǔ)大小通常是有意義的。這使得根據(jù)用戶自己的需求來調(diào)整存儲(chǔ)單元的大小和限制FPGA資源的使用會(huì)變得容易。

寄存器陣列。ASIC版本的RTL代碼可能包含寄存器陣列,這些寄存器陣列在期望的配置中實(shí)現(xiàn)內(nèi)存功能。這樣的陣列通常不會(huì)被FPGA邏輯綜合工具識(shí)別為內(nèi)存,也不會(huì)映射到FPGA上可用的內(nèi)存中,而是通過使用寄存器實(shí)現(xiàn)。但是,如果寄存器被用于實(shí)現(xiàn)而不是專用內(nèi)存,則FPGA可實(shí)現(xiàn)的時(shí)鐘頻率可能會(huì)大大降低,因?yàn)榇鎯?chǔ)器實(shí)現(xiàn)需要大量的寄存器。在將大內(nèi)存描述為寄存器陣列的情況下,甚至可能無法將它們映射到FPGA上,因?yàn)镕PGA上可用的寄存器數(shù)量根本不足以實(shí)現(xiàn)。

所需的存儲(chǔ)單元。ASIC所需的存儲(chǔ)是專門為目標(biāo)應(yīng)用創(chuàng)建的。FPGA中一對(duì)一的映射將導(dǎo)致所用邏輯門的數(shù)量大大增加,從而導(dǎo)致可實(shí)現(xiàn)的時(shí)鐘頻率降低。因此,在FPGA中使用ASIC內(nèi)存通常是不可取的。一個(gè)例子是在對(duì)功能安全有特殊要求的安全關(guān)鍵型應(yīng)用中使用ASIC,這種應(yīng)用需要檢查存儲(chǔ)內(nèi)容的正確性和由于外部影響而可能發(fā)生的錯(cuò)誤。

例如,為了能夠糾正α粒子的影響和由此產(chǎn)生的單粒子翻轉(zhuǎn)(SEU),就需要實(shí)現(xiàn)糾錯(cuò)碼(ECC)電路。另一方面,在FPGA中提供的塊存儲(chǔ)器默認(rèn)具有這樣的電路,如果有需要就可以通過特殊的邏輯綜合功能屬性激活該電路。實(shí)現(xiàn)帶有額外邏輯的冗余電路幾乎沒有意義,同時(shí)也有可能因?yàn)榻M件片芯占用過高而無法達(dá)到所需的時(shí)鐘頻率。

圖3:ASIC和FPGA的存儲(chǔ)結(jié)構(gòu)不同,時(shí)鐘分配也有很大差異。使用鎖相環(huán)/數(shù)字鎖相環(huán)(PLL/DLL)電路可以簡(jiǎn)化這一點(diǎn),但是專有的PLL/DLL電路都需要從相應(yīng)的庫(kù)中實(shí)例化。

當(dāng)前所有的FPGA都包含PLL、DLL或兩者的組合。這些電路支持多項(xiàng)時(shí)鐘操作,如時(shí)鐘失調(diào)、頻率合成(例如,輸入時(shí)鐘頻率的除法或乘法)和占空比編程。輸入時(shí)鐘和輸出時(shí)鐘可以相位對(duì)齊。雖然在ASIC中有相應(yīng)的電路,但在功能上存在差異。如果需要PLL/DLL,則必須從FPGA制造商的相應(yīng)庫(kù)中對(duì)其實(shí)例化,并且必須確保時(shí)鐘分配方案適應(yīng)目標(biāo)FPGA架構(gòu)。

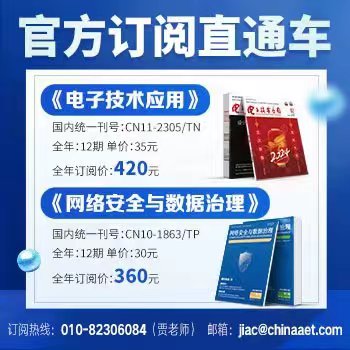

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<