2 月 26 日消息,三星電子 DS 部門 CTO 宋在赫(???)在上周于舊金山舉行的國際固態電路會議(ISSCC)上發表主題演講,并展示了其晶圓鍵合、低溫蝕刻和鉬應用等技術。

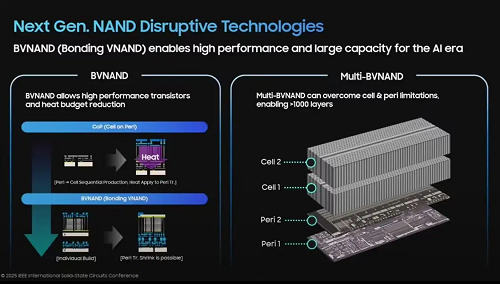

據介紹,這些技術將從 400 層的 NAND 閃存技術開始應用,而且他還提到,“鍵合技術可用于(在 NAND 區域)實現 1000 多層(堆疊)”。

注:晶圓鍵合是指分別制造外圍晶圓和單元晶圓,然后將它們鍵合在一起形成單個半導體。

宋部長當天還公開展示了 1000 層 NAND 的“Multi-BV NAND”結構 PPT(上圖),堆疊四片晶圓(2+2)以打破結構限制。實際上,早在 2022 年于硅谷舉行的“2022 年三星技術日”上,三星就承諾將在 2030 年之前開發出 1000 層 NAND。

當然,三星電子并不是唯一一家研究這些結構的公司。全球第二大 NAND 閃存企業鎧俠也在研究類似的“多棧 CBA (CMOS directly Bonded to Array)”,其目標是到 2027 年開發出 1000 層 3D NAND。

長江存儲則將該技術命名為“Xtacking”,且早在 100 層以下的產品就已經開始應用,而長江存儲目前正在量產 270 層的 NAND 閃存。據 ZDNet 周一報道,三星將為此與長江存儲建立合作關系。

據 ZDNet 報道,三星之前在 NAND 生產上使用的是 COP(Cell on Peripheral)方法,其中外圍電路被放置在一個晶圓上,并且單元堆疊在頂部。然而,隨著層數的增加,下層外圍的壓力會影響可靠性。

業內人士表示,在單個晶圓上僅通過單元堆疊的方式最多可堆疊約 500 層 NAND,要想實現三星承諾的 1000 層 NAND 則不可避免地用到多片晶圓。

除晶圓鍵合技術外,三星還展示了為下一代 NAND 的大批量量產而準備的低溫蝕刻和鉬沉積等創新技術。

低溫蝕刻預計將用于 400 層或以上的 NAND 通孔,目前東京電子(TEL)與 Lam Research 正在開發相關設備。

低溫蝕刻設備最大的特點是能夠在極低的溫度下保持高速蝕刻,從而減少 NAND 蝕刻期間的堆疊問題。對此,三星電子和 SK 海力士分別壓鑄于 TEL 設備和 Lam Research 設備。

三星還準備為字線(與晶體管源極部分連接的線路,負責讀取和寫入)材料引入鉬(Mo)元素,以此取代鎢(W)和氮化鈦(TiN)材料,從而大幅降低晶體管的“電阻率”。

業內人士表示:“通過鎢可以減少的層高已經達到極限。如果使用鉬則可以進一步減少 30% 至 40%。目前,TEL 和 Lam 同樣也在這一領域進行競爭,而 Lam 公司已經向三星電子提供了多臺鉬沉積設備。

材料業界人士表示:“隨著新技術的應用,繼設備市場之后,材料市場也將經歷一場大動蕩。從新一代 NAND 閃存開始,不僅是前驅體,蝕刻液劑、動力氣體等也將迎來大量變革。”