1 引 言

邏輯分析儀的測試對象是數字系統中的數字信息[1]。為了滿足現代數據域的檢測要求,邏輯分析儀應具有高的采樣速率和足夠多的輸入通道。本文基于虛擬儀器的概念,主要論述以PC586為基礎400MHz/102通道邏輯分析儀設計原理和方法,重點闡述系統控制電路設計和系統軟件設計。

2 虛擬邏輯分析儀體系結構

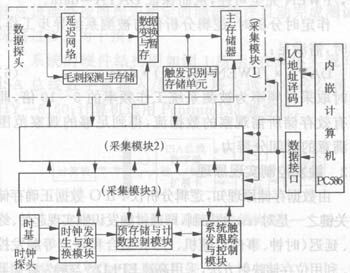

圖1為PC環境下的400MHz/102通道虛擬邏輯分析儀控制與采集系統總體構成原理框圖,主要包括數據采集、探頭、觸發跟蹤、時序變換與生成,測試接口等部分。該系統輸入采集由3個模塊構成,每個模塊有32個數據通道(另附加2個時鐘通道),采用完全相同的功能結構。第3個模塊附加了時鐘輸入與輸出、控制等功能。采用該結構的主要原因,一是避免主采集板過大,元件過密造成散熱方面的困難(因高速工作的器件較多),二是系統結構靈活,可以根據需要選32、64、96路組態方式。

該邏輯分析儀的控制和管理、數據處理以及數據顯示盧內嵌計算機完成。因此,系統硬件的設計主要集中在高速數據捕獲以及與微機的接口,而軟件設計主要在系統管理、數據的后處理及數據顯示。

圖1 400MHz/102通道虛擬邏輯分析儀原理框圖

3 系統硬件設計

400MHz/102通道虛擬邏輯分析儀中的高速數據捕獲是由控制電路完成觸發控制、數據存取控制而實現的,控制電路同時實現與微計算機的接口。

3.1 數據存儲原理

作狀態分析時,邏輯分析儀與被測系統同步工作。為了使存儲器存儲的狀態數據與被測系統運行的數據流一致,則應滿足:

DATA*/FWEN=f(sclk,trw,dtc)*data (1)

式(1)中,DATA為邏輯分析儀存儲的數據;/FWEN為邏輯分析儀主要存儲器FIFO的寫使能控制;sclk為狀態(外部)時鐘;trw為觸發字;dtc為數據控制;data為被測系統數據。由式(1)知下式:

DATA=data (2)

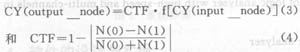

成立的條件是/FWEN信號與sclk、trw、dtc信號必須符合嚴格的關系。根據數字系統可測性設計中可控性理論,應用CAMFLOT[2]法(Computer Aided Measure For Logic Testability),有:

式(3)~(4)中,CY為可控程度,其值ε(0,1);CTF為可控傳遞因子;N(0)、N(1)為在電路輸入端加所有不同輸入值時,電路輸出端出現“0”和“1”的總次數。由式(3)知,當可靠置位sclk、trw、dtc等控制信號,可計算出:

CY(/FWEN)=1 (5)

即,/FWEN完全可控,從而保證DATA=data。

作定時分析時,邏輯分析儀與被測系統異步工作。此時,需滿足:

DATA*/FWEN=f(trw)*data (6)

同時取采樣頻率為被測系統工作頻率的5~10倍,即可有效存儲所需觀察的數據流,得到足夠的觀察范圍和滿意的時間分辨力。

3.2 觸發控制實現原理

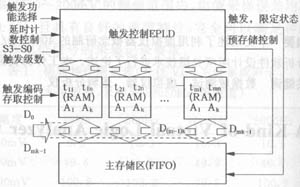

由數據存儲原理知,邏輯分析儀FIFO數據正確存儲的關鍵之一是對trw的控制,即通過觸發識別實現起始、終止、延遲(時鐘、事件)、隨機、序列、組合和限定等觸發控制。利用位存儲映射方法,采用高速EPLD[3]與觸發存儲器結合,設計的實現觸發控制的原理框圖如圖2所示。

圖2中,D0~Dmk-1為被測數據。觸發RAM數據位寬為n,地址寬度為k,個數為m,故可觀測的數據流的寬度為m·k。當k≥n時,最大序列觸發或組合觸發識別級數L為:L≦2n-1 (7)

圖2 觸發控制實現原理框圖

4 系統軟件設計

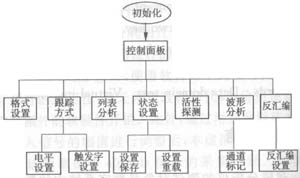

利用圖像界面操作系統Windows和以Windows為基礎的可視化程序設計平臺C++Builder,軟件由15個窗體加5個單元文件組成,各主要窗體之間的關系如圖3所示。

圖3 系統軟件各窗體及相互關系

5 結束語

邏輯分析儀結構復雜,技術要求高。本文所述的基于虛擬儀器概念的設計思想和方法,因部分硬件功能軟化而使硬件電路大為簡化,同時采用了EPLD器件,從而降低了儀器成本,提高了儀器的可靠性和性能,且功能易于擴展。400MHz/102通道邏輯分析儀已于2000年12月28日通過了信息產業部軍工預研局主持的技術鑒定。