CPCI總線簡介

CPCI總線是一個開放式、國際性技術(shù)標準,由PCI總線工業(yè)計算機制造商組織PICMG(PCI Industrial Computer Manufacturer Group)負責制定和支持。CPCI總線具有嚴格的標準和規(guī)范,保證其具有良好的兼容性,支持多種處理器和操作系統(tǒng),符合CPCI規(guī)范的擴展卡可插入任何CPCI系統(tǒng)并可靠地工作。CPCI標準將外設(shè)組件互連(PCI)標準特性與支持嵌入式應(yīng)用的堅固機械外形完美結(jié)合在一起,其性能特征是專門針對工業(yè)環(huán)境而量身定制的。簡單的說:CPCI總線=PCI總線的電氣規(guī)范+標準針孔連接器+歐洲卡規(guī)范。CPCI基于ICMG2.0規(guī)范,其電氣特性與PCI總線相同,因此用戶的軟件和普通PC機兼容,現(xiàn)有的PCI外圍卡也可以很容易地移植到CPCI平臺上。CPCI使用高密度針孔總線連接器,和使用金手指連接器的PCI卡相比,具有連接更可靠,完全氣密的特點,模塊的抗震性和抗腐蝕性高。CPCI還支持熱插拔,即可在不關(guān)機狀態(tài)下插入或取出板卡。熱插拔的優(yōu)點在于能增強系統(tǒng)性能或診斷系統(tǒng)故障而無需關(guān)閉系統(tǒng),這對很多應(yīng)用來說十分重要。

另外,CPCI在32位/33MHz系統(tǒng)中能夠提供132MB/s的背板傳輸能力,在64位/66MHz系統(tǒng)配置情況下的性能為528 MB/s。在對帶寬要求高的場合CPCI具有很強的優(yōu)勢。

除了上述所有的優(yōu)點,CPCI還具有非技術(shù)性的優(yōu)勢,即經(jīng)濟實用、可快速推向市場以及高可靠性。所以,在當今的工控、通信、軍事等諸多要求高可靠性領(lǐng)域中CPCI總線已經(jīng)取代了ISA、STD等其它總線,成為主流總線形式。

C PCI系統(tǒng)硬件方案概述

CPCI系統(tǒng)由機箱、電源、總線背板和功能單元組成。一般而言,CPCI機箱內(nèi)部就帶有電源和總線背板,其中CPCI總線背板如圖1所示。

CPCI系統(tǒng)最多能加載的CPCI功能單元數(shù)取決于機箱所能提供的槽數(shù)n:一個CPCI系統(tǒng)由1個系統(tǒng)槽和(n-1)個外圍槽組成。在CPCI系統(tǒng)中,系統(tǒng)槽為系統(tǒng)提供仲裁、時鐘、中斷和復位功能,這些信號對總線上所有的功能單元起作用。

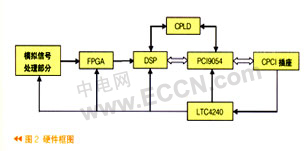

在這個CPCI系統(tǒng)中,我們研制的實際上是一塊功能單元板,其硬件框圖如圖2所示。

由于數(shù)字信號處理部分計算量大,且實時要求高,我們采用了FPGA和DSP協(xié)同處理數(shù)據(jù)的方案。在數(shù)字信號處理時,低層的信號預(yù)處理算法處理的數(shù)據(jù)量大,對處理的速度要求高,但運算結(jié)構(gòu)相對簡單,因而適于用FPGA進行硬件實現(xiàn),相比之下,高層處理算法所處理的數(shù)據(jù)量相對較小,但算法的控制結(jié)構(gòu)復雜,適于用運算速度高、尋址方式靈活、通信機制強大的DSP芯片來實現(xiàn)。

CPCI總線控制以及通信協(xié)議十分復雜,一般需要選用專門的處理芯片。我們這里選用了PLX公司的PCI9054芯片,而電源管理選用了凌力爾特公司的LTC4240芯片。

CPCI總線接口設(shè)計

PCI總線接口的實現(xiàn)

設(shè)計PCI接口的實現(xiàn)通常有兩種方法:一種是用可編程器件FPGA或CPLD,另一種是用專用PCI接口芯片。二者各有優(yōu)缺點:利用可編程器件自行設(shè)計PCI接口邏輯,可以根據(jù)具體的應(yīng)用需要,優(yōu)化接口邏輯,靈活性是該方法最大的特點,且接口邏輯也可獲得較高的性能。但是由于PCI協(xié)議比較復雜,在具體的實現(xiàn)中也相當困難,并且各種邏輯關(guān)系驗證起來也很麻煩,有時會得不償失,把簡單的設(shè)計變得復雜化了;而利用專用芯片來實現(xiàn)PCI總線接口是一種能夠解決設(shè)計難點的有效方法。但是這種芯片必須具有較低的成本和通用性,而不限于插卡一側(cè)的特定處理器總線,能夠優(yōu)化數(shù)據(jù)傳輸,提供配置空間,具備片內(nèi)FIFO功能(用于突發(fā)性傳輸)等。目前,很多半導體器件公司提供這類專用芯片。如PLX開發(fā)的PCI9030、PCI9054 和AMCC開發(fā)的接口芯片S5933等。

比較以上兩種實現(xiàn)PCI接口的方案可知,用可編程邏輯器件能夠較靈活地實現(xiàn)所需要的功能,但為了達到PCI指標的苛刻要求,需要做大量的邏輯驗證和時序分析工作。采用PCI專用芯片,可以比較容易地實現(xiàn)PCI接口,大大縮短開發(fā)時間,當然,由于廠家設(shè)計芯片時對通用性的考慮,在用戶需要的某個方面可能不是最好的,但綜合性能方面,采用專用芯片要比用可編程器件設(shè)計好得多。

我們最終選用了PLX公司的PCI9054芯片。

PCI9054是PLX公司生產(chǎn)的PCI總線通用接口芯片,采用先進的PLX數(shù)據(jù)管道結(jié)構(gòu)技術(shù),符合PCIV2.1和V2.2規(guī)范。提供了兩個獨立的可編程DMA控制器。每個通道均支持塊和分散/集中的DMA方式:在PCI總線端支持32位/33MHz;本地端(local bus)可以編程實現(xiàn)8、16、32位的數(shù)據(jù)寬度,傳輸速率最高可達132MB/s。

PCI9054與DSP的接口

PCI9054作為一種橋接芯片在PCI總線和LOCAL總線之間提供傳遞消息,既可以作為兩個總線的主控設(shè)備去控制總線,也可以作為兩個總線的目標設(shè)備去響應(yīng)總線。其本地總線可工作在M,C,J三種模式:M模式是專為Motorola公司的MCU設(shè)計的工作模式。C模式下9054芯片通過片內(nèi)邏輯控制將PCI的地址線和數(shù)據(jù)線分開,很方便地為本地工作時序提供各種工作方式,一般較廣泛應(yīng)用于系統(tǒng)設(shè)計中。J模式是一種沒有Local Master的工作模式。它的好處是地址數(shù)據(jù)線沒有分開,嚴格仿效PCI總線的時序。

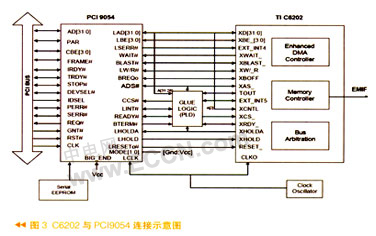

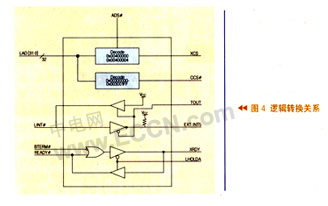

由于DSP我們采用了TI公司的C6202,考慮到與DSP的擴展總線進行接口,PCI9054的LOCAL總線選用了J模式。其連接如圖3所示。

這種連接方式十分方便,幾乎不需要加多少改動,兩塊芯片就能互相通信。其部分引腳的邏輯轉(zhuǎn)換關(guān)系如圖4所示。

熱插拔電路設(shè)計

CPCI總線不同于PCI總線的最大特點是支持熱插拔(Hot Swap)。

熱插拔技術(shù)概述

CPCI熱插拔技術(shù)的基本目的是在系統(tǒng)正常工作的同時,CPCI總線上插入或拔出插件板,完成故障插件板的更換與計算機系統(tǒng)的重新配置。熱插拔技術(shù)主要分為三種處理過程:

1)物理連接過程

熱插入——在工作著

CPCI總線上加入插件板。

熱拔出—— 在工作著

CPCI總線上移走插件板。

2)硬件連接過程

計算機系統(tǒng)在硬件上的電氣連接與斷開。

3)軟件連接過程

計算機系統(tǒng)在軟件上的連接與斷開。

這些連接過程在系統(tǒng)中雖屬于不同的連接層,但是彼此相互關(guān)聯(lián)。例如:當物理連接不存在時,硬件連接層就不能產(chǎn)生電氣連接。而插件板從計算機系統(tǒng)的CPCI總線上拔出后,軟件與硬件連接將自動斷開。

熱插拔芯片介紹

LTC4240熱插拔控制器是凌力爾特公司研制的針對CPCI總線的熱插拔控制器,它使線路板能夠在帶電的CPCI總線插槽中安全地插入或拔出,能控制全部4個CPCI電源,它使用兩個外部N溝道晶體管控制3.3V和5V電源,而±12V電源則由兩個片上開關(guān)管調(diào)節(jié)。電子斷路器對所有4個電源進行過流保護,“電源良好”輸出信號表明所有電源電壓都在正常容限之內(nèi),另外,LTC4240有個內(nèi)置的I 2 C總線兼容接口,從而可用軟件控制和監(jiān)視器件功能及電源狀態(tài)。它還使用戶能夠開啟或關(guān)閉器件、置位RESETOUT、開啟狀態(tài)LED指示驅(qū)動器以及不受±12V電源故障的影響。這個器件還可為I/O引腳提供預(yù)充電偏壓.以及通過將PCI_RST信號和HEALTHY信號整合來產(chǎn)生LOCAL_PCI_RST信號.并能滿足PCI定時要求,且不需要外部邏輯電路。其典型應(yīng)用如圖5所示。

LTC4240工作過程

1)板卡插入過程

當板卡插入背板時,在CPCI接插件的防護地連接上,板卡上可能存在潛在的對地電壓放電。該熱插拔板將首先接觸到背板插件的長針(+5V和地),即LTC4240的VCC管腳被加電,將對其后端電路進行復位以關(guān)斷VGATE3/5輸出,從而禁止外部MOSFET管工作,并輸出1V參考電壓,此1V參考電壓對還未接觸到背板的I/O管腳加電,同時PWRGD#的輸出將被置高,接著I/O管腳接觸到背板插針上,BD_SEL#管腳被主機置低,以確認板卡已經(jīng)被正確的插入,此時LTC4240控制的上電順序開始。LTC4240通過控制VGATE3/5的輸出來打開外部的MOSFET功率管。板卡上的電路都保持在復位狀態(tài),直到5和3V電源電壓穩(wěn)定,而且內(nèi)部復位時間計時器達到一定時間時,復位信號停止,板卡進入正常操作過程。

在正常工作過程中,LTC4240將持續(xù)監(jiān)控板卡的后端電壓,一旦電壓超過關(guān)斷電壓閾值,LTC4240將控制PWRGD#輸出為低,以使主機檢測到該信號并指示板卡電源有問題。

2)板卡拔出過程

板卡拔出時,首先將BD_SEL#與地斷開,LTC4240則立即關(guān)斷VGATE3/5輸出,并改變PWRGD#的狀態(tài),同時將LOCAL_PCI_RST#輸出置低,并將總線I/O接口電路置為高阻態(tài),這時電源依舊對I/O腳加電,以使總線從激活狀態(tài)平穩(wěn)轉(zhuǎn)為非供電狀態(tài)。一旦I/O腳與背板插針斷開,板卡上的電路和LTC4240將通過最后斷開的長針進行最后的放電過程。

寄存器配置

設(shè)計好接口電路后,硬件設(shè)計工作還只完成了一半。由于PCI9054是通用PCI接口功能芯片,它的功能還不一定能夠滿足用戶的需求,所以還要進行功能寄存器設(shè)置以使接口電路具有特定的功能。寄存器的配置包括EEPROM初始化、LOCAL功能寄存器和PCI配置寄存器的配置。

1)EEPROM初始化

在計算機的加電自檢期間,PCI總線的RST#信號復位,PCI9054內(nèi)部寄存器的默認值作為回應(yīng)。PCI9054輸出本地LRESET#信號并檢測串行EEPROM。如果串行EEPROM中的前33個比特不全為1,那么PCI9054確定串行EEPROM非空,用戶可通過向PCI9054的寄存器CNTRL的29位寫1來加載EEPROM的內(nèi)容到PCI9054的內(nèi)部寄存器,配置的信息(設(shè)備識別號、供應(yīng)商代碼號、Local總線三個空間的大小以及三個空間的基址等)事先要利用編程器寫入配置存儲器中,也可以在主機的專用程序中對EEPROM進行配置。

2)PCI配置寄存器的配置

配置PCI配置寄存器比較簡單。主要是填寫生產(chǎn)商ID號、器件ID號、類碼子系統(tǒng)ID號和子系統(tǒng)生產(chǎn)商ID號。

3)本地配置寄存器的配置

對 于本地配置寄存器的配置就是對本地地址空間及其本地總線屬性的配置。這些配置要根據(jù)實際開發(fā)的硬件板卡的硬件資源進行配置。

設(shè)備驅(qū)動程序的設(shè)計

在完成上述工作以后,還需在主控板(相當一臺高性能計算機)上完成設(shè)備驅(qū)動程序。其關(guān)鍵是如何完成硬件操作,基本功能是完成設(shè)備的初始化、對端口的讀寫操作、中斷的設(shè)置和響應(yīng)及中斷的調(diào)用,以及對內(nèi)存的直接讀寫。在windows下有很多驅(qū)動程序開發(fā)環(huán)境,只需根據(jù)硬件的具體情況,很方便就能完成驅(qū)動程序的編制。

結(jié)束語

我們研制的設(shè)備實際上是一個通用硬件平臺,通過加載不同軟件,它需要完成很多復雜信號的檢測、解調(diào)等功能,由于受到硬件運算速度、存儲量等資源限制,這些信號處理僅靠底層的硬件電路(如DSP、FPGA)將很難滿足要求,這就需要傳給主控板處理;另外,考慮到應(yīng)用的場合,CPCI總線系統(tǒng)很適合我們的要求,其接口設(shè)計就成為十分重要的部分,需要從軟硬件兩個方面全盤考慮、精心設(shè)計,才能達到預(yù)期目標。