摘 要: 給出了高速采集" title="高速采集">高速采集系統的實現架構及控制原理,并在分析數據采集系統現狀的基礎上,針對高速采集系統存在的采集和傳輸速度" title="傳輸速度">傳輸速度、資源利用不合理以及硬件成本偏高等問題,給出了一種共享總線、同步采集、分時讀取的方法。實踐表明,采用該方法提高了系統的采集和傳輸速度,實現了對多通道、高分辨率并行A/D" title="A/D">A/D同步采集的有效控制,節省了FPGA系統資源,降低了硬件成本。

關鍵詞: 高速采集 FPGA 分時操作

工程應用中經常需要對一些具有長時間域、瞬變特征的信號進行檢測,由于信號波形具有時域位置不確定等特點,特別在航天測控、故障診斷、定位等系統中,所以往往還需要同時對多個參數進行采集[1~3]。一般暫態過程中還有豐富的有用信息,能夠為故障診斷、失效分析等提供有力的理論依據;連續大容量數據信息對于趨勢預測、壽命診斷、檢測以及系統參數估計和辨識具有重要的意義。因此,這對數據采集、存儲和傳輸速度及精度提出了較高要求。由于一般處理器主頻和資源的限制,無法達到高速數據采樣、高分辨率、大數據量存儲的目的;DSP等高性能處理器雖然可以滿足一定場合的高速采集的需要,但過于頻繁的中斷使CPU效率降低,響應速度變差。

目前,一般采用CPLD 或FPGA直接控制A/D轉換的方式達到高速采集的目的。但采用CPLD或FPGA控制A/D轉換的很多應用中,同樣存在一些問題,主要為一般都外掛數據緩沖區,降低了系統的傳輸速度,同時增加了硬件成本[4];另外對于高精度、多通道、并行轉換A/D系統,使得接入FPGA的管腳數增多,這樣造成FPGA等系統資源的嚴重浪費和成本的增加。本文給出了一種共享總線、同步采集、分時讀取的方法,提高了系統采集和傳輸速度,達到對多通道、高分辨率并行A/D同步采集的有效控制,合理利用了FPGA系統資源,降低了硬件成本。

1 系統基本原理與設計

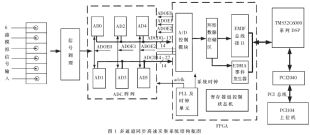

多通道同步高速采集系統結構如圖1所示[5]。由圖1可知,系統主要包括信號調理、A/D數據采集與控制、數據傳輸存儲、EMIF總線接口、DSP部分以及PCI接口等。6路輸入模擬信號經過信號調理電路后送入A/D轉換器,數據經A/D控制單元存入FPGA內部緩沖區,由EMIF接口模塊送至DSP外部存儲區,最后經PCI總線上傳給PCI104上位機。

1.1 基本原理

總線共享、同步采集、分時讀取的方法主要是借鑒了分時操作系統的思想,按照時間片對A/D轉換結果進行輪循讀取。從圖1可知,在硬件設計上,6路A/D轉換器共享采樣時鐘信號" title="時鐘信號">時鐘信號adclk、讀寫控制信號adwr、片選信號adcs;AD1、AD3、AD5共享一路數據總線ADCD14~27,AD0、AD2、AD4共享另一路數據總線ADCD0~13;AD0、AD1共享輸出使能信號ADOE0、AD2、AD3共享輸出使能信號ADOE1,AD4、AD5共享輸出使能信號ADOE2。6路A/D轉換器共享采樣時鐘信號adclk、片選信號adcs保證了采樣的同步問題,共享數據總線節約了FPGA管腳,合理利用FPGA資源,通過分別使能ADOE信號,在A/D轉換完成后數據有效的時間內,分時讀取轉換結果,達到了并行采集的目的;不同數據總線的2路A/D轉換器共享OE信號,保證在同一時間片內并行讀取2路A/D轉換結果。

1.2 A/D數據采集與控制

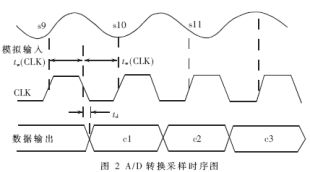

本文使用TI公司的THS1408 A/D轉換芯片。THS1408具有14bit分辨率,最高采樣速率達到8 MSPS,采用流水線結構,14位并行接口[6]。本文最高采樣頻率為5MHz,并行采集6路模擬電壓或電流信號。A/D轉換采樣時序如圖2所示,在CLK為高電平的半個時鐘周期加上td(輸出延時時間)的時間內,轉換后的數據都是有效的。因此,在CLK為高電平的半個時鐘周期內,讀取轉換結果是最穩定和可靠的。

?

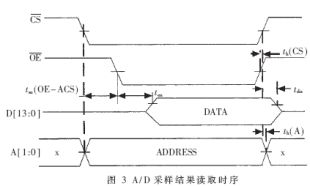

圖3為A/D采樣結果讀取時序,其中, 為片選信號,低電平有效;

為片選信號,低電平有效; 為輸出激活信號,低電平有效;D[13:0]為雙向數據總線;A[1:0]為地址輸入信號,可尋址四個地址,其中0地址存放轉換結果,另外三個地址為控制、增益設定和偏移設定寄存器;tsu(OE-ACS)為地址以及片選建立時間,要求最小為4ns;ten為輸出使能時間,最大為15ns;tdis為輸出關斷時間,典型值為10ns;th(A)為地址保持,最小為1ns;th(CS)為片選保持時間,最小為0ns。從圖2和圖3可以得出,完成A/D采樣和讀取控制的步驟如下:

為輸出激活信號,低電平有效;D[13:0]為雙向數據總線;A[1:0]為地址輸入信號,可尋址四個地址,其中0地址存放轉換結果,另外三個地址為控制、增益設定和偏移設定寄存器;tsu(OE-ACS)為地址以及片選建立時間,要求最小為4ns;ten為輸出使能時間,最大為15ns;tdis為輸出關斷時間,典型值為10ns;th(A)為地址保持,最小為1ns;th(CS)為片選保持時間,最小為0ns。從圖2和圖3可以得出,完成A/D采樣和讀取控制的步驟如下:

(1)首先,為ADC提供采樣時鐘信號CLK;

(2)在CLK時鐘信號上升沿,使片選信號 有效,地址信號A[1:0]輸出為0,使輸出激活信號

有效,地址信號A[1:0]輸出為0,使輸出激活信號 有效;

有效;

(3)至少延時tsu(OE-ACS)+ten=19ns;

(4)從數據總線D[13:0]讀取轉換結果;

(5)使片選信號 無效,

無效, 無效。

無效。

2 環形隊列數據存儲" title="數據存儲">數據存儲與控制

本文在FPGA內部采用環形隊列結構,用于暫存采集數據,并采用乒乓方式切換數據存儲區,提高數據傳輸和數據暫存的可靠性。定時觸發DSP的EDMA(Enhanced Direct Memory Access)事件,通過EMIF(External Memory Interface)總線接口完成高速數據傳輸。環形隊列內存要求較小,不易丟失數據,控制邏輯復雜,采用乒乓方式觸發數據傳輸事件,保證了采樣和傳輸的不間斷進行。

3 FPGA的邏輯控制功能的實現

采用Xilinx Spartan-II E系列40萬門FPGA完成邏輯控制功能,主要包括采集時鐘處理、6路并行A/D采集與控制、數據存儲與傳輸控制、與DSP的EMIF接口、EDMA事件觸發控制等。

3.1 A/D控制模塊

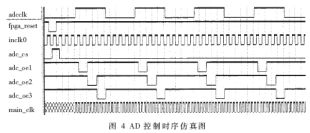

通過上面對A/D控制分析可以知道,在采樣時鐘CLK為高電平的半個時鐘周期內,讀取轉換結果是可靠和穩定的,由于片選、地址建立時間以及輸出激活時間的要求,在5MHz時鐘信號的半個周期內,以共享總線方式可以控制三路A/D轉換器,那么通過兩路總線,就可以完成對六路并行數據的采集。圖4為三路A/D轉換器共享數據總線的控制時序圖,采用ModelSim仿真工具完成。其中,adcclk為A/D采樣時鐘;inclk0為外接時鐘,經過PLL輸出main_clk作為系統的主時鐘,時鐘周期為10ns;adc_oe1、 adc_oe2、adc_oe3為三路A/D輸出使能信號,通過分時有效的方法,讀取各路A/D轉換結果,每個時間片長度為30 ns;adc_cs為A/D片選信號,該信號建立需要一定時間,為實現多路A/D并行采樣,將六路A/D片選信號連接在一起,一直有效;fpga_reset為FPGA復位信號。

3.2 環形數據存儲模塊

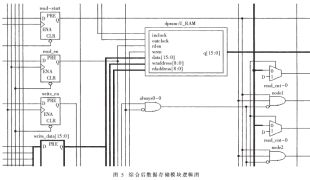

FPGA內部通過將雙口RAM與地址控制器結合構成環形隊列數據存儲模塊,數據存儲器大小為16KB,每136.53μs觸發一次DSP的EDMA事件,經過EMIF數據總線,將采集數據存儲到DSP的外部存儲器SDRAM中,當有異常發生時,通過PCI總線上傳到PCI104存儲介質中。圖5為FPGA綜合后的數據存儲模塊邏輯圖,通過對地址模塊和雙口RAM的讀寫達到對數據的有效存儲和傳輸。

4 實驗數據與波形

圖6為實測其中一路A/D控制的時序圖,A路為A/D輸出使能信號,在每個采樣時鐘的上升沿有效,有效時間為30ns;B路為5MHz采樣時鐘信號。圖7為實際捕獲的瞬變信號圖形,圖8為漸變信號變化的實測圖形。由于系統具有較高的采樣速率,高速的數據傳輸和大容量的數據存儲能力,無論是對瞬態變化的信號,還是漸變信號的特征,都可以達到捕捉的目的。

?

系統采用FPGA實現邏輯控制、數據傳輸的功能,將數據緩沖部分在FPGA內部實現,提高了存儲、讀取速度,節省了硬件成本;采用分時操作系統思想,以共享總線的方式,完成對多路A/D同步采集的功能,合理利用了資源、節省了硬件成本。實踐證明,該系統可以滿足多通道高速采集、大數據存儲的要求。

參考文獻

1 曾祥君, 尹項根, 陳 浩等. 電力系統暫態過程同步記錄的研究. 電力系統及其自動化學報, 2001;(1)

2 劉蘇宜, 王國榮, 郭烈恩等. 一種基于ISA總線的高速數據采集系統的設計. 華南理工大學學報, 2004;(8)

3 王志華, 尹項根, 張小波等. 利用CVT捕捉電壓行波實現故障測距的分析與實踐. 電力系統自動化, 2004;(8)

4 林長青, 孫勝利. 基于FPGA的多路高速數據采集系統.電測與儀表, 2005;(5)

5 Zhang Donglai, Zhang Dongsheng, Zhang Jian et al. Data sampling system with high speed and high timing synchron-ization precision for power line fault position detection based on dual ports traveling wave distance measurement method. IEEE/PES T&D, 2005

6 THS1408datasheet. Texas Instruments Incorporated,2002