摘? 要: 提出一種基于DDS技術(shù)的數(shù)字化通用聲納信號(hào)模擬器" title="信號(hào)模擬器">信號(hào)模擬器的實(shí)現(xiàn)方案。通過控制DDS器件輸出信號(hào)的幅度和相位來模擬成像聲納基陣的輸出,可以對(duì)任意距離和方位上目標(biāo)回波進(jìn)行精確的模擬,并可以模擬運(yùn)動(dòng)目標(biāo)的回波信號(hào)。討論了多通道信號(hào)模擬器在設(shè)計(jì)和實(shí)現(xiàn)中的具體問題。

關(guān)鍵詞: 聲納? 波束形成? DDS? CPLD

?

近年來隨著海洋開發(fā)和海軍技術(shù)的發(fā)展,聲納設(shè)備的研究越來越受重視。但是由于水聲設(shè)備試驗(yàn)通常需要適宜的水聲環(huán)境,例如消聲水池、湖泊或海洋等,因而試驗(yàn)的復(fù)雜性和成本都較高。為了能在普通實(shí)驗(yàn)室環(huán)境中模擬目標(biāo)回波信號(hào),需要針對(duì)各種聲納設(shè)備的要求設(shè)計(jì)專用的聲納信號(hào)模擬器。

1 聲納信號(hào)模擬器本原理的基

1.1 波束形成原理簡(jiǎn)介

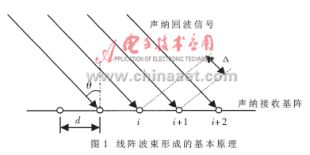

本文旨在研制適用于某種高分辨率成像聲納的信號(hào)模擬器。該成像聲納接收聲基陣采用48元等間隔線陣" title="線陣">線陣,工作頻率800kHz,作用距離為0.5~25米,角度分辨率為0.35°。成像聲納對(duì)接收基陣信號(hào)進(jìn)行波束形成,從而實(shí)現(xiàn)聲圖像的獲取。聲納波束形成的基本原理如圖1所示。

?

圖1是遠(yuǎn)場(chǎng)時(shí)等間隔線陣接收回波信號(hào)的示意圖[1]。入射聲波與基陣法線方向成θ角平行入射,基元從左至右順序編號(hào)為1、2、...i、i+1、...N,基元間距為d。如果選取1號(hào)基元為時(shí)間參考點(diǎn),其接收到的信號(hào)為Acos2πft,那么相鄰兩個(gè)基元間存在聲程差Δ=dsinθ,因此第i個(gè)基元接收到的信號(hào)為:

其中c為聲速。由于成像聲納是窄帶主動(dòng)聲納,所以i基元與1號(hào)基元接收信號(hào)間的相位差是φi=2π(i-1) sinθ,其中λ為波長。因此要想使線陣定向在θ0方向上,只需將第i個(gè)基元的信號(hào)延時(shí)

sinθ,其中λ為波長。因此要想使線陣定向在θ0方向上,只需將第i個(gè)基元的信號(hào)延時(shí) 即可。

即可。

以上是線陣波束形成的基本原理,但這只是遠(yuǎn)場(chǎng)情況下的近似。對(duì)于近場(chǎng)條件,這樣的近似產(chǎn)生的誤差會(huì)很大。對(duì)于本文中的高頻成像聲納,由于全部工作范圍均屬近場(chǎng)條件,所以波束形成時(shí)必須采用聚焦方法。其基本原理同上,只是對(duì)每個(gè)基元信號(hào)進(jìn)行的延遲(或移相)不成線性關(guān)系,本文對(duì)此不做詳述。

1.2 聲納信號(hào)模擬器原理

用于成像聲納的信號(hào)模擬器一般通道數(shù)與基元個(gè)數(shù)相同,每個(gè)通道的輸出模擬聲納基陣中一個(gè)基元的信號(hào)。由于成像聲納工作距離較近,并且水聲環(huán)境中高頻段的噪聲級(jí)很低,因而接收信噪比通常較高。出于這樣的考慮,信號(hào)模擬器的輸出中就不額外加入噪聲。成像聲納工作在較強(qiáng)的混響" title="混響">混響環(huán)境中,由于混響的模擬比較困難,并且對(duì)成像的影響并不嚴(yán)重,因而在設(shè)計(jì)中也不考慮對(duì)混響的模擬,只專注于模擬近場(chǎng)目標(biāo)回波。

根據(jù)用戶輸入的要模擬的點(diǎn)目標(biāo)的方位和距離,信號(hào)模擬器計(jì)算出相應(yīng)的目標(biāo)回波到達(dá)接收基陣各個(gè)基元的相位差,然后按照這些相位差產(chǎn)生相應(yīng)的多路正弦信號(hào)。將這些信號(hào)加到成像聲納的輸入端,代替真實(shí)的基陣輸出,這樣就可在陸上試驗(yàn)室條件下方便地對(duì)成像聲納進(jìn)行調(diào)試和測(cè)量。

1.3 傳統(tǒng)聲納信號(hào)模擬器的缺陷

傳統(tǒng)的聲納信號(hào)模擬器通常采用一個(gè)固定頻率的振蕩器產(chǎn)生與聲納系統(tǒng)工作頻率相同的正弦信號(hào)。將本振信號(hào)通過一組多抽頭模擬延遲線" title="延遲線">延遲線,然后從延遲線的不同抽頭中引出信號(hào)作為模擬器的輸出。這種信號(hào)模擬器結(jié)構(gòu)存在若干缺陷和不足。

首先,由于采用模擬器件構(gòu)成抽頭延遲線結(jié)構(gòu),最小可變的延遲長度受限。尤其是考慮到系統(tǒng)的硬件規(guī)模和成本,一般延遲線的抽頭數(shù)目不多,這樣就造成延遲時(shí)間和理論值之間存在較大誤差,從而降低了模擬器的精度。

其次,為了實(shí)現(xiàn)對(duì)不同方位目標(biāo)回波信號(hào)的模擬,就必須將不同抽頭延遲線的輸出進(jìn)行切換或組合,然后作為一個(gè)基元的信號(hào)輸出到聲納設(shè)備。因此整個(gè)模擬器的規(guī)模龐大,且只能模擬若干個(gè)離散方位和距離上的目標(biāo),不能實(shí)現(xiàn)對(duì)任意方位距離上點(diǎn)目標(biāo)回波的模擬,否則復(fù)雜度大增將難以實(shí)現(xiàn)。

另外,使用模擬器件構(gòu)成的抽頭延遲線,其通道一致性難以保證,調(diào)試?yán)щy。且延遲線頻率范圍較窄,如果頻率參數(shù)發(fā)生變化將不能正常使用,因此適用范圍窄,性價(jià)比很低。

為了克服傳統(tǒng)聲納信號(hào)模擬器的這些缺陷,本文采用DDS技術(shù)設(shè)計(jì)并實(shí)現(xiàn)了新型信號(hào)模擬器。這種基于DDS的模擬器結(jié)構(gòu)可以實(shí)現(xiàn)對(duì)任意方位距離上點(diǎn)目標(biāo)回波信號(hào)的精確模擬,適用于不同頻率參數(shù)并具有一定擴(kuò)展能力,從而具有很高的性價(jià)比。

2 DDS構(gòu)成的信號(hào)模擬器

2.1 DDS技術(shù)簡(jiǎn)介

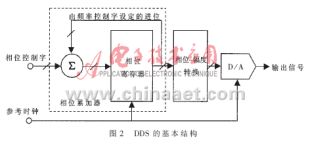

DDS技術(shù)出現(xiàn)于二十世紀(jì)70年代,是一種全數(shù)字頻率合成技術(shù)。它將先進(jìn)的數(shù)字信號(hào)處理理論與方法引入信號(hào)合成領(lǐng)域,實(shí)現(xiàn)了合成信號(hào)的頻率轉(zhuǎn)換速度與頻率準(zhǔn)確度之間的統(tǒng)一。它具有相位變換連續(xù)、頻率轉(zhuǎn)換速度快、頻率分辨率極高、相位噪聲低、易于用微機(jī)等多種方法控制以及體積小、集成度高等多種優(yōu)點(diǎn),因而近年來DDS在理論和應(yīng)用上得到了飛速的發(fā)展。

DDS的基本結(jié)構(gòu)如圖2所示[2]。

?

由于DDS具有頻率和相位可以精確數(shù)控的特點(diǎn),因而將DDS器件作為成像聲納信號(hào)模擬器的關(guān)鍵部件,并輔以相應(yīng)的控制和接口邏輯等,就可以實(shí)現(xiàn)對(duì)任意方位和距離目標(biāo)回波的精確模擬。

2.2 DDS構(gòu)成的模擬器結(jié)構(gòu)

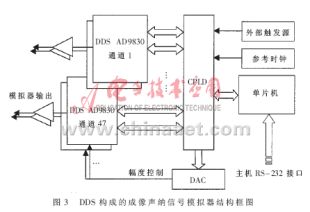

基于DDS技術(shù)的成像聲納信號(hào)模擬器的結(jié)構(gòu)如圖3所示。

?

模擬器共有48個(gè)信號(hào)通道,每個(gè)通道模擬聲納接收基陣中一個(gè)基元的輸出。通道電路由單片DDS器件AD9830及其接口邏輯電路、輸出I-V變換器及濾波和跟隨電路構(gòu)成。各個(gè)通道的DDS器件與CPLD之間的接口采用16bit位寬的并行總線。

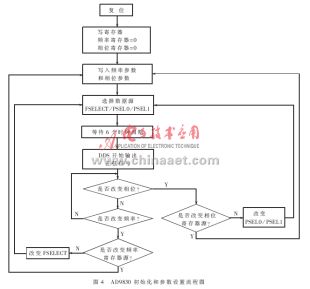

用戶將要模擬的目標(biāo)方位、距離、信號(hào)幅值等信息輸入到主機(jī)的應(yīng)用程序界面中,應(yīng)用程序根據(jù)這些信息,按照近場(chǎng)聚焦的算法計(jì)算出每個(gè)通道信號(hào)相對(duì)于參考通道的相位差等參數(shù),然后通過RS-232串行總線將這些參數(shù)下傳到信號(hào)模擬器中。信號(hào)模擬器中的微控制器將這些參數(shù)接收并解碼,并將每個(gè)通道信號(hào)的頻率和相位等參數(shù)通過CPLD寫入相應(yīng)通道的DDS器件的控制寄存器中。AD9830初始化和參數(shù)設(shè)置[3]的流程圖見圖4。

?

2.3 目標(biāo)距離的模擬

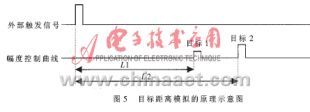

信號(hào)模擬器從主機(jī)接收到的參數(shù)除了各通道頻率和相位差外,還包括輸出信號(hào)的幅度(增益)控制曲線參數(shù)。幅度控制參數(shù)也由單片機(jī)解碼并按照曲線的定時(shí)參數(shù)發(fā)送到DAC中,數(shù)模轉(zhuǎn)換后的幅度控制信號(hào)送入AD9830的Rset端,從而控制了輸出信號(hào)的幅度。

這個(gè)幅度控制電路是一個(gè)開環(huán)系統(tǒng),具有較好的動(dòng)態(tài)性能,帶寬可達(dá)100kHz。采用適當(dāng)?shù)姆?增益)控制曲線并配合外部觸發(fā)源,可以實(shí)現(xiàn)對(duì)預(yù)定距離上點(diǎn)目標(biāo)回波信號(hào)的模擬。其工作原理如圖5所示。要模擬與接收基陣相距分別為L1和L2的兩個(gè)點(diǎn)目標(biāo),則按照模擬器中DAC的轉(zhuǎn)換速率生成相應(yīng)的幅度控制曲線。該幅度控制曲線在模擬器中與外部觸發(fā)信號(hào)同步,而外部觸發(fā)信號(hào)與成像聲納發(fā)射機(jī)同步,即它的上升沿對(duì)準(zhǔn)聲納發(fā)射脈沖的前沿時(shí)刻。這樣在幅度曲線的控制下就可以精確模擬預(yù)定距離上的點(diǎn)目標(biāo)回波。

?

本文采用的DDS器件AD9830中共有4個(gè)相位寄存器,如果事先寫入計(jì)算好的相位參數(shù),并且在使用幅度曲線控制的同時(shí)配合相應(yīng)的相位轉(zhuǎn)換,就可以在一次發(fā)射回波中模擬最多4個(gè)不同方位和距離上的點(diǎn)目標(biāo)。

3 幾個(gè)注意事項(xiàng)

3.1 參考時(shí)鐘的扇出" title="扇出">扇出(Fan-out)

為了提高系統(tǒng)的可靠性和可擴(kuò)展能力,整個(gè)模擬器采用了3U EuroCard機(jī)箱+背板+插板的結(jié)構(gòu),每8個(gè)通道電路在一塊插板上實(shí)現(xiàn),總線接口和參考時(shí)鐘等信號(hào)位于背板。這樣的結(jié)構(gòu)造成參考時(shí)鐘的布線拓?fù)浔容^復(fù)雜。并且因通道數(shù)較多,所有通道的DDS器件公用一個(gè)參考時(shí)鐘,時(shí)鐘的扇出和布線以及阻抗匹配等就顯得非常重要。如果扇出不合理,造成各通道DDS輸入端的參考時(shí)鐘存在延遲,就會(huì)影響系統(tǒng)的精度[4]。另外由于參考時(shí)鐘頻率高達(dá)50MHz,信號(hào)完整性問題也將影響系統(tǒng)的正常工作。

本文采用了Cypress公司的高速時(shí)鐘分布器件CY2308,將石英晶體振蕩器產(chǎn)生的參考時(shí)鐘扇出為6個(gè)獨(dú)立的時(shí)鐘,分別送到6塊通道板,嚴(yán)格保證每條時(shí)鐘信號(hào)在PCB上的路徑等長并進(jìn)行精確的阻抗匹配。同時(shí),每塊通道板中也使用同樣的扇出和布線方法。這樣,各個(gè)通道的時(shí)鐘間延遲小于200ps,可以保證模擬器的精度。

3.2 混合電路的布線

由于信號(hào)模擬器中既存在大量高頻數(shù)字邏輯控制信號(hào),輸出信號(hào)又是多通道微弱模擬信號(hào)(mV級(jí)),因而要特別注重?cái)?shù)模混合電路的布局布線、退耦、電源和地平面的分割等事項(xiàng)。這方面有許多專著討論,本文不再詳述。值得注意的是,DDS器件的Layout應(yīng)嚴(yán)格按照參考設(shè)計(jì)進(jìn)行,以確保系統(tǒng)的性能。

3.3 DDS器件的安全

單片集成式DDS器件多數(shù)采用CMOS工藝生產(chǎn),比較脆弱易損,在設(shè)計(jì)與調(diào)試中應(yīng)特別注意。由于信號(hào)模擬器在使用中可能出現(xiàn)輸出被意外短路等情況,因此在輸出級(jí)采用跟隨器以避免DDS意外損壞。此外,在設(shè)計(jì)幅度控制電路時(shí)應(yīng)留有一定余量,避免DDS因輸出電流過大而失效。

本文提出并實(shí)現(xiàn)了采用DDS技術(shù)的新型聲納信號(hào)模擬器。完成的模擬器樣機(jī)克服了傳統(tǒng)模擬技術(shù)結(jié)構(gòu)復(fù)雜、可靠性差、可調(diào)范圍窄等弊端,可以實(shí)現(xiàn)對(duì)任意方位和距離上點(diǎn)目標(biāo)回波信號(hào)的精確模擬,使用方便可靠,在某高頻成像聲納的設(shè)計(jì)和調(diào)試中起到了十分關(guān)鍵的作用。同時(shí),該模擬器具有較好的適應(yīng)性和擴(kuò)展能力,可以用于未來的多種型號(hào)成像聲納的調(diào)試,具有很強(qiáng)的工程實(shí)用價(jià)值和廣闊的應(yīng)用前景。

?

參考文獻(xiàn)

1 李啟虎. 聲納信號(hào)處理引論(第二版). 北京:海洋出版社,2000

2 Walt Kester. High Speed DACs and DDS Systems.Analog Devices Inc.,1998

3 CMOS Complete DDS-AD9830 Datasheet. Analog Devices?Inc.,1996

4 Howard W. Johnson, Martin Graham. High-Speed Digital Design. Prentice Hall PTR,1993