摘 要: 介紹了系統芯片SOC的概念和M8051 IP軟核" title="軟核">軟核的原理,給出了視頻字符疊加器" title="字符疊加器">字符疊加器VAD_SOC中M8051 IP軟核的作用,詳細介紹了I2C主控制器" title="主控制器">主控制器模塊的設計,給出了功能仿真波形,最后對M8051IP軟核在視頻字符疊加器中的重應用進行了深入研究。

關鍵詞: 系統芯片 微控制器 M8051 IP軟核 視頻字符疊加器

隨著集成電路制造技術的快速發展,集成電路的規模不斷擴大。這使得將復雜系統集成在單個芯片上成為可能,于是便出現了系統芯片SOC(System on a Chip)。傳統芯片設計方法" title="設計方法">設計方法關注的是如何創建一個全新的設計并進行有效的驗證;如今在SOC設計中,基于IP模塊的功能組裝正在逐漸替代傳統的功能設計而成為主流設計方法。基于IP模塊的SOC設計方法的基本思路是通過系統設計的應用層次,利用現有的IP資源,根據系統需求選用適當的IP模塊,進行系統集成設計;基于IP模塊的SOC設計方法是采用IP模塊而不是采用基本邏輯或電路單元作為基礎單元,即以功能組裝代替功能設計。這就提高了設計者的設計能力,能夠較快地完成設計,保證設計成功,以極低的價格滿足市場需求。

M8051 IP軟核是高性能的8位微控制器(MCU),它的每個機器周期只需要兩個時鐘周期而不是標準8051[1] 軟核的十二個周期,但是它的功能卻與標準的8051軟核兼容。這就使得M8051 IP軟核在同樣功耗的情況下運行速度比標準的8051軟核提高六倍,也就是說,若在同樣的運行速度下,M8051 IP軟核的功耗僅僅是標準8051軟核的六分之一。這對于現在的便攜式數字產品或低功耗產品來說是相當有競爭力的。

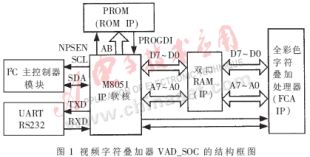

視頻字符疊加器是一種在視頻信號中疊加入字符或簡單的圖文信息,從而在屏幕的特定位置上與圖像信號同時進行顯示的設備[2]。視頻字符疊加器VAD_SOC的結構如圖1所示,具體包括以下幾個IP模塊: M8051 IP軟核、I2C主控制器模塊、 存儲器核和全彩色字符疊加處理器(FCA IP)等。其實現的功能是將片外或內置的疊加字符ROM(如E/E2PROM、雙口RAM或Flash)中儲存的字符信息轉變為可疊加在視頻信號上的信息,同時通過內部時序控制功能單元,調節疊加字符在監視器上的疊加位置、大小及其背景色和前景色等。

本文主要介紹M8051 IP軟核的改進設計,對其進行有效的仿真和驗證;并對M8051 IP軟核在視頻字符疊加器VAD_SOC中的重應用進行深入的研究。

1 M8051 IP軟核結構及其改進性設計

1.1 M8051 IP軟核的結構

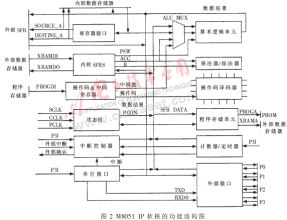

M8051 IP軟核的功能結構框圖如圖2所示,主要由五部分組成。

(1)算術邏輯單元" title="算術邏輯單元">算術邏輯單元(ALU)部分:位算術邏輯單元、帶進位的算術邏輯單元、8位的算術邏輯單元,操作數的選擇、乘法/除法單元。

(2)數據存儲與交換部分:內部數據存儲器、內部專用寄存器及其復用、專用功能寄存器的復用、核級專用功能寄存器。

(3)狀態機與程序存儲部分:主狀態機、程序計數器、程序計數器的運算單元。

(4)指令譯碼部分:取指令、指令譯碼。

(5)外圍設備部分:(I/O)端口寄存器、中斷、定時器、計數器、通用串行口。

從圖2可以看出,M8051 IP軟核與傳統8051單片機在組成部分及指令系統部分是兼容的,但功能上有些不同,詳見表1。所以,若要將M8051 IP軟核集成到視頻字符疊加器VAD_SOC中,則需要進行一些簡單的功能擴展和可復用設計。

1.2 I2C主控制器的RTL級實現

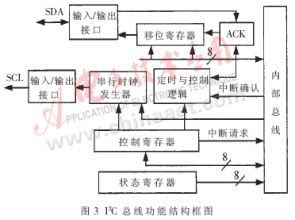

I2C總線是Philips公司提出的一種串行數據傳輸技術,通過數據線(SDA)和時鐘線(SCL)兩個總線即可完成全雙工同步數據的發送和接收,在需要與外圍器件進行低速通信時,I2C總線是個不錯的選擇。目前8051 IP軟核是片上系統中用得比較多的微控制器核之一,但是其沒有集成I2C總線,應用起來很不靈活。所以在設計片上系統時常常需要將I2C系統集成到8051 IP核中,以方便其與MCU的外圍接口連接,擴展8051 IP核的功能。由于篇幅的限制,本文只對I2C主控制器模塊進行簡單研究。I2C主控制器模塊是根據Philips公司的8xc552的I2C接口原理設計的。由于通常情況下單片機系統都作為主系統使用,一些功能是不需要的,所以圖3只是本設計用到的I2C原始的功能結構簡化框圖。

1.2.1 I2C主控制器的端口源代碼格式[3]

I2C主控制器端口源代碼格式如下:

module i2c_top (s1sfrdi,si,sda,scl,regresult,source_addr,

destine_addr, sfr_write, rmw, internal_reset, pclk_en, pclk);

output [7:0] s1sfrdi;

output scl ,si;

inout sda;

input [7:0] regresult;

input [7:0] source_addr;

input [7:0] destine_addr;

input sfrwe, rmw, internal_reset;

input pclk, pclk_en;

……

endmodule

1.2.2 I2C主控制器與M8051 IP軟核的接口

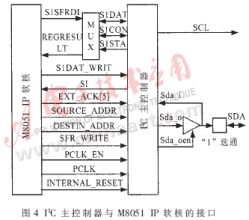

I2C主控制器的數據端口(SDA)是雙向端口,利用串行數據線SDA傳輸數據,所以不使用總線時必須關閉三態門的輸出控制端,即sda_oen為“0”;另一方面,數據可以通過引腳直接進入模塊內部,但必須設置輸出控制端為“1”,即sda_oen為“1”。I2C主控制器與M8051 IP軟核的接口如圖4所示。

1.2.3 I2C主控制器的軟件仿真與結果

在I2C主控制器設計過程中,主要用Modelsim SE PLUS5.6、QUARTUS2.0等軟件作為前端的仿真工具并 針對I2C主控制器的主接收和主發送兩個狀態機的不同激勵條件,編寫測試代碼進行測試。電路仿真時序波形圖如圖5和圖6所示。

2 M8051 IP軟核在視頻字符疊加器VAD_SOC中的重應用

M8051 IP軟核在視頻字符疊加器VAD_SOC中的重應用的結構如圖1所示。它的主要任務是從程序存儲器中讀出指令代碼,經編譯執行后,向周圍的相應模塊提供操作命令和地址、數據總線值,完成一個復雜的狀態機及對其它模塊的部分控制功能,協同其它模塊共同工作,實現將字庫中的字符取出放到全彩色字符疊加處理器上進行顯示。工作流程如下:

(1) 將要顯示的字符從PC機的鍵盤輸入,經串行口RS-232的接口寫入到字庫中。

(2) 從程序存儲器中讀出指令代碼,經編譯執行后,向周圍的相應模塊提供操作命令和地址、數據總線值。

(3) 繼續執行代碼,從字庫中讀入要顯示的字節數據,并將它存放在SFR(專用寄存器)中。

(4) 繼續執行代碼,將專用寄存器中的數據傳送到雙口RAM中進行緩存。

(5) 通過對控制模塊的控制,實現數據讀取、地址生成,并按時空拓撲劃分的形式進行行、列地址及數據信號的選擇。

(6) 最后,將選擇出的信號通過三通接口加到視頻信號中進行顯示。

基于以上考慮,本系統中M8051 IP核具有一定的專用性,是針對具體的VAD_SOC系統而設計的,因此不需完全拘泥于標準的MCU的所有特點,只需設計出滿足VAD_SOC系統要求的嵌入式M8051 IP核即可。

2.1 視頻字符疊加器VAD_SOC的設計及功能仿真

2.1.1設計流程

第一步:生成VAD_SOC頂層初始網表。在四個模塊開發之后,只需開發用于集成的網表,即可用于模塊之間的連接。

第二步:處理VAD_SOC頂層中四個模塊的時序預算,此時每個模塊建立一個“黑盒”時序模型。

第三步:改進VAD_SOC頂層布線,在模塊實現的同時解決頂層的信號完整性問題。此外,還要考慮前兩步中不需涉及的電源問題,其中包括模擬模塊和I/O模塊問題。同時模塊層的實現也在此步進行,通過采用物理綜合方法來確保模塊層的時序收斂。VAD_SOC頂層設計和四個模塊實現之間是同步進行的。

第四步:用模塊的實際尺寸修改VAD_SOC頂層描述,這一步需用Aristo 的IC Wizard處理,大約需要2~3小時。

2.1.2 視頻字符疊加器VAD_SOC的仿真波形

視頻字符疊加器VAD_SOC的功能仿真是在NC_Verilog下進行的,圖7顯示了兩個場同步周期的字符疊加信號的仿真波形圖。

建立在IP模塊功能組裝基礎上的片上系統設計,使設計方法從電路設計轉向系統設計,設計重心從邏輯綜合、門級布局布線、后模擬轉向系統級模擬、軟硬件聯合仿真、以及若干個IP模塊組合在一起的物理設計。為了對各模塊特別是IP模塊進行有效的測試,還必須在模塊中加入可測性設計;同時,在驗證方法上要采用數字電路和模擬電路在一起的混合信號驗證、軟硬件協同驗證以及并行驗證等多種方法。經過試驗可知,M8051 IP核在視頻字符疊加器VAD_SOC中實現了所需的基本功能,并且仿真主頻率可以達到33MHz。

參考文獻

1 何立民.單片機應用系統設計.北京:北京航空航天大學出版社,1990

2 傅萬鈞. 應用電視技術.北京:電子工業出版社,1994

3 夏宇聞.復雜數字電路與系統的Verilog HDL設計技術.北京:北京航空航天大學出版社,1998:87~100

4 Rochit Rajsuman. SOC設計與測試.北京:北京航空航天大學出版社, 2003:96~107