PCIE(PCI express)是用來互聯諸如計算機和通信平臺應用中外圍設備的第三代高性能I/0總線。PCIE體系結構繼承了第二代總線體系結構最有用的特點,采用與PCI相同的使用模型和讀/寫通信模型,支持各種常見的事務。其存儲器、I/0和配置地址空間與PCI的地址空間相同。由于地址空間模型沒有變化,所以現有的OS和驅動軟件無需進行修改就可以在PCIE系統上運行。

PCIE是串行協議,與原有的PCI并行總線相比,它沒有大量的數據和控制線,對于硬件電路設計者來說,省去了很多硬件設計工作。PCIE的傳輸速度遠遠大于PCI總線,PCIE1.1版本單個鏈路的單向吞吐量能達到250 MB/s。對于需要與主機進行大容量傳輸的系統來說,該總線標準的優勢是非常明顯的。

由于PCIE總線硬件設計簡單,吞吐量大,軟件向下兼容,只要找到合適的總線接口芯片,很容易將現有的PCI總線設備升級為PCIExpress設備。Altera公司最新推出的EP2SGX90系列的芯片,給用戶提供了PCIE接口IP核。本文將結合實際的應用,詳細介紹該IP核的使用情況,包括寄存器設置,DMA操作等。

1 功能描述及參數設置

按照PCIE協議的要求,該FPGA的IP核也采用三層體系結構,即傳輸層、數據鏈路層和物理層。這三層功能模塊完成了PCIE的協議轉換,在傳輸層上給開發人員提供了非常豐富的接口。開發人員的所有開發,包括DMA傳輸等都是在傳輸層以上進行的。

傳輸層(transaction layer):完成TLP(數據傳輸包)的收發,含有虛擬信道(VC)緩沖區,具有端口仲裁、VC仲裁、流控制、數據重新排序和數據校驗等功能。

數據鏈路層(data link layer):數據鏈路層的主要功能是保證在各鏈路上發送和接收數據包時數據的完整性。在接收端,對數據進行嚴格的CRC校驗,如果有錯誤,會給發送方返回1個NAK信號。發送端具有重傳緩沖區,如果收到NAK信號,則把數據重新發送1次。

物理層(physical layer):對于發送端,接收數據鏈路層的數據包,把這些數據進行8 b/10 b編碼,送到串行發送器上;對于接收端則剛好相反,收到串行碼后,先解碼,然后送給數據鏈路層。

在生成PCIE的IP核時,至少選擇2個存儲區,一個是BAR[1:O],用作用戶開發板的擴展存儲區用;還有一個是BAR2,下面所有的寄存器操作都是基于該地址的。新生成的IP核不帶有DMA功能,但是在工程文件夾下面有一個xxxx_examples(xxx代表工程名稱)的文件夾,文件夾里有簡單DMA和鏈式DMA的例子代碼,開發者只需要對這些代碼進行修改,就能開發出適合自己的DMA功能模塊。

2 簡單DMA

該DMA傳輸模式相對比較簡單,只需要對相應的寄存器進行設置即可完成,DMA傳輸步驟如下所示,每進行1次DMA傳輸,都需要按照下面的步驟進行1次設置。下面所述的偏移量都是相對于BAR2地址。

(1)設置偏移量為0x00和0x04的寄存器,寫入DMA傳輸的主機端地址;

(2)設置偏移量為0x14的寄存器,寫入DMA傳輸的PCIE端點地址;

(3)在偏移量為0x08的寄存器中寫入本次DMA傳輸的長度,以字節為單位;

(4)設置偏移量為0x0C的寄存器,設置DMA傳輸的屬性,對該寄存器的寫操作將啟動本次DMA傳輸;

(5)讀取0x0C的寄存器DMA傳輸狀態位,察看本次DMA是否完成。

3 鏈式DMA

鏈式DMA是一種效率遠遠高于簡單DMA的傳輸方式,它只需要1次啟動操作,就可以完成多次DMA傳輸。這里將結合實際使用情況,詳細介紹鏈式DMA的傳輸過程。

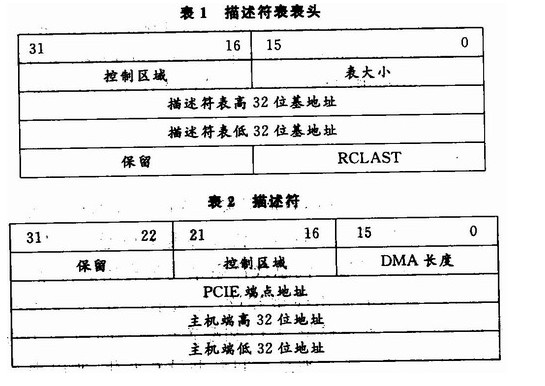

3.1 描述符表

實現鏈式DMA傳輸時,需要開發人員在主機內存中開辟一塊空間,用來存儲描述符表,它由一個表頭和多個描述符組成,其中每一個描述符對應一次DMA操作。用戶根據自己的需求填寫該描述符表,關于該描述符表的詳細說明如表1和表2所示。

控制區域中含有一些控制信息,其中第16位用來控制傳輸方向,為O是DMA寫,為1是DMA讀,這里的讀/寫是以主機端為參考的,如果以PCIE核為參考,方向剛好相反。第18位用來使能DMA傳輸計數,如果該位使能為1,那么在DMA傳輸過程中,PCIE核每完成1次DMA操作,都會進行1次計數操作,然后把這個計數結果傳送給主機,主機把這個結果填寫到描述符表的RCLAST字段中。

表大小是指本次鏈式DMA操作對應的描述符個數,每個描述符對應一次DMA操作。

RCLAST是一個計數單元,它有兩個作用,在鏈式DMA傳輸前,表示還有多少個DMA操作等待傳輸,由于它是從0開始計數的,所以這個值等于表大小減1。還有一個重要作用是在鏈式DMA傳輸過程中,用來表示鏈式DMA傳輸的狀態。如上所述,如果控制區域的第18位設置為1,那么每完成1次DMA操作,主機都會更新這個計數器。當計數器的數值(也是從O開始計數的)等于前面設置的期望傳輸的DMA次數,就表示鏈式DMA傳輸操作結束。開發人員可以用這個狀態單元來察看本次傳輸是否結束,從而開始一個新的傳輸周期。

DMA長度用來設置本描述符對應的DMA傳輸的長度,是以32位為單位的。主機端地址用來指示數據存放存放的位置。

3. 2 實現范例

根據上面介紹的描述符表,下面給出一個鏈式DMA讀的驅動程序例子。首先生成一個描述符表,然后把描述符表表頭的4個字段的內容分別寫入BAR2地址偏移量為0x0,0x4,0x8和0xC寄存器中。寫完后即開始此次鏈式DMA讀傳輸,while循環用于等待鏈式DMA結束。從下面的代碼可以看出,2個描述符對應2次DMA操作。

圖1是用SignalTap工具獲取的鏈式DMA讀時序圖。PCIE核接收tx_req0請求信號,然后給出一個tx_ack0,同時將tx_dr0置為有效,該信號套住的TXData就是需要讀取的有效數據。在每次DMA結束之后,PCIE核都會用同樣的控制邏輯給主機傳送1個已完成DMA次數的狀態字,如圖1中的44040000h。

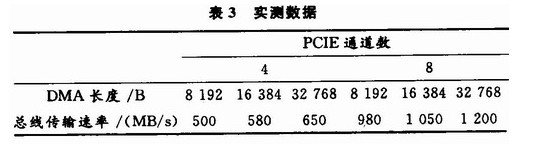

4 性能測試

在做總線性能測試時,采用鏈式DMA傳輸方式,共4個描述符表。根據實際使用的PCIE總線通道數和DMA長度的不同,實際測試得到的總線速度也不同,表3給出了參考數據。

5 結語

使用FPGA來設計PCIE總線擴展卡,可以省去專用的PCIE接口芯片,降低了硬件設計成本,提高了硬件的集成度。利用FPGA的可編程特性,大大提高了設計靈活性、適應性和可擴展性。PCIE總線提供了高速、獨享的數據交換通道,確保在大數據量的數據交換時不會出現瓶頸,而且作為新一代總線,它使系統在獲得更高性能的同時,具有了良好的升級性。