摘 要: 描述了基于PXI總線的數字輸入/輸出模塊的特點和原理,以及用PCI9030接口芯片和FPGA器件實現的PXI總線接口電路,提出了數字輸入/輸出電路及高精度延時補償電路的實現方法。實踐證明系統原理和硬件設計是成功的。

關鍵詞: PXI總線 數字輸入/輸出 PCI9030 FPGA器件

PXI總線是PCI總線的一種擴展總線;PXI總線是設計用戶測試系統的標準選擇,可以靈活地組建自動測試系統。PXI總線具有標準、開放、結構緊湊、數據吞吐能力強、模塊可重復使用、眾多儀器廠家支持等優點,其應用領域越來越廣泛。

基于PXI總線的數字輸入/輸出模塊用來接收和發送來自被測器件的圖形數據,通過與預期的正確結果進行比較,完成被測電路的功能測試。用它組建的測試系統,具有測試速率快、可靠性高和診斷精度高等特點,能夠滿足不同電子產品測試的要求,可廣泛應用于數字系統的在線故障診斷、總線仿真、微處理器仿真以及電子裝備故障診斷等。

1 數字輸入/輸出模塊的工作原理

數字輸入/輸出模塊采用PXI總線測試平臺,具有四通道32路,每個通道存儲深度為64K,可獨立編程為輸入或輸出通道,時鐘頻率最高可達20MHz,存儲的圖形數據支持單次、循環和跳轉三種輸出方式,輸出電平兼容COMS/TTL電平,輸出擺率不超過±5ns,輸出電平脈沖寬度可編程調節,其范圍為6.25ns×4~409.6μs×1024,測試圖形的裝載速率,可以達到10MByte/s,能夠在很短的幾秒鐘內完成圖形數據的裝載及數據的輸入/輸出。

數字輸入/輸出模塊用于數字測試的基本方法是:從輸入端施加若干測試激勵,記錄并觀察其相應的輸出響應,并與預期的正確數據進行比較。如果兩者不一致,則可能有故障存在。同時對有故障的電路板進行進一步的診斷,找出故障發生的原因,進行維修,這就是通常所說的功能測試。對于一個具有n個輸入/輸出端口的電路板來說,完全測試需2n條測試激勵,如果n較小,可以用2n條測試激勵進行完全測試;但當n較大時,則需要有多路的測試激勵同時進行工作,這就需要數字輸入/輸出模塊能夠提供盡可能多的輸出通道,滿足故障測試的要求。

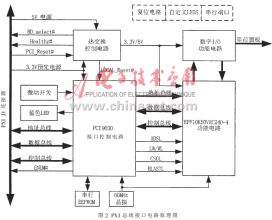

數字輸入/輸出模塊的工作原理如圖1所示,整個電路的實現由PXI總線接口電路和功能電路兩部分組成,PXI總線接口電路采用可編程器件及PCI9030接口芯片來實現接口功能;功能電路部分含有四個通道,每個通道都可以指定為輸出激勵模式或記錄響應模式。輸出激勵模式的作用是:在主控計算機上生成激勵圖形數據,根據圖形的寬度、長度、輸出方式確定所需端口個數;對所用端口生成相應控制信息,通過PXI控制器將圖形數據和控制數據傳給圖形I/O" title="I/O">I/O模塊,并存入各個端口的圖形存儲器中;設置起始地址,選擇激勵時鐘,設置圖形存儲器的工作方式" title="工作方式">工作方式為輸出方式;最后由上位機發送“運行”命令,圖形I/O輸出激勵圖形數據到DUT端口。記錄響應模式的作用是:根據所要記錄的響應圖形的寬度、長度確定所需端口個數,對所用端口生成相應控制信息,通過PXI控制器將控制數據傳給圖形I/O模塊,并存入各個端口的圖形存儲器中;設置起始地址,選擇響應時鐘,設置圖形存儲器的工作方式為記錄方式;最后由上位機發送“運行”命令,使圖形I/O接收來自DUT端口的響應圖形數據并存儲在圖形存儲器內。記錄結束后上位機從模塊讀取響應圖形數據,以供分析研究使用。

存儲器通過PXI總線從上位機下載激勵圖形數據,單次或循環輸出激勵圖形數據,接收來自DUT端口的響應圖形數據并保存到圖形存儲器中。地址發生器為PXI總線讀寫圖形存儲器時提供地址,在輸出或記錄時實現圖形I/O從任意地址進行任意長度的單次或循環輸出數據。激勵圖形數據從圖形存儲器輸出后經觸發器進行同步直接輸出。所有的控制切換都由控制邏輯完成,這些邏輯在FPGA上實現。

每個端口的控制寄存器包括圖形存儲器地址、轉移目標地址、端口數據總線、配置和狀態/時鐘源等寄存器。圖形存儲器地址寄存器用于設置圖形存儲器的當前地址;轉移目標地址寄存器用于循環執行;端口數據總線寄存器負責PXI總線和圖形存儲器的通訊,用于激勵圖形數據加載" title="加載">加載、校驗和響應圖形數據的轉儲;配置寄存器用于圖形存儲器的工作方式設定;狀態/時鐘源寄存器控制圖形發生器的起停,選擇圖形發生器的時鐘。

2 PXI總線接口電路

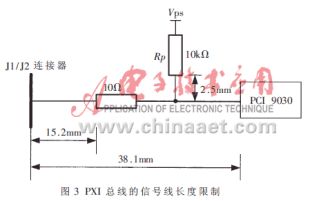

PXI總線接口電路是采用PCI9030接口芯片來實現的,PXI總線接口電路主要由熱交換控制電路、PCI9030接口控制電路、FPGA控制電路和數字輸入/輸出功能電路等組成。采用Altera公司的FLEX系列的EPF10K50VRC240-4 FPGA實現部分PCI接口邏輯電路及功能電路,采用PCI9030實現PCI總線的接口邏輯電路。PCI9030 具有最靈活的局域總線,允許各種存儲和I/O 設備選擇多種接口。PCI9030以PLX在Compact PCI上的經驗為基礎,是首個支持Compact PCI熱交換的目標設備。它符合PCI V2.2規范的32位33MHz 目標接口芯片,使PCI 突發傳輸速度高達132兆字節/秒;具有高達60MHz的局域總線操作,使突發傳輸速度高達240兆字節/秒的特點;可編程局域總線操作,支持非多路復用和多路復用32 位地址/數據協議,并支持動態局域總線寬度控制,以通過從屬訪問方式訪問8位、16位或 32位設備;其9個可編程的通用I/O,可用于對功能電路進行控制。PXI總線接口電路原理圖如圖2所示。為了減小單板上的PCI總線的信號線分支對總線的影響,必須對總線信號進行串聯電阻匹配。PCB的布線特征阻抗應設計為65Ω±10%,匹配電阻阻值為10Ω。這里僅用到J1連接器,需要加串聯匹配電阻的信號為:AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、TRDY3、STOP#、LOCK#、IDSEL、DEVSEL#、PERR#、SERR#、RST#、INTA#、INTB#、INTC#、INTD#。PXI總線的信號線長度,必須符合Compact PCI規范的要求,串聯電阻的Stub(短線)長度應進行限制,Stub長度越短,Compact PCI對總線的沖擊越小。PXI總線的信號線長度限制如圖3所示。在單板上,對預充電的信號,從接插件J1(或J2)插針到PCI9030接口器件引腳,總的信號線長度應小于38.1mm,其中,從接插件插針到串聯電阻的PCB連線長度應小于15.2mm,預充電電阻的Stub長度最好是零,最長不能超過2.5mm。

PXI總線及FPGA控制電路具有如下功能:①內部集成了功能電路所需的各種寄存器,分別為狀態/控制寄存器、校準ROM寄存器、序列地址寄存器、跳轉地址寄存器、功能配置寄存器、輸入輸出控制寄存器、狀態/時鐘源寄存器、時鐘校準寄存器。②利用PXI總線提供的星形觸發總線及局部總線,完成時鐘信號" title="時鐘信號">時鐘信號的傳遞,減少了時鐘信號到達各個模塊的傳輸延遲" title="傳輸延遲">傳輸延遲,傳輸的時鐘信號電平為ECL/TTL電平;③具有16位數據線的傳送能力,通過對某一地址的讀、寫操作,完成圖形文件數據的加載、記錄存儲器存儲的響應圖形數據;④監視功能電路的中斷請求,可通過軟件設置和外部跳線來設置中斷級別,向PXI總線發中斷請求信號,完成中斷菊花鏈的傳遞,并將邏輯地址放到數據線上;⑤根據各個通道對應寄存器的配置,譯碼實現各個通道的控制信號,并確定其工作方式。

3 功能電路的實現

數字輸入/輸出模塊的功能電路的組成框圖如圖4所示,它能實現如下六種工作狀態:①圖形文件的加載。通過對數據總線寄存器的寫操作,在16位地址發生器的作用下,將8位的圖形數據和4位的控制數據裝進容量為64K×4的三片靜態存儲器中。②圖形文件的讀取。在對響應圖形數據記錄完成后,通過對數據總線寄存器的讀操作,可以獲取某一地址段或全部地址的圖形數據,讀入到指定的文件中,并與預期正確的圖形文件相比較,判斷被測單元的性能狀態。③圖形數據的激勵。圖形文件加載完成后,在激勵時鐘的作用下,同步16位地址發生器和輸出觸發器,輸出某一地址段或全部地址的圖形數據,或跳轉到某一指定地址的數據,在輸出端口輸出高電平、低電平或高阻狀態。④圖形數據的響應。當激勵時鐘加在輸出端時,精確計算圖形數據經往返的通道和被測單元所產生的延遲T,使激勵時鐘延遲相同的時間T,形成響應時鐘,加到數據輸入端,同步記錄激勵所產生的響應數據,在16位地址發生器的作用下,存儲在64K×4的靜態存儲器中,完成圖形數據的記錄。⑤PXI總線數據直接輸出。PXI總線數據通過軟件的寫操作直接加到輸出觸發器,而不經過靜態存儲器存儲。⑥PXI總線數據直接輸入。PXI總線數據通過軟件的讀操作。直接訪問輸入觸發器,而不是讀取靜態存儲器存儲的響應數據。

數字輸入/輸出模塊使用的激勵或響應時鐘經PXI局部總線加到時鐘選擇單元。當通道定義為輸出時,通過多路選擇器選擇六路時鐘信號中的一個,加到輸出通道上;當通道定義為輸入時,則選擇響應時鐘。激勵時鐘和響應時鐘由時鐘模塊產生,響應時鐘是激勵時鐘經N×6.25ns的延時所得,以補償激勵信號經被測電路和往返通道所產生的延遲。同時,同一時鐘信號加到同一模塊的不同輸出端,也會產生傳輸延遲,采用可編程延時器AD9500產生精確延遲時間,補償不同通道間的傳輸延遲。延遲補償電路采用MOTOROLA公司的MC10H系統的ECL電路,具有速度快、邏輯功能強、扇出能力高、噪聲低、引線串擾小和自帶基準源等優點。先將時鐘信號由TTL電平轉換為ECL電平,由于AD9500具有2.5ns~10μs的可編程延遲范圍,它由8位數碼編程產生所需要的延遲信號,補償不同通道間的傳輸延遲,補償后的時鐘信號再由ECL電平變換為TTL電平,加到各個輸出通道,記錄或響應圖形數據。

基于PXI總線的數字輸入/輸出模塊采用了可編程器件和ECL電路,實現了圖形數據的輸入和輸出,基本上達到了HPE1451/1452輸入/輸出模塊所具有的功能。該模塊具有可靠性好、精度高、功耗小的特點,適用于要求高質量數字激勵/響應測試并保持一定時序關系的應用場合。它能模擬信號圖形,也可以通過編程產生DUT正常工作所需要的數字圖形、控制、應答及時鐘等信號,可廣泛應用于數字系統的在線故障診斷、總線仿真、微處理器仿真以及電子裝備故障診斷中。

參考文獻

1 奚文駿,馮玉光. PXI數字I/O的工作模式及軟件實現[J]. 電子產品世界, 2002(12): 32~35

2 萬世豪. PXI技術發展與近況[J]. 今日電子, 2003(6): 53~55

3 PCI9030 Data Book.PLX Technology Inc. 2000.4

4 王建永,李德華. PCI9030及其應用[J]. 計算機與數字工 程,2003;(1): 22~27