摘要:本文從分析DVI接口的工作原理入手,探討了基于DVI 接口的LED視頻控制系統。該系統取代了傳統的VGA接入方式,不需要進行 A/D轉換和處理,減少了信號損失,有利于提高整個顯示系統的性能。

關鍵詞:DVI接口;T.M.D.S.鏈路;LED顯示屏;FPGA

引言

目前,大多數LED視頻系統都是通過 VGA接口從計算機獲取數據源,但在LED顯示系統中,信號經過多次轉換,難免會造成一些圖像細節的損失。

DVI(數字視接口)的工作原理就是將顯卡產生的數字信號原封不動地傳輸給數字顯示器,在信號傳輸過程中沒有任何信號損失,并且能有效防止外界雜散信號的干擾。因此,研究設計基于DVI接口的LED視頻控制系統有較強的實用價值。

DVI概述及工作原理

DVI是由 DDWG(數字顯示工作組)組織制定的高速數字信號傳輸接口技術,有DVI-D 和DVI-I 兩種不同的接口形式。目前應用主要以DVI-D為主。

DVI 采用T.M.D.S.(轉換最小差分信號)技術來傳輸數字信號。T.M.D.S.是一種微分信號機制,可以將像素數據編碼,并通過串行連接傳遞。DVI 接口協議支持單鏈路 T.M.D.S.和雙鏈路 T.M.D.S.兩種方式。單鏈路的傳輸速率可達 4.9Gbps,具有3個數據通道及1個頻率信號對。單 T.M.D.S.鏈路只提供 24位色深,當用戶要求的色深超過 24位時,并且系統已經確認顯卡和顯示器都支持雙鏈路T.M.D.S.時,系統會啟動雙 T.M.D.S.鏈路。本系統僅用到單鏈路。

控制系統設計

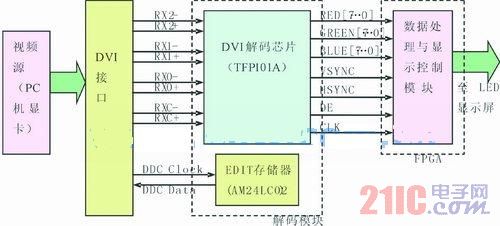

本系統由視頻源、解碼、數據處理與顯示控制三部分組成,如圖1所示。

圖1 系統原理框圖

解碼模塊

DVI 接口支持即插即用功能,要求接收設備符合VESA的DDC2B或更高版本的通訊協議,DDC2B構建在I2C總線上,通過DDC(顯示數據通道)通道來傳遞顯示設備的EDID(擴展顯示標識數據),從而實現PC機對顯示設備的識別和正確配置。EDID內部包含了顯示設備的EDID版本信息、色度系數,以及可支持的分辨率、場頻、行頻等參數。

EDID數據存放在DVI解碼電路的AM24LC02芯片中,該芯片為2Kb(256×8),I2C 總線、CMOS工藝的串行EEPROM存儲器。電源VCC的范圍為 2.7V~5.5V,可以通過把 WP引腳接電源來對整個存儲器寫保護,此時,存儲器的內容不可更改。將DVI接口插座的第16腳(熱插拔檢測端)通過1KW上拉電阻和第14腳(+5V電源端)相連,構成顯示設備的HPD (熱插拔檢測)信號。AM24LC02芯片的時鐘線(SCL)、數據線(SDA)和DVI接口插座的第6、7腳相接,當系統上電時,AM24LC02 在時鐘 SCL 的同步控制下通過 DDC 通道向PC機傳送 EDID數據。只有當PC機識別和正確配置后,TDMS鏈路才會被激活。

TFP101A 是一種T.M.D.S.信號接收芯片,通過檢測DE信號的狀態轉變來確定鏈路的激活狀態。如果106個像素時鐘過后,DE狀態未發生變化,則認為鏈路未激活,輸出SCDT (同步檢測指示信號) =0;在SCDT=0的情況下,如果發現在1024個像素時鐘內DE信號有兩次轉變,則認為鏈路已激活,輸出SCDT=1。RX2-和 RX2+表示紅色數據的差分信號,RX1-和 RX1+表示綠色數據的差分信號, RX0-和 RX0+表示藍色數據的差分信號,分別與DVI接口的單鏈路通道相接(1、2、9、10、17、18腳);RXC-和 RXC+是表示時鐘的差分信號,與鏈路時鐘相接(23、24腳)。TFP101A內部鎖相環回路從時鐘通道獲得同步時鐘,為后繼的T.M.D.S.碼元數據恢復、像素時鐘同步以及T.M.D.S.信號解碼提供參考時鐘,同時也作為前端鎖存器對輸入信號進行4倍過采樣的參考時鐘,T.M.D.S.解碼器將 10位的串行T.M.D.S.編碼解碼成8位并行像素數據以及相應控制信號,并從輸出接口電路將像素數據、控制信號、場同步信號和行同步信號并行輸出。

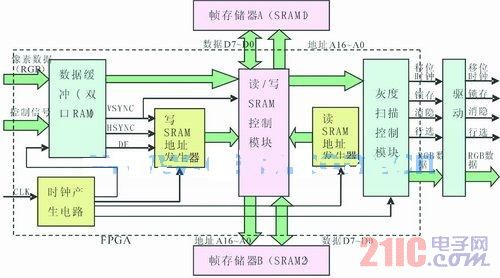

數據處理與顯示控制模塊

數據處理與顯示控制模塊主要負責對顯示數據作進一步地轉換、處理,產生符合 LED顯示屏灰度級顯示的數據,并將其送入驅動電路。數據處理與顯示控制模塊原理圖如圖2所示,主要由數據緩沖處理(雙口RAM)、讀/寫控制、灰度掃描控制、驅動4部分組成,SRAM1、SRAM2 作為幀數據存儲器。

圖2 數據處理與顯示控制模塊原理圖

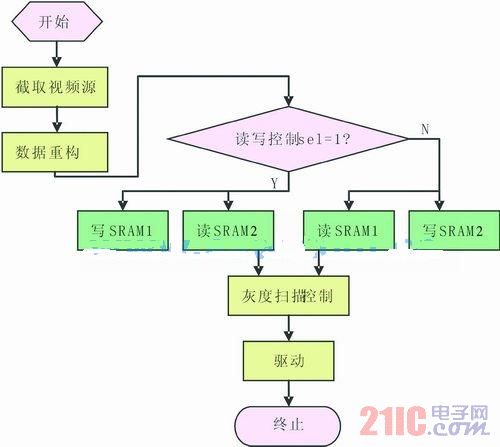

虛線框內的 FPGA 控制器內部的程序流程圖如圖3 所示。主要完成的功能有四個。

圖3 FPGA控制器程序流程圖

一是數據重構。由于本設計采用占空比的方法來實現 LED顯示屏的灰度,每個像素由紅色(R)、綠色(G)、藍色(B)各 8位的二進制數組成,所以計算機一幀的視頻數據信息,在 LED 屏上就需要分 8 次來顯示,依次為 bit0、bit1、bit2、…bit7,通過控制這些不同位視頻數據信息點亮 LED 時間的不同來實現灰度。因此,需要數據緩沖處理模塊(雙口RAM)對每幀圖像數據進行重構。

二是截取視頻源。由于本設計選取的視頻源分辨率為1024×768,刷新率為65Hz, LED屏大小為320×128。所以像素數據寫入雙口RAM的同時,需根據所要顯示的LED屏大小,對重構的像素數據進行相應截取并存入幀存儲器。

三是讀寫控制。當行同步信號HSYNC和數據使能信號DE同時有效時,讀/寫地址計數器同時開始計數。采用ping-pang邏輯,某一時刻幀存儲器A從緩沖區接收數據時,按照分區掃描的規則讀取幀存儲器B內的像素數據,并經并/串轉換后發送至LED屏。兩者輪流切換,保證了數據的高速傳輸。

四是灰度掃描控制。本設計采用占空比控制方法來實現 LED 屏的灰級,整個屏可以分成 8 個區,每個區 16行,每一行每一列的數據可用 8位的二進數表示。對于每一區首先掃描顯示 16 行各列 8位灰度值的 D0 位,然后掃描顯示 16 行各列灰度值的 D1 位。依次類推,直到掃描顯示 16 行各列灰度值的 D7 位。且8個區的掃描是同時進行的。

結語

本設計通過對 DVI 接口技術的深入研究,探討了基于 DVI 接口的LED 視頻控制系統方案。該控制系統取代了傳統的VGA接入方式,運用顯卡的DVI接口作為數據源,不需要進行 A/D轉換和處理,減少了信號損失。因此,不論從信號質量還是后處理考慮,都有利于提高整個顯示系統的性能。