引言

MDB/ICP廣泛應用于自助售賣系統,實際上已經成為自助售賣系統的行業標準通信協議。國內也有采用這個標準的產品,基本上都是采用51單片機作為硬件解決方案,讓功能更強大的處理器S3C2410A支持該協議,可以大大提升自助售賣系統的軟硬件功能。

基于ARM處理器提供了一種讓高端處理器支持MDB/ICP的靈活方法,在該方法的引導下,也可以廣泛應用在MIPS、Power PC等非ARM處理器芯片上,有很強的行業實用性。

1 MDB/ICP協議概述

MDB/ICP協議(Multi-Drop Bus/Internal Communication Protocol)是歐洲售貨機制造者協會制定的一套用于協調自動售貨機的主控制器(VMC)與多個外設(硬幣機、讀鈔機等)之間通信的協議。硬幣機和讀鈔機的標準首先是由Coinco在美國可口可樂公司的指定下開發的。這個標準于1993年被NAMA(National Automatic Merchandising Association)協會采用,經過一個專門的工作組修訂后,于1994年被EVMMA(Euro-pean Vending Machine Manufacturers Association)采用。當前的最新協議版本version 4.O在2009年4月由NAMA和EVA(European Vending Association)共同制定。

1.1 MDB協議串行位格式

MDB接口是工作在9 600 bps波特率的主從型串行總線接口,所有外圍設備(例如硬幣機、紙幣機、讀卡器等)均為主控制器VMC的從機。所有外圍設備與VMC之間的通信方式都一致。最多支持32個外設。

MDB協議的串行位格式為:9600 bps、1個起始位、8位數據、1個模式位(mode bit)和1個停止位。

1.2 MDB/ICP通信協議幀要求

在MDB總線上,VMC通過廣播方式向外發送命令。第一字節為地址字節(高5位為尋址信息,低3位為對外設的指令)。該字節被所有的外設讀取,但只有符合地址字節所指定的外設才處理其后的數據字節,并做出反應。在VMC到外設的數據中,地址字節的方式位被置1,數據字節的方式位被置0,外設通過檢驗接收到的方式位確認是地址命令還是數據。當數據從外設發送到主機時(最長36字節),最后送出的字節方式位被置1,標志著數據發送完畢。

VMC向外設傳送的指令由一個地址字節、一些可選的數據字節與一個校驗和(CHK)字節構成。發送指令后,外設應答VMC的通信塊可以由一個數據塊和一個CHK字節組成,或者一個應答字節(ACK),或者一個無應答字節(NAK)。如果外設應答數據塊的話,VMC將通過一個應答字節(A-CK)、無應答字節(NAK)或發字節(RET)應答外設傳回的數據。

2 MDB/ICP協議應用

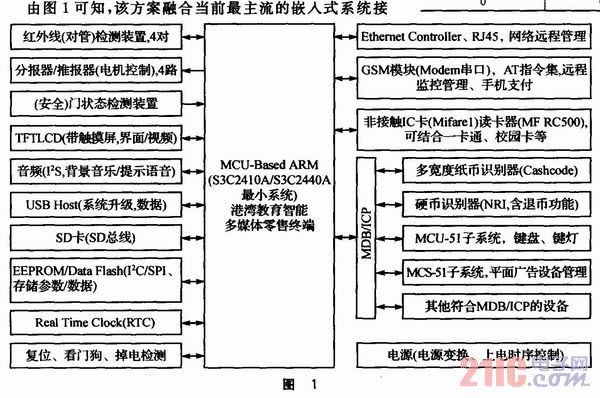

自動售貨機(Vending Machine)是一種全新的商業零售形式,20世紀70年代自日本和歐美發展起來。它又被稱為24小時營業的微型超市。在日本,70%的罐裝飲料是通過自動售貨機售出的。全球著名飲料商可口可樂公司在全世界就布有50萬臺飲料自動售貨機現在,自動售貨機產業正在走向信息化并進一步實現合理化。例如實行聯機方式,通過第三方無線網絡將自動售貨機內的庫存信息和銷售記錄及時地傳送各營業點的電腦中,從而確保了商品的發送、補充以及商品選定的順利進行,實現自動售貨設備的全球連鎖。并且可以通過第三方網絡對售貨終端進行遠程控制和監測,通過以太網控制可以實現設備的云操作,將來也可以接入物聯網實現web操作購物。在市場對功能提出日益復雜化的要求下,傳統的51單片機+MDB設備的解決方案難以滿足市場的需求。在ARM處理器日漸流行的今日,采用S3C2410A來作為VMC是滿足客戶需求的解決方案。S3C2410A芯片功能模塊豐富,軟件支持良好,可以使Linux操作系統實現更為復雜的用戶功能需求。圖1是港灣教育售貨系統的框圖。

由圖1可知,該方案融合當前最主流的嵌入式系統接口,足以實現功能強大的售貨系統來滿足客戶的需求。

2.1 S3C2410A芯片UART串行位格式

通過對S3C2410A數據手冊的研讀,會發現當前一些主流的處理器芯片,比如S3C2410A,UART模塊不像傳統的51單片機一樣正好滿足MDB協議的串行位協議格式,S3C2410A的UART數據格式:最高115 200 bps、1個起始位、5~8位數據、1個奇偶校驗位(odd/even parity bit)、1或2個停止位。

2.2 S3C2410A支持MDB/ICP應用方法

如果要想支持MDB協議,S3C2410A沒有mode bit可用,這樣對MDB總線上的數據判斷是地址字節還是數據字節和總線一幀數據什么時候結束在S3C2410A上無法判斷識別,這對最初制定的方案提出了嚴重的挑戰,迫不得已要對S3C2410A成為MDB/IPC協議的VMC設備的可能性進行預研,最直接的方式就是想到利用S3C2410A的可選的奇偶校驗位的值來逆推MDB設備的mode bit的值,讓奇偶校驗位來充當MDB mode bit的作用,從而來判斷出S3C2410A接收MDB設備傳送的數據是否是結束了。經過分析就可以得到表1所列的推理。

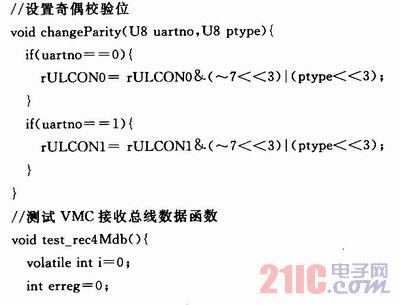

通過上面的分析,開始編寫測試程序,結果發現S3C2410A的串口設計的一個bug:當配置UART LINECONTROL REG ULCONn的BITS[5:3]為“101”,選擇evenparity接收MDB總線的數據的時候,無論是構造出來的數據1的位數為奇數個還是偶數個搭配具體的模式位,發現S3C2410A的UART ERRORSTATUS REG(UERSTATn)的bit2 frame error位并不能準確的置位。想想S3C2410A這么流行的芯片竟然還有設計不完美的地方,幾乎要放棄的時候,本著一切皆有可能的原則,既然芯片都不可靠了,就索性測試一下,按照表1把ULCONn的BITS[5:3]設置為“100”,選擇odd parity接收數據。按常理推斷even parity的結果應該和odd parity結果是一樣的,抱著試一試的態度,構造測試代碼,結果出現了明顯的規律:當模式位為“O”的時候,UERSTATn的bit2 frame error位可以準確的置位;當模式位為“1”的時候,UART TX/RX STATUS REG(UTRSTATn)的bit 0(receive buffer data ready)可以準確置位,正常接收數據。得到這個規律之后,2410 VMC設備就可以準確判斷出MDB設備發送過來的數據是否是收到了結束標志。另外,當VMC向MDB設備發送數據的時候,可以按照協議要求當要發送地址字節時可設置ULCONn的BITS[5:3]為“110”,代表parity forced/checked as 1來把奇偶位強制1充當模式位,地址字節發送結束之后調整ULCONn的BITS[5:3]為“111”來發送數據字節。至此,S3C2410A充當MDB VMC設備可以得到完美的解決。下面是VMC接收總線數據的部分調試代碼片段。VMC向總線發送數據相對比較簡單,有興趣的讀者可以與筆者交流探討。

結語

本文給出了一種在嵌入式處理器ARM(S3C2410A)上實現MDB/ICP協議的實現方法,在工程實踐中,證明該方法準確可靠,滿足了市場的需要,拓展了支持該協議的硬件平臺,豐富了支持該協議設備的軟件功能接口。本文的實現方法也可以應用在其他嵌入式處理器上。