目前,以手機為代表的移動終端設備已經成為集圖像、游戲、商務等多種功能于一體的工作和娛樂平臺。此平臺為了給用戶提供豐富和高質量的視覺享受,大都設置圖像協處理器,由其來完成數字圖像的采集、處理、壓縮、存儲等功能。然而,高速度和高分辨率已經成為數字圖像的方向發展,它們對圖像協處理器的設計提出了更高的要求。

為了使圖像協處理器能夠更快地存儲更多的數字圖像,這里介紹一種以SD卡為圖像存儲器件的圖像協處理器。采用SD卡存儲圖像數據有兩方面的原因:1)SD卡體積小、功耗低,非常符合移動終端設備的系統要求;2)SD卡的存儲容量非常大,目前最高可達到32GB,另外其最高時鐘頻率為25MHz,讀寫的極限速度可以達到12.5MB/s。所以SD卡對于分辨率越來越高、速度越來越快的數字圖像,無疑是理想的存儲器件。

但SD卡控制器對DMA接口的靈活性有較高要求。這首先有協議方面的原因,SD卡控制器每次讀或寫卡的數據量應為512字節的整數倍但在圖像協處理器中提供數據的基帶芯片寫入數據時可能被某個中斷源打斷,故不能保證每次都連續寫入512字節整數倍個數據,所以DMA接口的控制器在此情況下必須能夠使SD卡控制器在寫完已有數據后暫停寫卡操作;其次有速度方面的原因,基帶芯片寫數據的速度與SD卡控制器寫SD卡的速度有很大差異,當基帶芯片要寫入新的數據時,極有可能SD卡控制器還在通過DMA接口讀取數據,所以DMA控制器此時必須能夠使基帶芯片的寫入和SD卡控制器的讀出互不干擾。

本文所設計的可適應于多種時序情況的DMA控制器,被應用于該圖像協處理器之中后,能夠很好地解決上述問題。

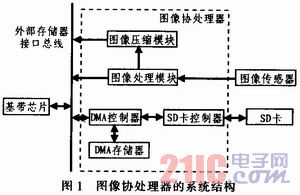

1 圖像協處理器的系統結構

圖1所示為該DMA控制器所處圖像協處理器的系統結構,下面將對其的系統構成和數據流程做詳細說明。

1.1 系統構成

基帶芯片為移動終端設備的系統控制核心。其通過外部存儲器接口總線(External eMI,Memory Interface bus)與該圖像協處理器的控制端口相連。基帶芯片不僅控制著圖像協處理器所有模塊的工作模式,而且負責圖像數據的傳送。EMI總線數據線寬度為16位,其控制的圖像顯示終端為分辨率為320x240的LCD。

圖像傳感器(sensor)為感光器件,其將接收到的光信號轉為電信號,并在內部通過模擬/數字轉換產生數字圖像,在該圖像協處理器設計中采用分辨率為640x480的圖像傳感器,其的工作時鐘為24 MHz。

圖像處理模塊,即ISP(Image Signal Processing)模塊被用于圖像處理,包括去壞點、去噪聲、邊界增強等功能。

圖像壓縮模塊被用于對圖像處理模塊輸出的YUV422格式數據進行JPEG壓縮。

SD卡控制器模塊負責與SD卡的命令和數據交互,所有對SD卡的操作都由基帶芯片配置SD卡控制器的相關寄存器完成。其與SD卡的接口包括CLK(SD卡的時鐘信號線)、CMD(SD卡的命令線)、DATA0~DATA3(SD卡的4根數據線)。在與SD卡的數據交互中,一般是以block(512字節)為

單位的,并且在啟動寫卡命令之后,SD卡控制器必須在250 ms(SD version 2.0)內將所有數據寫入SD卡中。

DMA控制器為基帶芯片與SD卡控制器的接口模塊,用于對寫卡數據和讀卡數據做暫時存儲。其的本質功能是協調基帶芯片和SD卡控制器之間的速度差異。存儲數據的DMA存儲器容量為5 120字節,即10個block數據。

1.2 數據流程

在該圖像協處理器中,所有模塊時鐘頻率均為48 MHz,其被2分頻之后送至圖像傳感器,圖像傳感器以24 MHz頻率送出格式為YUV422的640x480圖像。

該圖像協處理器有2種模式:圖像預覽模式和連拍模式。圖像預覽模式用于拍照前的圖像預覽,拍照者可以在LCD上看到將被拍下的圖像。連拍模式用于連續拍攝圖像,并將每一幅拍下的照片存入SD卡當中。

1.2.1 圖像預覽模式的數據流程

在圖像預覽模式下,圖像傳感器以24 MHz頻率送出分辨率為640x480且格式為YUV422的圖像,幀率為30幀/s。數據被48 MHz系統時鐘同步后送入圖像處理模塊。圖像處理模塊將針對圖像傳感器的特點對圖像進行處理以提高圖像質量,然后將圖像分辨率從640x480縮小至320x240以適應LCD的顯示分辨率,并將數據格式從YUV422轉為RGB565。最后,基帶芯片通過EMI接口將圖像數據讀出,直接寫入LCD的顯示緩沖區后在LCD上顯示出來。

1.2.2 連拍模式的數據流程

當基帶芯片啟動連拍模式后,其首先配置圖像傳感器,使其以10幀/s的幀率送出分辨率為640x480的數字圖像,數據格式仍然為YUV42 2。此時每幀的周期為100 ms,其中幀有效時間為30 ms,幀消隱時間為70 ms。

當數據送入圖像處理模塊后,該模塊仍對圖像進行處理并將圖像分辨率從640x480縮小至320x240,之后將數據格式從YUV422轉為RGB56 5。基帶芯片也仍然通過EMI接口將該圖像數據讀出,并直接寫入LCD的顯示緩沖區中,這樣在連拍的時候,仍可以在LCD上看到被拍下的圖像。

圖像處理模塊在送出預覽數據的同時也將320x240的YUV422數據送至圖像壓縮模塊。為了兼顧壓縮比和圖像質量,一般配置壓縮比在10:1左右,這樣一幅320x240的圖像經JPEG壓縮后的數據量為320x240x2/10=15 360字節。為留出適當的備用空間,圖像壓縮模塊將編碼之后的數據存入一個容量為8 192x16位的存儲器中,在此命名為JPEG_MEM。當一幅圖像編碼完成時,即在圖像傳感器進入幀消隱階段之后,JPEG_MEM中已經存了一幅壓縮之后的圖像。隨后圖像壓縮模塊向基帶芯片發出中斷信號,基帶芯片在從圖像處理模塊接收了當前預覽圖像的最后一部分數據并送LCD顯示后,將響應該中斷,從JPEG_MEM中讀出JPEG格式圖片,存入片外的存儲器中。經實際測試可知,基帶芯片做一次EMI讀取大約需要時間250 ns,因為EMI數據線寬度為16位,所以在此250 ns內基帶芯片將從JPEG_MEM中讀出2個字節,這樣讀完所有15 360個字節需要15 360x250/2=1.92 ms。在基帶芯片讀取JPEG數據之前,其將最后一部分預覽數據讀出并送LCD顯示也需要1 ms左右,至此每幀圖像70 ms的幀消隱時間在基帶芯片讀完JPEG數據后還剩余70-1-1.92=67.08 ms。

當基帶芯片讀完JPEG數據后,將立即準備將數據寫入SD卡中。其首先將操作文件鏈表,在SD卡上為即將寫入的JPEG圖片分配相應空間,并將這些空間的原內容擦除。因為在寫卡和擦卡之后,SD卡需要過一定時間后才能接受新的命令,所以操作文件鏈表和擦卡比較耗時間,一般需要15 ms左右。在此之后,為了提高寫卡速度,基帶芯片先將一部分數據(如512字節)利用DMA控制器寫入存儲器中,這需要的時間為250 nsx512/2=0.064 ms,然后配置SD卡控制器向SD卡發出CMD25(multiply block write conlluand)命令。基帶芯片設置每個CMD25向卡寫入10個block數據。在接收到SD卡發回的響應后,SD卡控制器將利用DMA接口從DMA存儲器中讀出圖像數據并同時將數據寫入SD卡中。在SD卡控制器寫卡的同時,基帶芯片將剩余的9個block數據寫入DMA存儲器。SD卡的時鐘頻率為24 MHz,為其工作在4根數據線模式時,其傳送完所有5 120字節的數據只需要42nsx2x5120=0.43 ms。但是基帶芯片寫完剩余的9個block需要250nsx512x9/2=0.576 ms>0.43 ms,所以從基帶芯片寫第1個block開始到SD卡控制器把最后一個block寫入SD卡大約需要時間為0.064+0.576+0.045=0.685 ms。在此之后,SD卡將進入編程狀態(programming狀態),這段時間因卡而異,在實際調試中使用的卡一般編程狀態會持續5 ms左右。至此基帶芯片完成一次5 120字節的寫卡需要時間為:15+0.685+5=20.685ms。如前所述每幅JPEG壓縮后的320x240的圖片大約為15360字節,即30個block,所以寫完一幅圖片需要的總時間約為3x20.685=62.055ms,其小于前面計算的67.08ms,所以基帶芯片和SD卡控制器可以在每幀圖像的幀消隱時間內完成寫卡操作。

2 DMA控制器的實現

2.1 DMA控制器接口

為了更準確地描述該DMA控制器的工作流程,其主要接口信號介紹如下。DMA控制器與3部分邏輯的接口為:基帶芯片的EMI接口、DMA存儲器接口、SD卡控制器。

1)與基帶芯片的接口 這個接口中,與該DMA控制器關系最密切的信號是host_dma_wr,其為基帶芯片送給DMA存儲器的寫信號,這個信號低電平有效。

2)DMA存儲器接口 dma_memory_addr為DMA存儲器的地址信號。為了能夠保存10個block的數據,DMA存儲器的容量為2560x16=5120字節,所以dma_memory_addr的位寬為12位;drag_memory_datain為DMA存儲器的數據輸入端口,位寬為16位;dma_memory_dataout為DMA存儲器的數據輸出端口,位寬為16位;dma_memory_wen為DMA存儲器的寫使能信號,低電平有效。

3)SD卡控制器接口 dma_req是SD卡控制器發出的DMA請求信號,高電平有效。其為DMA控制器做速度協調的重要信號,如果其為高則表示SD卡控制器要求與DMA存儲器做DMA傳送;如果該信號被置低,可能存在兩種情況,①可能是本次DMA傳送已經完成,②可能是SD卡控制器的讀或寫卡速度低于其操作DMA存儲器的速度,所以SD卡控制器暫停DMA操作;dma_write是SD卡控制器發出的DMA寫標志信號。如果其為1表示SD卡控制器在做讀卡操作,并準備將讀出的數據寫入DMA存儲器;如果其為0表示SD卡控制器在做寫卡操作,并準備從DMA存儲器中讀取數據;dma_ ack是DMA控制器發給SD卡控制器的應答信號,其相當于DMA傳輸數據的有效信號;dma_rdata是DMA讀模式的數據輸出端口,位寬為32位;dma_ wdata是DMA寫模式的數據輸入端口,位寬為32位。

2.2 DMA控制器的工作流程

為了使DMA控制器能更靈活地適應各種操作情況并很好的完成2個操作源(基帶芯片、SD卡控制器)的速度匹配功能。下面將分別就multi-ple block write命令(CMD25)和multiple block read命令(CMD18)對該狀態機的工作流程進行說明。

先將狀態機中的幾個重要變量做如下說明:

dma_num表示在一次多block讀(CMD18)或寫(CMD25)操作中,要向卡寫入或讀出多少個字節的數據。在該圖像協處理器中,每次讀或寫卡都要操作10個block數據,所以dma_num將被設置為5 120;

dma_in_cnt表示在一次多block寫卡操作中,基帶芯片已經向DMA存儲器中寫入了多少個字節的數據;

dam_cnt表示在本次多block操作中,SD卡控制器從DMA存儲器中讀出數據的字節數(DMA讀模式)或寫入DMA存儲器中的數據字節數(DMA寫模式)。

顯然,在該圖像協處理器中,每個CMD18和CMD25完成之后,dam_in_cnt和dma_cnt都將與dma_num相等,且均為5 120。

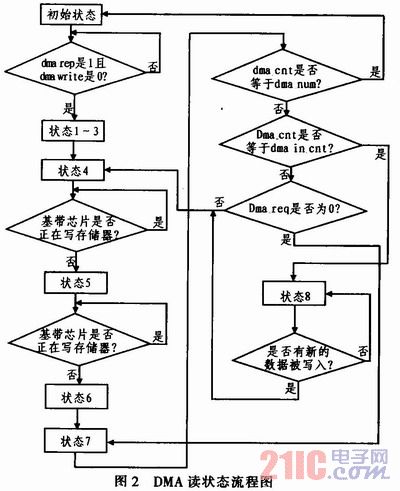

2.2.1 multiple block write

如前所述,每次multiple block write要向卡寫入10個block數據,即10x512=5 120字節。為了提高寫卡速度,基帶芯片首先向DMA存儲器中寫入1個block數據,然后向SD卡發出CMD25(multi block write command)。當SD卡控制器發出CMD25并接收到該命令的應答信號后,立即向DMA控制器發出dma_req信號,準備從DMA存儲器中讀取數據。當DMA控制器監測到dma_req為1且dma_write為0后,將依次進入狀態1、狀態2、狀態3、狀態4。在狀態4中,其會檢查基帶芯片的寫信號host_dma_wr是否有效,如無效,其將從DMA存儲器中讀取當前地址的數據,然后再將DMA存儲器的地址加1并進入狀態5;如host_dma_wr有效,則DMA控制器將等待一個時鐘周期,在下個時鐘的上升沿再去判斷host_dma_wr的極性,若其失效再讀DMA存儲器。也就是說基帶芯片對DMA存儲器的操作有更高優先級,利用這個辦法就可以使基帶芯片和SD卡控制器可以盡量并行工作以加快寫卡速度。在狀態5中,DMA讀狀態機做如狀態4的操作,這是因為dma_rdata的數據線寬度為32位,而dma_memory_data-out的數據線寬度是16位,所以必須要讀2次DMA存儲器再做一次DMA讀傳送。在狀態6中,DMA狀態機將向SD卡控制器發出dma_ack(數據使能信號)和dma-rdata[31:0],隨后進入狀態7。在狀態7中,DMA狀態機將做3個重要判斷,首先其判斷dma-cnt是否等于dma_num,如相等則意味著SD卡控制器在本次多block操作中已經讀取了全部5 120個字節數據,狀態機將回到初始狀態以準備下一次DMA操作;若不相等,則判斷dma_c-nt是否等于dma_in_cnt,若dma_cnt等于dma_in_cnt,則意味著基帶芯片寫入DMA存儲器的所有數據均已被SD卡控制器讀出,DMA存儲器已經為空,但數據量還沒有達到5 120字節,DMA狀態機將進入狀態8即等待狀態,只有基帶芯片寫入新的數據后,SD卡控制器才能回到狀態4繼續讀取數據,這個分支主要是應用于SD卡控制器寫卡速度快于基帶芯片寫DMA存儲器的情況;若dma_cnt不等于dma_in_cnt,則DMA狀態機將檢查dma_req信號的極性,如其為1,狀態機將轉至狀態4讀取下一個32位數據,如為0則意味著此時SD卡控制器寫卡的速度要慢于DMA讀數據的速度,其前面通過DMA接口讀出的數據還沒有完全寫入SD卡,所以SD卡控制器將暫停從DMA存儲器中讀取數據,DMA控制器的狀態機也將在狀態7處于等待狀態,等待dma_req重新為1。當dma_req再次為1后,狀態機將回到狀態4開始新的32位數據的DMA讀操作。最后,當第5 119和5 120個字節被從DMA存儲器讀出后,DMA狀態機將在狀態7中檢查到dma_cnt=dma_num,標志至此,DMA狀態機完成了一次DMA讀操作的全過程。SD卡控制器將向基帶芯片發出中斷信號,基帶芯片響應該中斷后將啟動下一個讀卡或寫卡的命令。其讀狀態流程圖如圖2所示。

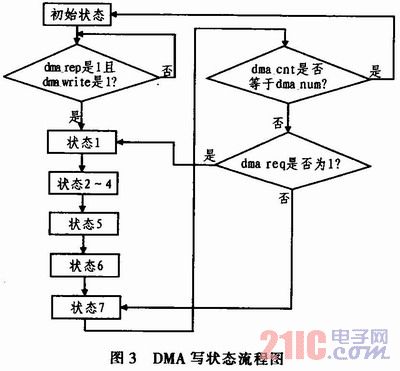

2.2.2 multiple block read

在該圖像協處理器中每次multiple block read要從卡讀出10個block數據并將其全部寫入DMA存儲器當中。當處于初始狀態(狀態0)的DMA狀態機發現dma_req為1且dma_write信號為1時,即明確SD卡控制器將開始DMA寫操作,其將依次進入狀態1、狀態2、狀態3、狀態4。在狀態1中,DMA狀態機會向SD卡控制器發出dma_ack信號,由于存儲器讀存在延時,SD卡控制器將在此后的第二個時鐘上升沿(即DMA狀態機在狀態3時)送出dma_wdata。DMA控制器將dma_wdata暫存一個時鐘周期后,會在狀態4和狀態5中把此32位數據依次寫入DMA存儲器,dma_memory_addr也將在這兩個狀態分別加1。在狀態7中,DMA控制器也將做2個判斷,首先會判斷dma_cnt和dma_num是否相等,若相等說明本次multipleblock read的全部5 120字節數據已經寫入DMA存儲器中,DMA狀態機將回到狀態0等待下一次DMA操作指令;若不相等,則判斷dma_req是否為1,如果為1則意味著繼續做本次DMA寫操作,DMA狀態機也將回到狀態1,開始下一個32位數據的寫入;如果dma_req為0則說明SD卡控制器讀卡的速度較慢,暫時還沒有新的32位數據要寫入,DMA狀態機也將在狀態7處于等待狀態,直至dma_req再次為1,狀態機才回到狀態1,開始寫入下一個32位的數據。最后當DMA控制器在狀態7時發現dma_cnt和dma_num相等,意味這本次DMA操作已經完成,SD卡控制器也將向基帶芯片發出中斷信號,基帶芯片響應該中斷后將從DMA存儲器中讀取此5 120字節數據。其寫狀態流程圖如圖3所示。

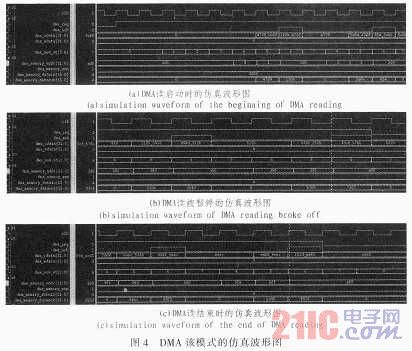

3 仿真結果

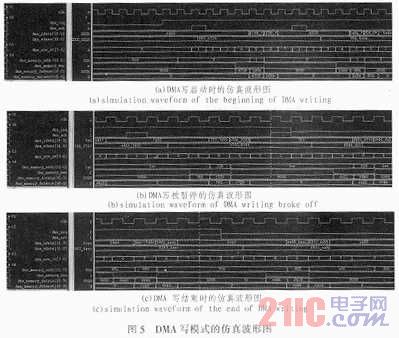

該DMA控制器的核心即為文章第2部分中所述的DMA狀態機,現將multiple block read和multiple block write的幾個關鍵時序情況的仿真波形顯示如下,dma_now_st則為DMA狀態機的狀態變量。

圖4(a)所示為一次DMA讀剛剛開始時,DMA狀態機翻轉情況。在dma_req為1后,狀態機dma_now_st則依次進入各個狀態。在dma_now_st為狀態4時,讀出了DMA存儲器的地址0中的數據16'h4739,在dma_now-st為狀態5時,讀出了DMA存儲器的地址1中的數據16'hlf0b,之后在dma_now_st為狀態6時,此32位數據在dma_rdata端口被送出;

圖4(b)所示的是在一次DMA讀中,SD卡控制器寫卡速度較慢,其暫停DMA讀操作的情況。在DMA控制器送出地址12'h394和12'h395中的數據后,SD卡控制器發現DMA讀的速度較快,有可能覆蓋還未寫入卡的數據,所以把dma_req拉低,暫停DMA讀;

圖4(c)所示的是一次DMA讀的結尾,此時DMA存儲器已經讀完了地址0~12'h9ff中的所有5 120個字節的數據,dma_now_st在狀態7中監測到dma_cnt已經等于dma_num,所以狀態機回到初始狀態0。

圖5(a)所示為在一次DMA寫剛剛開始時,DMA狀態機dma_now_st的工作情況。從圖上可清楚看到當dma_now_st處于狀態4和狀態5時,DMA控制器將dma_wdata端口數據寫入DMA存儲器的地址0和地址1中。

圖5(b)所示為在做DMA寫時,SD卡控制器讀卡速度較慢的情況。當SD卡控制器在dma_now_st為狀態1時送出32位數據32'hb944da21后,其發現已不能在DMA狀態機的下一個狀態1時送出新的32位數據,所以SD卡控制器將dma_req拉低。

圖5(c)所示為一次DMA寫的結尾,SD卡控制器送出最后一個32位數據32'hf83dea95后,已經讀出了所有5 120字節的數據,所以將dma_req拉低。dma_now-st也在向DMA存儲器的地址12'h9fe和12'h9ff寫完最后兩個16位數據后,回到初始狀態狀態0,至此一次CMD18命令操作完成。

4 結束語

隨著消費者對視覺效果的要求越來越高,也必然要求各種移動終端設備的圖像系統功能越來越豐富,性能越來越高,因此圖像協處理器的設計也變得更加重要。在此背景下,處于基帶芯片和SD卡控制器之間的DMA控制器部分將面臨更復雜的工作環境和更高的性能要求。這里所述的DMA狀態機能夠靈活適應基帶芯片操作可能被打斷、基帶芯片寫DMA存儲器可能與DMA讀相沖突等多種信號時序情況,起到了很好的協調基帶芯片和SD卡控制器速度的作用,并使基帶芯片和SD卡控制器能夠盡量并行工作,使操作SD卡的速度達到210 kB/s,在實際工作中取得了很好的效果。