摘要:根據有限沖擊響應(FIR)數字濾波器的原理,綜合運用Matlab" title="Matlab">Matlab和FPGA" title="FPGA">FPGA的QuartusⅡ" title="QuartusⅡ">QuartusⅡ兩大計算機軟件,提出了一種利用QuartusⅡ中參數化宏功能模塊(LPM)的FIR濾波器設計方法。首先利用Matlab設計濾波器系數,再利用QuartusⅡ的LPM構造的乘法器和加法器,最終得到濾波結果。相比分布式算法,該法在信號處理速率要求不高,且濾波器階數較高的情況下,可更加簡單地實現濾波效果。最終在Matlab和Quar-tusⅡ的基礎上,實現了64階的高階FIR數字濾波器電路的設計與仿真。

關鍵詞:FlR濾波器;Matlab QuartusⅡ;參數化功能模塊庫

相對無限沖擊響應(IIR)濾波器,有限沖擊響應(FIR)能夠在滿足濾波器幅頻響應的同時獲得嚴格的線性相位特性,而數據通信、語音信號處理等領域往往要求信號在傳輸過程中不能有明顯的相位失真,所以FIR濾波器獲得了更廣泛的應用。FIR濾波器有多種設計和實現方法,最為常用的是基于分布式算法的FIR濾波器設計。該法利用構造查找表,流水線操作完成濾波過程,極大地提高了系統的處理效率。然而,查找表所要求的系統存儲器容量隨濾波器的階數成指數上漲。本文基于工程實際出發,在信號處理速率要求不高且濾波器階數較高的情況下,提出了一種基于LPM參數化宏功能模塊的FIR濾波器設計方法,具有一定的工程實用價值。

1 FIR濾波器的原理與設計方法

1.1 FIR濾波器的原理

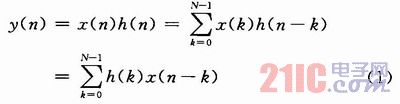

FIR濾波器的數學表達式為:

式中:N為FIR濾波器的抽頭數;x(n)為第n時刻的輸入樣本;h(k)為FIR濾波器第k級抽頭系數。

直接型FIR濾波器結構如圖1所示。

由圖1可見,FIR的濾波過程就是一個信號逐級延遲的過程,將各級的延遲輸出加權累加,即得到FIR的輸出,其中最主要的算法是乘累加運算。由于FIR每完成一次濾波過程就需要進行N次乘法和N-1次加法操作,所以FIR濾波的運算量完全依賴于N的大小。

1.2 分布式FIR濾波器設計

分布式算法(Distributed Arithmetic,DA)早在1973年就已經被Croisier提出,直到現場可編程門陣列(Field Programmable Gate Ar-ray,FPGA)的查找表(Look Up Table,LUT)結構出現,這種算法才重新受到重視,其主要原理如下。

為了分析簡單,將FIR濾波器的表達式(1)改寫為:

可見,分布式算法是一種以實現“乘-加”單元為目的的優化解決方案。利用一個查找表(LUT)實現映射,即用一個2k字寬(即2k行),預先編好程序中LUT接收到的一個K位輸入向量Xb=[X0b,X1b,…,X(k-1)b]的映射,經查找表的查找后直接輸出部分積![]() 。然而,由上述可知,查找表字寬為2k,如果濾波器的抽頭系數過多,則查找表的規模隨抽頭系數的增加成指數級增長,這將使LUT的規模十分龐大。為了減小規模,可以利用部分表計算法,即將一個大的查找表化分為幾個小的查找表,然后再將結果相加。

。然而,由上述可知,查找表字寬為2k,如果濾波器的抽頭系數過多,則查找表的規模隨抽頭系數的增加成指數級增長,這將使LUT的規模十分龐大。為了減小規模,可以利用部分表計算法,即將一個大的查找表化分為幾個小的查找表,然后再將結果相加。

1.3 基于LPM參數化宏功能模塊的FIR濾波器設計

由1.2節可見,分布式算法極大地減少了硬件電路規模,很容易實現流水線技術,不僅使電路的執行速度得以提高,使得信號的處理效率大幅度提高。然而,當系統所要求的處理速度不高時,可利用QuartusⅡ中的LPM參數化宏功能模塊來設計FIR濾波器;當濾波器系數較大時,該法不需要像分布式算法那樣構造龐大的查找表或多個小的查找表。

1.3.1 LPM參數化功能模塊簡述

LPM是參數可設置模塊庫(Library of Parameterized Modules)的英文縮寫,設計者可以根據實際電路的需要,選擇LPM庫中的適當模塊,并為其設定適當的參數,以滿足設計的要求。常用的LPM宏功能模塊有諸如累加器、加法器和乘法器等的算術組件;多路復用器和LPM門函數還有諸如和I/O組件、存儲器編譯器等等的門電路,用戶可以根據自身需要查閱相關的資料。本文正是利用其中的乘法器和累加器來完成FIR濾波器的設計。

1.3.2 FIR濾波器的設計

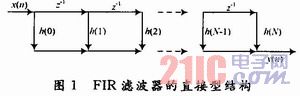

在QuartusⅡ中,利用“Megawizard”向導生成所需的模塊,其界面如圖2所示。

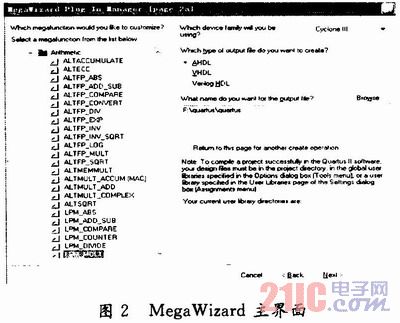

選擇圖中左側Arithmetic中的LPM_MULT得到圖3的界面,根據技術指標選擇合適的參數,即可生成乘法器模塊,按其向導,完成乘法器參數的設置(如乘數的位數,是否有符號數相乘等)。加法器模塊的構造類似,不再詳述。

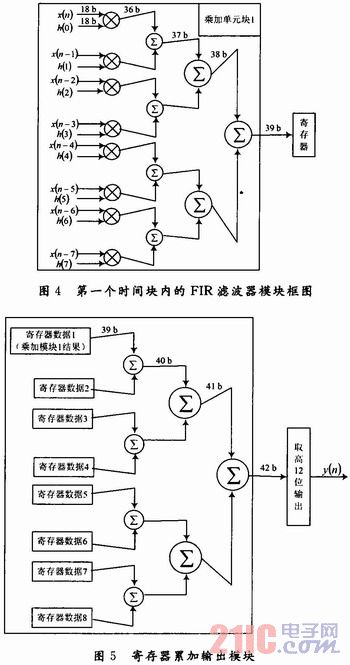

以本文設計的FIR濾波器為例(后面詳述),輸入信號的速率為2 MHz(周期為500 ns),濾波器的階數為64階,由此構造了8個乘法器(最多可以構造25個),分8次完成所有的乘法。相對分布式算法的流水速度而言,構造的乘法器完成一次乘法需要20 ns,相對耗時長一點,但是完成8次乘法也只需8×20=160 ns,小于輸入信號一個周期的時間,因此滿足設計需求。將輸入數據的一個周期平均分為8個時間塊,每個時間內的FIR濾波設計模塊的框圖如圖4所示。

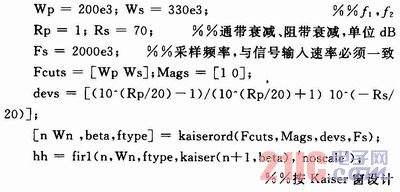

其他7個時間塊內的FIR濾波器模塊同圖4,所不同的是參與乘法運算的信號輸入數據和濾波器抽頭系數不同,分別從x(n-8)到x(n-63)和h(8)到h(63)。待8個乘加模塊的結果均送入寄存器后,再在最后一個時間塊內完成累加得到最終的輸出(相對乘法運算而言,完成累加的時間可以忽略),其實現框圖如圖5。

結合圖4和圖5,可全部完成基于LPM參數化宏功能模塊的FIR濾波器設計。由兩圖可以發現,有多個全加器,且輸入數據的位數(bit數)不同,只要調節LPM宏功能模塊的參數即可方便地完成設計,輸出數據y(n)的位數則根據工程需要取最終累加結果的高12位。取高12位帶來的誤差為![]() (最高位為符號位,不予數值考慮),這是可以接受的誤差。

(最高位為符號位,不予數值考慮),這是可以接受的誤差。

2 基于Matlab和QuartusⅡ的FIR濾波器設計

2.1 利用Matlab進行濾波器系數設計

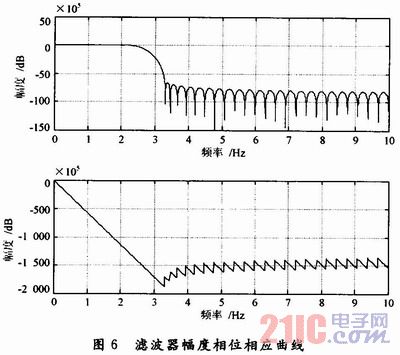

設計指標:采樣頻率為2 MHz,f1=200 kHz,f2=330 kHz,通帶衰減1 dB,阻帶衰減70 dB。通過參數指標確定所需的階數和參數值,部分程序如下:

由圖6驗證設計指標。

如果設計指標不滿足,則可通過調整濾波器參數直至滿足設計要求。

2.2 利用QuartusⅡ進行設計和仿真

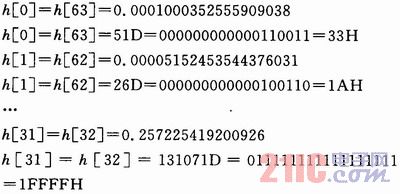

對Matlab產生的FIR濾波器抽頭系數,用QuartusⅡ進行仿真。QuartusⅡ軟件是Altera公司主推的FGPA設計軟件,是集設計輸入、編譯、綜合、仿真、布線、下載于一體的設計軟件。由于Matlab產生的濾波器抽頭系數為小數,根據工程需要將其轉換為18位二進制系數使用。過程如下:

由Matlab產生的FIR數字濾波器系數如下:

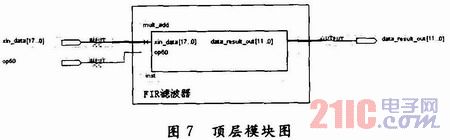

按第2.3節提出的方法在QuartusⅡ中完成FIR濾波器的設計,通過編譯綜合功能對設計文件進行編譯和綜合,然后生成頂層模塊,見圖7。

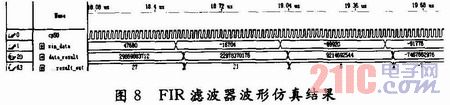

通過QuartusⅡ的波形仿真功能,對其進行波形仿真并進行定量分析。波形仿真如圖8所示。其中,cp50為系統時鐘,由它控制輸入信號xin_data的輸入速率(本例為2 MHz)。data_result為濾波器未經取高位處理的乘加結果;data_result_out,為最終濾波輸出結果。經驗證,data_result與Matlab的運算結果一致,data_result可滿足工程精度的要求。

3 結語

本文在結合Matlab和FPGA軟件QuartusⅡ的基礎上,完成了一種基于LPM參數化宏功能模塊的FIR濾波器設計,該法是基于工程實際應用提出的,它對信號處理速率的要求不高,但對濾波器的階數較高。當設計指標改變,只需調整各模塊的參數,即可完成新的設計,該法已應用在實際工程中。