1 FIR濾波器的基本原理

一個L階的FIR數字濾波器的基本系統函數見式(1):

![]()

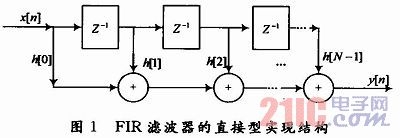

式中:h(n)表示濾波器的系數;x(i)表示帶有時間延遲的輸入序列,此表達式對應的直接型實現結構可用圖1來表示。

可以看出,FIR濾波器是由一個“抽頭延遲線”加法器和乘法器的集合構成的。傳給每個乘法器的操作數就是一個FIR系數。對每次采樣x(n)要進行N次連續的乘法和(N-1)次加法操作,因實際中濾波器的階數都很高,實現高數據吞吐率就需要很多的硬件乘法器,硬件實現時將占用大量的資源,同時也會因此影響濾波器的速度和性能。為了解決這個問題,人們從多個角度尋求優化方法。從數字濾波器表達式看,對它

的優化操作,實際最終轉換成兩類改進。一類是針對輸入xi的DA操作的改進;另一類是針對系數hi編碼的操作。

2 DA算法

分布式算法(Distributed Arithmetic,DA)是為了解決乘法資源問題而提出的經典優化算法這種算法結構,可以有效地將乘法運算轉換成基于查找表LUT(Look Up Table)的加法運算,利用查表方法快速得到部分積。

對于低階而言,由于LUT表地址空間較小,與傳統算法相比,分布式算法可極大地減少硬件電路的規模,提高電路的執行速度。然而當FIR濾波器階數很高時,作為查找表的ROM將很大。階數每增加1位,ROM容量就增加1倍,這種以2的冪次遞增的資源占用是硬件資源不可接受的。因而在濾波器系數較高時,為了減小查找表的規模,常采用一定的方法將大LUT分割為一些小的LUT的方法。如濾波器的多相分解結構、多路復用器和加法器替代查找表的算法等。

3 CSD編碼算法

常數乘法可以通過“移位-加”來完成,而乘數中“1”的個數決定了“加”操作的次數,當然“1”的個數越少越好,正則有符號數字量CSD(Canonic Signed Digit)編碼就可以實現“1”的個數的最小化。

3.1 CSD編碼

與傳統的二進制編碼的二值表示法不同,CSD編碼的數字值域為0,1和-1。-1常表示成1。這種編碼是具有最少非零元素的一種表示法,用CSD編碼表示數字的形式具有惟一性。在實際硬件電路中可以采用如下原則生成最佳CSD編碼:

①從最低有效位開始,用10…0![]() 取代所有大于2的1序列,此外還需要用110

取代所有大于2的1序列,此外還需要用110![]() 取代1011;

取代1011;

②從最高有效位開始,用011代替10![]() 。

。

最佳CSD編碼的特點是:

①在一個CSD數據里,沒有兩個連續的非零位;

②對同一個數字的CSD編碼是獨一無二的;

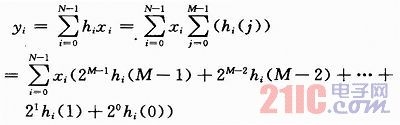

基于CSD編碼,可以將式(1)做以下的變化:

從以上式子可看出,應用CSD表示法,由于可以降低系數中非零元素的數量,因而在運算中能減少加法的次數,有利于提高運算速度和減少資源的占用。

3.2 最佳CSD編碼設計與結果

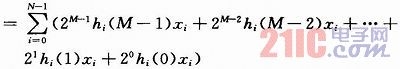

根據前面所列舉的最佳CSD編碼方法,用C語言生成最佳CSD編碼,部分偽代碼如下:

③是數字表示法里,所含非零位數最少,相比于二進制補碼系統平均減少33%的非零項。

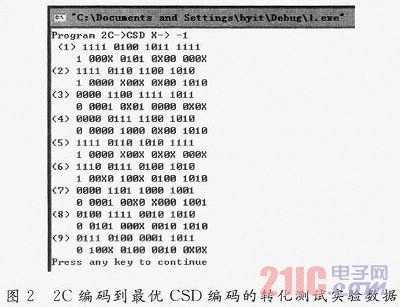

測試實驗數據及結果如圖2所示。在本C語言程序中用X來指代碼,輸入數據為16位。

4 實例設計過程與仿真

4.1 FIR系數提取

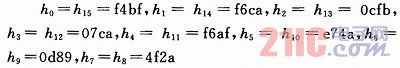

利用Matlab中Fdatlool設計一個16階低通FIR濾波器,各項性能指標為:采用頻率fs=48 kHz,截止頻率fstop=12 kHz,通帶寬度fpass=9.6 kHz。系數數據寬度為16位;輸出數據寬度是16位。為了便于FIR濾波器的FPGA實現,減小誤差,將Fdatlool提取的濾波器的系數量化取整后為:

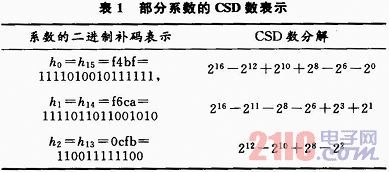

4.2 系數的CSD轉換

讀入量化系數,進行CSD轉換操作,生成CSD碼,表1是部分量化后的系數及對應的CSD數。

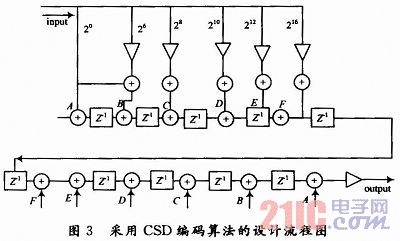

4.3 FIR濾波器實現結構

采用轉置形式的FIR濾波器結構,此結構和直接型結構不同的是,輸入信號X『n』是同時分別和濾波器系數向量相乘,不需要通過不同的延時單元再和相對應的濾波器系數相乘。這種結構最大的優點是工作頻率較高,圖3給出了采用CSD編碼算法的設計流程圖。

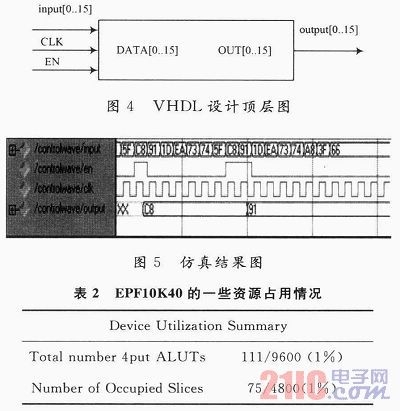

4.4 FPGA實現與仿真

參照圖3中給出的設計流程,使用VHDL語言實現了該常系數濾波器的行為描述,圖4是濾波器的實現頂層圖。FPGA采用AItera公司的EPF 10K40芯片,該芯片最高的單路運行速率為200 MHz。圖5是在MaxPIusⅡ中的仿真結果。表2給出了EPF10K40的一些資源占用情況。

5 基于FPGA的FIR試驗結果

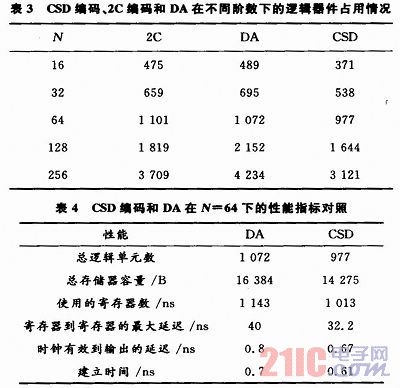

為驗證本文提出的算法的普遍性,以并行DA和2C編碼方式設計了一系列階數從16到256階的FIR濾波器,濾波器在Altera公司的開發軟件MaxPlusⅡ中進行編譯和布局布線,采用的目標器件為EPF10K40芯片,在系統中對3種實現結構進行測試,測試數據位寬為8位。通過表3的比較結果可以看出,使用CSD編碼,資源耗用明顯下降。當FIR階數很高,系數很復雜時,CSD編碼的優勢會更加顯著。表4給出了N=64時DA算法和CSD算法的具體性能指標,從結果來看,CSD編碼相對于單純的DA在系統資源和整個系統延遲上有明顯的提高。

6 結語

濾波器用VHDL硬件描述語言實現,采用Altera公司的EPF10K40芯片,在MaxPlusⅡ中進行了仿真驗證。從結果來看,文中所提出的CSD編碼算法,具有一定的研究價值和實用價值,CSD編碼在處理序列較多的情況下,在資源占用、速度處理方面的效果尤為明顯。采用CSD編碼方式對FIR濾波器進行優化設計,可減少FIR實現的FPGA資源消耗。