系統構成

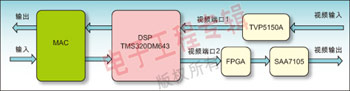

本文介紹的系統是基于TI DSP TMS320DM643與FPGA的完整視頻監控系統,支持1路視頻的輸入和1路視頻輸出,此外還提供網絡接口。

視頻輸入采用TI的高性價比視頻解碼器TVP5150A來實現,TVP5150A可實現兩路復合視頻輸入或一路S-video視頻信號的采集。通過I2C進行寄存器配置,輸出數字視頻信號遵循ITU656標準。

TVP5150A解碼后的數字視頻信號通過DM643的視頻端口1傳送給DSP,由DSP進行必要的視頻處理,由網絡接口輸出給遠端設備。另一方面,DM643把從網絡接收的視頻數據處理后,通過視頻端口2,經過FPGA,由SAA7105顯示輸出,具體結構如圖1所示。

輸出部分采用SAA7105實現。SAA7105是NXP公司的一款高性能視頻編碼器,可提供復合視頻輸出、VGA視頻輸出以及HDTV高清視頻信號的輸出。SAA7105的控制也通過I2C實現,接收復合ITU656標準的數字視頻信號。

視頻處理部分采用的是TI的DSP TMS320DM643來實現。DM643主頻可達600MHz,有2個20位的視頻端口,視頻端口支持BT.656、Y/C等數字視頻接口,DM643還集成了網絡MAC,可實現網絡接入。

硬件性能的發展速度總是很難滿足軟件的需求。在視頻處理越來越復雜的應用中,DSP承擔著繁雜的視頻處理任務,資源變得非常緊張,所以在本系統設計中,采用了FPGA實現OSD的設計,可以減輕DSP的負擔。

OSD實現部分選用的是賽靈思公司的XC3S250E。XC3S250E是賽靈思SPARTAN-3E系列的FPGA,有25萬個邏輯門。

圖1 基于TMS320DM643與FPGA的完整視頻監控系統架構示意圖

OSD實現

SAA7105無法實現OSD功能,而由XC3S250E來實現。主控芯片DM643只需要通知FPGA要顯示的內容和位置,具體的工作由FPGA執行。OSD的邏輯框圖如圖2所示。

圖2 OSD功能框圖

OSD FPGA通過EMIFA從DSP DM643接收OSD數據和控制指令,通過DSP的視頻端口1接收視頻數據,并將OSD的信息疊加到視頻數據上,輸出給視頻編碼器SAA7105。OSD的各功能模塊描述如下。

地址譯碼模塊的數據端口與DSP DM643的EMIFA低32位數據接口,接收DM643發出的數據與控制信息,這些數據和控制信息是DM643發出的原始32位數據。地址譯碼模塊將接收到的OSD數據,如OSD的內容等,以32位數據格式放入到FPGA的內部FIFO中。而控制信息主要是通過一組控制寄存器對OSD實現控制。

與DSP直接連接的模塊還有視頻接口模塊。視頻接口模塊與DSP的視頻端口2相連,存儲來自DSP視頻端口的數據與控制信息。這些控制信息被直接傳輸給OSD多路控制模塊,同時控制信息也直接控制視頻解碼器SAA7105。

OSD控制邏輯把從控制寄存器組得到的控制信息輸出到OSD的各個功能模塊,實現對OSD的控制。寄存器組主要分為兩個部分:一是異步寄存器組,向OSD發送如復位、OSD使能和選擇數據寬度的控制信息;另一個是同步寄存器組,主要控制OSD的位置信息。

OSD解碼模塊根據控制邏輯的控制信息,從FIFO中取出要顯示的數據,以與視頻數據同步的方式輸出到OSD CLUT模塊。從FIFO中獲得的數據是原始的DSP 32位數據,而OSD CLUT模塊需要的數據是8/16位的,所以OSD解包模塊需要以一定的規則將32位數據解包,以視頻端口的頻率將32位數據以8/16的寬度傳輸給OSD CLUT模塊。

FIFO模塊的另外一個功能是向DMA事件發生器模塊傳遞FIFO的狀態信息,如FIFO滿或FIFO空。DMA事件發生器監控這些事件,如果發生,則以中斷的模式發送給DM643,以實現對FIFO的正確讀寫操作。

OSD CLUT模塊為從OSD解包模塊接收的每個象素的數據查找YCbCr的對應值,并控制這些OSD CLUT數據的輸出順序。這種轉換關系是由DSP通過24位的數據端口傳送過來的。OSD CLUT模塊的數據直接輸出給OSD多路控制器模塊。

OSD多路控制模塊根據從OSD CLUT模塊接收到的Alpha控制位確定輸出視頻數據,如果當前為OSD信息,即Alpha控制位有效,則輸出OSD數據給數據轉換模塊。否則,輸出從視頻接口模塊接收的原始視頻數據,以此來實現OSD功能。

OSD多路控制器輸出的數據并沒有直接送給視頻解碼器,而是通過數據轉換模塊,根據具體的應用條件,進行必要的數據格式轉換。由SAA7105的接口時序可知,當SAA7105配置為復合視頻輸出時,其要求的數據為單時鐘沿數據,此時數據轉換模塊不作任何工作,將從OSD多路控制模塊接收的數據原封不動地傳輸給SAA7105;如果SAA7105配置為VGA或HDTV輸出模式時,需要雙時鐘沿數據,此時數據轉換模塊將從OSD控制器接收到的單時鐘沿數據轉換成雙時鐘沿數據,輸出給視頻解碼器SAA7105。

由此可見,FPGA完成了OSD的所有工作。如果要顯示OSD內容,DM643只需要通過EMFIA口向FPGA發送控制指令即可,這些指令當然包括OSD的內容及位置信息。

OSD控制

由XC3S250E實現的OSD設計根據接收到的OSD位置及內容信息進行OSD顯示,對OSD顯示的內容沒有任何限制,非常靈活方便。下面以OSD漢字顯示為例說明OSD的控制操作。

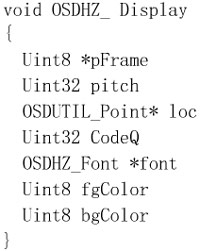

要正確的顯示漢字,就必須將輸入的漢字內碼轉換成對應的區位碼。這一功能我們通過函數Uint32 Code_Converse(unsigned char *CodeNPointer),其輸入為指針,指向要轉換漢字。返回值為該漢字對應的區位碼。OSD的顯示由函數OSDHZ-Display實現:

其中,Uint8 *pFrame為OSD輸出的Buffer緩沖區;Uint32 pitch為每行顯示的象素值;OSDUTIL_Point *loc為第一個字符的顯示位置;Uint32 CodeQ為要顯示漢字的區位碼;OSDHZ-Font *font為顯示漢字所用的字體;Uint8 fgColor顯示漢字的前景色;Uint8 bgColor顯示漢字的背景色。

所以,如果需要顯示漢字,只需要將漢字進行必要的碼制轉換,然后將轉換后的區位碼,給出顯示的位置,輸出給OSD FPGA即可。當然要顯示漢字,漢字字庫是必不可少的。