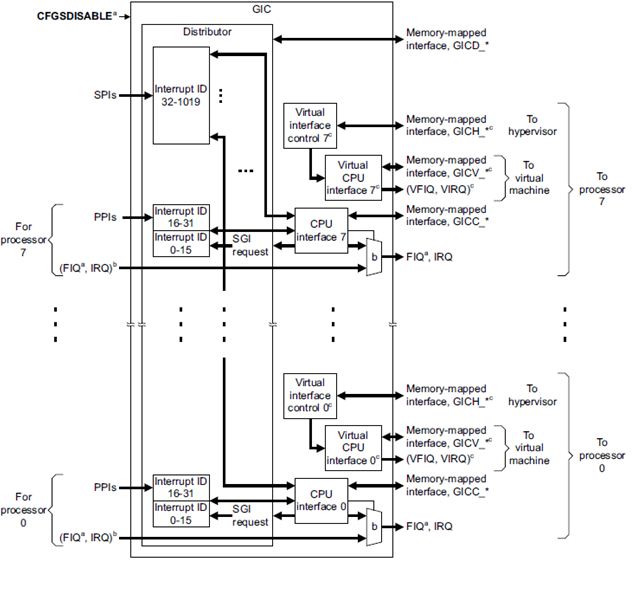

1 GIC : Generic Interrupt Controller

Distributor

–detecting, disabling, prioritizing, directing interrupts to CPU(s).

CPU interfaces

–asserting an interrupt indication to the CPU

Support max to 1020 interrupts

ARM GIC中斷控制器原文詳解" src="http://files.chinaaet.com/images/2012/05/17/086dc520-b7e6-426c-8882-dd6cdfd97fca.jpg" />

2 PPI,SPI and SGI

Peripheral interrupt

PPI : Private Peripheral Interrupt

specific to a single processor

SPI : Shared Peripheral Interrupt

Distributor can route to any of a specified combination of processors

Software-generated interrupt (SGI)

This is an interrupt generated by software writing to a GICD_SGIR register in the GIC. The system uses SGIs for interprocessor communication

ID0-ID15 are used for SGIs

ID16-ID31 are used for PPIs

ID32+ are used for SPIs

3 Models for handling interrupts in MP core

1-N model

Only one processor handles this interrupt. The system must implement a mechanism to determine which processor handles an interrupt that is programmed to target more than one processor.

N-N model

All processors receive the interrupt independently. When a processor acknowledges the interrupt, the interrupt pending state is cleared only for that processor. The interrupt remains pending for the other processors.

According to GIC document(p3-33)

software generated interrupts (SGIs) using the GIC N-N model

peripheral (hardware) interrupts PPI and SPI using the GIC 1-N model.

4 GIC interrupt handling sequence

1. The GIC determines the interrupts that are enabled.

2. For each pending interrupt, the GIC determines the targeted processor or processors.

3. For each CPU interface, the Distributor forwards the highest priority pending interrupt that targets that interface.

4. Each CPU interface determines whether to signal an interrupt request to its processor, and if required, does so.

5. The processor acknowledges the interrupt, and the GIC returns the interrupt ID and updates the interrupt state.

6. After processing the interrupt, the processor signals End of Interrupt (EOI) to the GIC.