1 引言

偵察與監視在軍事斗爭中的地位舉足輕重。在各種偵察/監視技術中,航空偵察占有重要的地位,可見光偵察是一種重要的偵察形式,無人偵察機顯示出了廣闊的發展前景,現代科學技術的發展為現代航空偵察與監視技術帶來了新的發展契機。

航空偵察一個主要的途徑就是利用高性能高速攝像機進行航空拍照,采集各種圖像信息。然而,數字化的偵察圖像分辨率高、信息量大,使后續的處理、傳輸、存儲等過程的實現變得極為困難,從而給機載圖像/視頻系統的設計與實現帶來了巨大的挑戰。為了解決這些問題,本文基于某型高速相機,利用低成本FPGA,構建了一個高性能的圖像采集存儲系統,完成對高分辨率、高幀率偵察圖像的采集和存儲。

2 某型高速相機簡介[1]

系統選擇的高速相機是一款高分辨率、高速度線掃數字相機,其圖像傳感器采用先進的CCD(Charge-Coupled Device)圖像傳感器,采用了世界尖端水平的高靈敏度掃描成像技術——高速率的TDI(Time Delay and Integration)技術、多重曝光技術并加強藍色響應,從而使該型相機可提供比單輸出線掃相機更好的靈敏度特性,總的數據傳輸率可高達200MB/s。

相機接口主要包括后面板上的六個接口:其中四個為數據輸出接口,每個接口包括16位數據信號,1位數據同步信號,1位同步時鐘信號,信號的電平輸出格式為LVDS電平格式;另外兩個接口分別為控制信號接口和電源接口。在控制信號的作用下,相機同步輸出包含同步時鐘信號(STROBE)和水平同步信號(LVAL)在內的 8×8bit標準的灰度圖像數據,圖像分辨率可選擇為4096×30'72(本系統采用分辨率)和2048×3072。

相機控制接口信號中,行觸發信號(EXSYNC)至關重要。它負責圖像數據的觸發輸出,行觸發信號的上升沿觸發數據并指示數據有效。相機觸發要求此信號存在下降沿,最小觸發頻率為300HZ。

3 系統硬件設計及工作原理

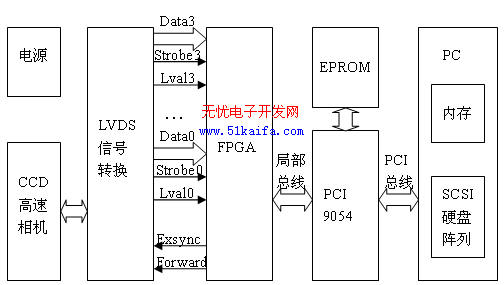

本設計硬件系統主要包括電平轉換,數據接收預處理和數據采集存儲三個部分。圖1為系統硬件原理框圖。在總線結構上,系統采用了滿足高速數據傳輸的PCI總線結構,PCI9054是PLX公司推出的一種32位33MHz的PCI總線主控I/O加速器,它采用多種先進技術,使復雜的PCI接口應用設計變得相對簡單。

從資源和成本方面考慮,FPGA選用Altera公司的低成本Cyclone系列芯片-EP1C6Q240C8。存儲介質則選用SCSI磁盤陣列,它能滿足高速、大數據量的存儲。

圖1 系統原理框圖

系統工作原理:

系統上電,首先完成一系列初始化工作:PC通過底層驅動配置PCI9054的寄存器,使之處于正常工作模式(C模式)[2]; FPGA上電,配置用戶電路(此時,FPGA內部邏輯和PCI9054都處于等待狀態)。

PC應用程序啟動后,向PCI9054發送數據傳輸指令,PCI9054收到數據傳輸指令,通過LOCAL BUS通知FPGA開始工作:FPGA產生行觸發信號(EXSYNC),觸發相機進行拍照、傳輸數據。然后,PCI9054進入工作狀態,開始采集數據,并將數據存儲到磁盤陣列。FPGA內部邏輯和PC應用程序通過行計數判斷一幀圖像傳輸完畢,相繼進入等待狀態。但是,PC應用程序在接收完一幀圖像,進入等待狀態后,延續一定時間,會自動觸發下一個數據傳輸指令通知FPGA開始下一幀圖像傳輸。

3.1電平格式轉換

PCI9054芯片電平格式為3.3V LVTTL格式,相機輸出信號的電平格式為LVDS格式,基于系統總體需要,有必要在進行圖像預處理前將LVDS相機輸出信號轉換成LVTTL格式電平。

3.2數據接收預處理

FPGA完成圖像預處理功能。FPGA是以并行運算為主導的芯片,處理速度更快。數據預處理過程包括:數據緩沖、位并轉換。

數據緩沖[3]:相機利用4個通道輸出圖像數據,每個端口的數據傳輸以本端口時鐘為參考,傳輸過程中由于各種差異如傳輸電纜的長度不同,使得各個端口的時鐘信號產生相對的相位漂移,從而使四個端口數據輸出不完全同步,這不利于圖像數據的同步采集。為消除數據異步,FPGA內部設計了由4個FIFO組成的數據緩沖器組。每個端口的有效數據寬度為16bit,傳送一行4096個數據需用512個時鐘周期,因此FIFO深度設為512個字。相機送來的4個LVAL信號為各對應通道寫使能信號, 4個STROBE信號作為對應通道寫時鐘。FIFO輸出端采用系統時鐘(15MHz)作為統一的數據同步時鐘,并設計一個讀請求信號,當FIFO半滿時讀取數據,經過緩存的數據以與系統時鐘同步的64bit寬度格式輸出。

位并轉換:PCI9054芯片LOCAL端的有效數據位數有兩種選擇:8bit和32bit(可更改9054寄存器設置,為了保證數據采集速度,本系統設置為32bit)。但是相機的輸出數據通過緩沖之后仍然為64bit,為了滿足PCI9054數據采集位數要求,必須將64bit數據進行位并轉換,變成32bit傳輸。本系

統設計在FPGA內部將數據的高32bit和低32bit分別送入二選一BUSMUX的輸入端,系統時鐘的電平選

擇數據輸出。64bit數據轉化成32bit數據傳輸,但數據率變成原來的兩倍(30M/s)。

3.3 數據采集存儲

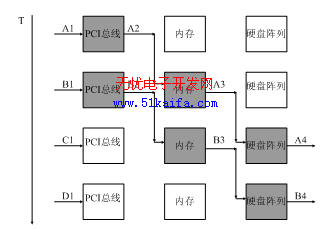

對于整個系統來說,存儲系統的持續存儲速度是個至關重要的參數。數據的采集存儲采用微機為主體,在其PCI總線上掛載一塊SCSI的接口卡和9054接口卡,9054接口卡用于數據采集,SCSI接口卡上掛載兩個SCSI硬盤,組成RAID-0的硬盤陣列,這樣可以大大提高硬盤的持續存儲速度。利用PCI9054進行數據采集時,數據的傳輸路徑為:PCI總線-內存-硬盤陣列。現有兩種傳輸方案可供選擇:第一種為單線采集存儲,顯然,這種方案會降低數據的的采集速度。本系統選用第二種方案:流水線存儲,如圖2所示。理論上,流水線方式的數據采集速度應該是單線采集的兩倍。

圖2 流水線存儲時序示意圖

4 部分軟硬件程序設計

3.4 PCI9054 Local Bus 硬件驅動

PCI9054局部總線是外設(FPGA)和9054之間通信的橋梁。9054圖像數據的采集需要使9054局部總線信號滿足一定的時序要求,保證數據傳輸的同步,即需要FPGA端硬件驅動。驅動是用Verilog HDL代碼編寫的一個狀態機,代碼如下[2][4]:

always @ (posedge CLK)

begin

casex (CurrentState)

1'b0: begin

if (!LLADS_)

begin LLREADY <= 1; CurrentState <= 1; end

else begin LLREADY <= 0; end

end

1'b1: begin

if (LLBLAST_) //突發循環重復

begin LLREADY <= 1; CurrentState <= 1; end

else //最后一個循環

begin LLREADY <= 0; CurrentState <= 0; end

end

default:

CurrentState <= 0;

Endcase end

assign LLREADY_ = (LLREADY) ? 1'b0 : 1'b1;

4.2 PCI9054驅動層和應用層設計

系統所用PCI采集卡非windows標準硬件,驅動程序需要自行開發,這里使用WDM編程。為了提高速度采用雙線程操作。由于寫磁盤比較慢,如果等寫完磁盤再讀local bus顯然效率太低,所以啟動雙線程雙buffer讀寫數據[5]。

部分程序代碼:

BOOL GetData()

{ ……

//創建等待驅動中斷線程以及寫文件線程

hEvent_Disk=GreateEvent(NULL,TRUE,TRUE,NULL); hEvent_Mem = CreateEvent(NULL,TRUE,FALSE,NULL);

_beginthread(WaitForDataThread,0,NULL); _beginthread(WriteDiskThread,0,NULL);

//啟動DMA傳輸

SetDma(); BlockDmaLocalToPci(dmabuffer, BLOCK_ONE_DMA);

}

void WaitForDataThread(void * pParam)

{}

void WriteDiskThread(void * pParam)

{}

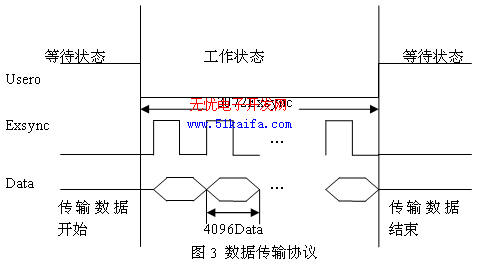

4.3 數據傳輸指令生成

PC應用程序產生數據傳輸指令,觸發數據傳輸。指令的產生是通過9054在PC端的底層驅動,設置9054 LOCAL端USERO管腳電平,使FPGA進入工作狀態,并產生相機行觸發信號(EXSYNC),觸發相機拍照傳輸數據。USERO信號為高電平時,FPGA和9054都處于等待狀態;USERO下降沿觸發數據傳輸,使FPGA和9054進入工作狀態;數據傳輸完畢,USERO拉高。時序如圖3。

5系統測試及工程考慮

本系統測試微機環境為:CPU,Pentium(R) 4. 2.40GHz;內存,333MHz,512MB/s;北橋芯片,845PE;操作系統,Windows Server 2003;SCSI硬盤空間,120G。

系統測試結果:圖像單線穩定存儲速率為37.2 MB/s ,流水線穩定存儲速率為71.2MB/s;持續記錄時間為25分鐘。

工程考慮:系統速度主要限制于兩個瓶頸,一是硬盤本身,二是PCI總線。本系統雖然采用了高速硬盤,但還有一個操作效率的問題。數據從FPGA到PCI9054的傳輸介質采用一般硬盤線,此類硬盤線的上限頻率為33M,限制數據采集速度;同時由于系統需要通過PCI總線轉移數據,而計算機的PCI總線多為32位、33MHz的總線,這個總線的理論數據為132MB/s,當總線上僅僅有一個設備時,實測實際總線持續傳輸速率在100MB/s以下,當總線上再掛載磁盤適配器時,總線的數據傳輸速率會更低。系統穩定性主要取決于FPGA內部邏輯的容錯性和微機的穩定性。在高速存儲的環境下,微機系統容易死機,因此微機選擇具有高穩定性的Windows Server 2003操作系統作為圖像采集的存儲環境。