片上系統(SoC)是在單一芯片上實現信號采集、轉換、存儲、處理和I/ O接口等多種功能,具有面積小、功耗低、設計時間短、成本低和高性能指標等特點. SoC設計的核心是IP 核設計. 在SoC的模擬集成電路設計中,使用簡單的電路結構來實現高性能成為模擬電路設計的趨勢. 運算放大器是模擬電路最重要的電路單元,但是隨著電源電壓的不斷降低,常規設計的運放受閾值電壓及飽和電壓降的影響而導致運放的輸入輸出動態范圍不斷減小,影響后級電路的正常工作. 為了增大運算放大器的動態范圍,出現了Rail-to-Rail 結構.

通常的兩級Rail-to-Rail 運放包含復雜的AB類輸出級,它占用很大的芯片面積. 而且AB類控制會增加運放的噪聲和失調電壓.雖然有的運放克服了上述問題. 然而, 由于使用了復雜的浮地電流源來偏置求和電路和AB 類輸出級,輸入級跨導隨共模電壓發生很大的變化,使得頻率補償特性難以達到最佳. 此外,輸出晶體管的瞬態電流隨電流電壓變化 .

筆者提出了一種基于SoC應用的5V Rail-to-Rail 運算放大器,其中輸入級采用互補差分對輸入. 運放的輸出級不同于以往復雜的AB類輸出級,也不同于使用浮地電流源來偏置求和電路和AB 類輸出級的電路,而是采用分壓電路來實現. 整個運放IP核的電路結構簡單有效,非常適合SOC應用.

1 電路結構

1.1 輸入級

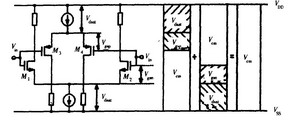

通常,運算放大器的輸入級均采用匹配性能好,失調、溫漂很小的差分放大電路. 為了使運放的共模輸入在整個電源范圍內變化時電路都能正常工作,采用NMOS管和PMOS管并聯的互補差分輸入對結構來實現輸入級的Rail-to-Rail.基本的Rail-to-Rail輸入級結構如圖1 所示,M1-M2 為NMOS 差分輸入對,M3-M4 為PMOS 差分輸入對.

圖1 基本的Rail-to-Rail 輸入級結構

Rail-to-Rail 輸入級的工作原理如下,其共模輸入電壓范圍如圖2所示.

圖2 Rail-to-Rail運算放大器共模輸入電壓范圍

PMOS差分輸入對共模輸入電壓范圍為VSS < VCM < VDD - Vdsat -Vgsp , NMOS差分輸入對共模輸入電壓范圍為VSS + Vgsn + Vdsat < VCM < VDD,其中VCM為共模輸入電壓, Vgsp為p管的柵源電壓, Vdsat為電流源兩端電壓, VDD為正電源, VSS為負電源, Vgsn為n管的柵源電壓.輸入級所需要的最小電源電壓為Vsup ,min = Vgsp + Vgsn + 2Vdsat . 當電源電壓大于Vsup ,min 時,輸入級能夠正常工作,總的共模輸入范圍為VSS < VCM < VDD , 從而實現了輸入級的Rail-to-Rail .所設計的運放輸入級工作在亞閾值區,根據輸入共模電壓的不同,輸入級電路可分為3 個工作狀態 :

當共模電壓接近VDD 時,NMOS差分輸入對處于放大工作狀態,輸入級跨導為gm = gmn = In/( nnVth) ;當共模輸入電壓接近VSS時,PMOS 差分輸入對處于放大工作狀態,輸入級跨導為gm = gmp = Ip/ ( npVth) ; 當共模電壓處于中間值時,NMOS輸入對和PMOS輸入對均處于放大工作狀態,輸入級跨導為gm = gmp + gmn = Ip/( npVth) + In/ (nnVth) . 其中In和Ip分別為NMOS和PMOS輸入管的漏級電流, np和nn分別為NMOS和PMOS輸入管的弱反型斜率因子, Vth是熱電勢kT/q , 為26mV.

1.2 輸出級

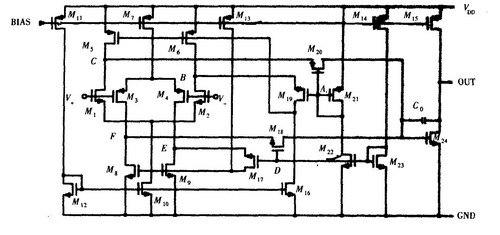

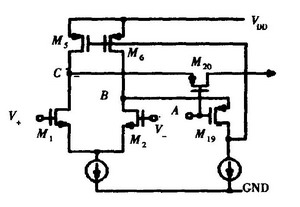

整個運算放大器采用對稱結構(如圖3) ,并且運用分壓電路進行求和. M5 , M20 , M18 和M8 構成分壓支路. 分壓支路中M5 和M20 與M8和M18的阻抗變化機理相同,因此僅描述M5 和M20 的阻抗變化. 電路如圖4 示,圖中A 點電壓恒定, M6 工作在飽和區. 根據輸出電阻公式

r0 = 1/ (λID) , (1)

( λ為溝道長度調制系數) ,當輸入電壓變化時, M1和M2 的漏級電流變化,圖中B 點電壓會發生變化, 但因M19引入一個負反饋, 使得B點電壓恒定. 根據飽和區

![]()

線性區

![]()

由式(1)~(3)知, VGS的變化使得M5和M6的漏級電流變化,導致阻抗變化和C點電壓變化. C點電壓變化使得M20在線性區和飽和區之間變化,因此M20 的阻抗發生很大變化. 同理,輸入電壓變化時,M8和M18的阻抗發生變化,變化趨勢與M5和M20相反. 因C點、F點電位分別接近VDD和GND,M24的柵壓在VDD和GND之間變化. 運放的第2級放大采用簡單的共源級放大,以提供最大的輸出擺幅. 為使放大器有良好的頻率響應特性,采用了Miller電容補償技術 .

圖3 Rail-to-Rail 運算放大器結構

圖4 阻抗變化機理圖

2 仿真結果與討論

電路采用上華0.6μm DPDM CMOS工藝,基于BSIM3V3 Spice模型,用Hspice進行仿真. 電源電壓為5V ,偏置電壓為3. 7V. 輸入級的跨導隨輸入共模電壓變化的結果如圖5 所示. 輸入級跨導變化兩倍,跨導在0.8V到3.85V之間恒定,為190μs. 跨導變化是因為輸入共模電壓在中間值時,輸入級跨導為NMOS和PMOS輸入對跨導之和,而在共模電壓接近GND或VDD時,輸入級跨導分別為PMOS和NMOS輸入對的跨導.

圖5 輸入級跨導曲線圖

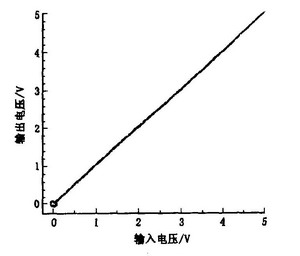

將運放接成電壓跟隨器的形式,測量其單位增益響應,仿真結果如圖6所示. 從圖6 可以看出,放大器的輸入輸出達到了整個電源電壓范圍.運算放大器的幅頻、相頻特性如圖7所示,整個電路的直流開環增益達107.8dB ,相位裕度為62.4°,單位增益帶寬為4.3MHz.

圖6 單位增益傳輸特性曲線

圖7 運算放大器幅頻、相頻特性

整個運算放大器的設計結果如表1所示. 運算放大器的整體性能比較好,并且在5V的電源電壓下,功耗只為0.34mW. 此外,運放的對稱性好,結構緊湊,版圖面積小,只為0.05mm2 ,非常適合SoC的應用.

3 總 結

從IP核設計的角度出發,筆者設計了一種結構簡單、低功耗、高增益的Rail-to-Rail CMOS運算放大器.輸入級采用互補差分對結構,輸出采用分壓電路進行求和,再接以PMOS為負載的共源級進行放大. 較以往的Rail-to-Rail運算放大器大大簡化了結構,對稱性好,版圖面積小,易于實現. 模擬結果表明運放的輸入輸出都達到全擺幅,且增益和相位裕度分別為107.8 dB和62.4°,功耗只為0.38mW,非常適于做成SoC的IP核.