1 引言

通用串行總線USB(Universal Serial Bus)接口以其通信速率快,USB2.0協議速率達480 Mb/s,支持熱插拔的特點得到廣泛應用,緩解日益增加的PC外設與有限的主板插槽和端口之間的矛盾;而低壓差分信號LVDS(Low-Voltage Differential Signaling)接口作為一種新型的高速串行。低噪聲的數據傳輸接口,廣泛應用于視頻傳輸領域,實現USB與LVDS接口轉換,使在只有USB接的情況下便可實現雙視頻顯示的連接,進一步擴展兩種接口的使用范圍,從而在一定程度上解決主板插槽與端口日益匱乏的問題。

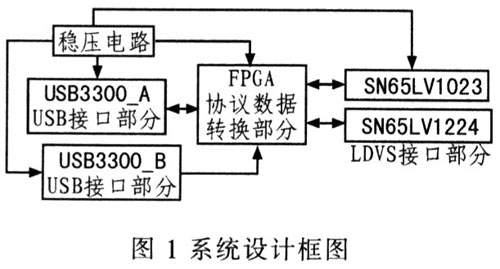

2 系統概述

該系統設計主要由穩壓電路,USB接口,基于FPGA的協議數據轉換以及LVDS接口等部分組成,其系統設計框圖如圖1所示。該系統設計的USB接口使用高速USB物理層收發器USB3300將USB協議的差分信號轉換成8位的并行信號后,再與FPGA交互數據,從而避免FPGA直接與USB協議的物理層交互數據,簡化FPGA可編程門陣列編程。基于同樣思想,系統LVDS接口部分采用SN65LV1023與SN62LV1224,將低壓差分信號轉換成 10位的并行信號再與FPGA進行數據交互。通過專用轉換器USB3300,SN65LV1023,SN65LV1224使得FPGA只與并行信號和相應的控制信號連接,而不與USB協議和LVDS協議的復雜物理層信號交互,從而較為簡單地實現協議數據轉換的軟件編程。

系統設計使用兩片USB3300,其中USB3300 A與主機PC的USB接口相連,將主機傳輸的USB協議數據轉換后,通過與FPGA的數據交互以及FPGA的協議數據轉換,轉換成10位并行信號,輸出給 SN65LV1023,最后以LVDS協議的低壓差分信號輸出,實現USB接口到LVDS接口的轉換。而SN65LV1224與主機的LVDS接口連接,將LVDS協議的數據轉換成10位并行輸入FPGA進行協議數據轉換后,再將8位并行數據與USB3300_B進行數據交互,最后以USB協議的差分信號輸出,從而實現LVDS接口到USB接口的轉換。

3 系統硬件設計

3.1 穩壓電路

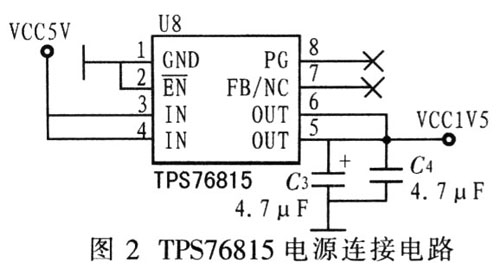

該系統設計需要提供5 V和3.3 V的穩定電壓信號。于是穩壓電路部分使用TPS76815向系統提供5 V的電壓信號,TPS76815電路連接如圖2所示,使能麗引腳接地,為除去毛刺則在OUT端接4.7μF和0.01μF的電容濾波,使用 TPS76833提供3.3 V電壓信號。TPS76833連接電路與TP$76815類似。

3.2 USB接口電路

因為USB協議的物理層定義過于復雜,采用FPGA現場可編程邏輯門陣列與USB協議物理層交互難度太大,同時也很難滿足數據收發時序同步要求。所以應在與FPGA數據交互前進行必要的數據轉換。因此,考慮使用USB控制器。而一般的 USB控制器只支持USB1.1協議,并不滿足高速傳輸要求.而轉換后的數據也較復雜。不利于協議數據轉換部分的編程。本系統應用SMSC公司開發的高速 USB物理層收發器USB3300。USB3300使用低引腳計數接口(ULPI)連接ULPI兼容鏈路層。ULPI接口在鏈路層和PHY之間采用傳輸頻帶內信號和狀態字節的方法,將引腳數從UTMI+接口的54降低到12。這樣大大降低USB協議物理層與FPGA數據交互的難度,易于軟件編程。

USB3300連接電路如圖3所示,為控制數據傳輸的時序同步,采用USB3300的時鐘輸出工作方式。USB3300外接24 MHz的時鐘晶體振蕩器,經內部鎖相環電路轉換為60 MHz信號,通過CLK輸入FPGA作為其時鐘信號,從而實現FPGA與USB3300的時鐘同步。USB接口部分與FPGA的數據交互傳輸通過雙向的8 位數據信號實現,USB3300通過DIR與NXT信號輸出控制數據信號的傳輸方向,而FPGA通過STP信號控制數據的傳輸方向USB3300的狀態。這樣便實現FPGA與USB3300的數據交互。

3.3 協議數據轉換部分

系統協議數據轉換部分中采用現場可編程邏輯門陣列器件EP1C6U240C8進行編程,主要實現的功能是將與USB3300交互的數據轉換成10位并行數據與SN65LV1023和 SN65LV1224交互,同時通過STP信號控制 USB3300的數據傳輸方向和USB3300的狀態。由于USB協議本身有低功耗模式,在低功耗模式時鎖相環關閉,在硬件設計時一定要接RESET控制鍵,這樣便于軟件編程的調試。

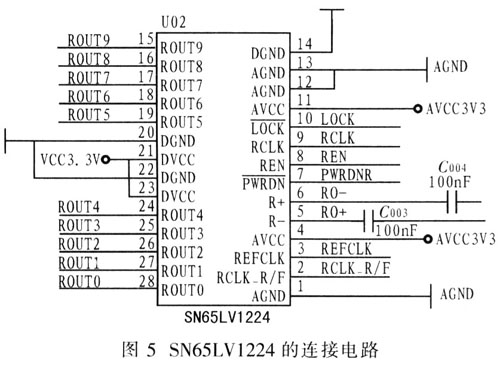

3.4 LVDS接口電路

低壓差分信號LVDS(Low Voltage Differential Signaling)接口是一種高速數據傳輸的物理層接口,其電壓信號擺幅低,技術上能做到且產生極低噪聲,功耗也極低,主要用于服務器、可堆壘集線器、無線基站、3FG交換機及高分辨率顯示等。與USB協議接口類似其物理層信號直接與FPGA進行交互相當復雜,系統選用SN65LV1224和 SNLV1023,將FPGA與LVDS接口物理層數據交互,轉換為10位的并行信號,同時通過相關的控制信號控制數據的傳輸方向。SN65LV1023 與SN65LV1224的硬件連接電路分別如圖4和圖5所示,其中SN65LV1023實現10位并行數據轉換成LVDS的低壓差分信號,同時FPGA通過TCLK_R/F控制內部鎖相環,進而控制SN65LV1023狀態。而SN65LV1224則將LVDS的低壓差分信號轉換成10位并行數據信號輸入 FPGA,這樣通過SN65LV1023與SN65LV1224,便在較為簡單的情況下實現FPGA與LVDS接口的數據交互。

4 系統軟件設計

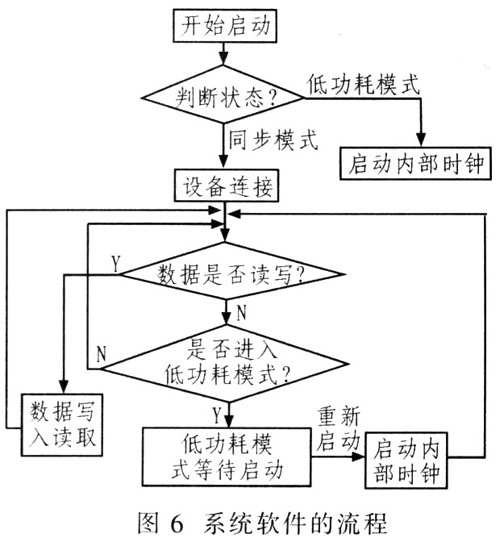

利用可編程邏輯門陣列FPGA轉換協議數據,由于系統使用USB3300可將USB協議物理層信號轉換成8位并行信號,而使用SN65LV 1023與SN65LV1224則將低壓差分信號LVDS轉換成10位并行信號,這樣大大簡化FPGA的編程。

FPGA編程只需通過控制引腳,控制兩個并行信號的輸入輸出即可,同時可將數據的讀寫操作模塊化,從而進一步簡化系統編程。系統軟件設計流程如同6 所示。由于遵循USB協議,在一段時間不進行任何操作時則進入低功耗模式。而USB3300也擁有這一特性。在一定時間系統不進行任何的讀寫操作,USB3300將進入低功耗模式,此時USB3300會自動關閉鎖相環時鐘輸出。

所以在系統啟動后,首先判斷USB3300的狀態,如果在低功耗模式下,則控制STP信號開啟內部時鐘,進入到同步模式。設備連接成功后,隨時判斷是否應該進行讀寫操作,若需要,則進入讀寫操作模塊,實現讀寫操作后又開始判斷讀寫。等待一段時間不執行讀寫操作后,USB3300則進入低功耗模式,關閉鎖相環,等待下次讀寫操作時再重新啟動內部時鐘。

5 結論

采用專用轉換器USB3300,SN65LV1023,SN65LV1224分別將USB協議物理層的差分信號和LVDS的低壓差分信號轉換成并行信號,并通過FPGA編程實現協議編程的轉換。該系統設計較為簡單,并且系統拓展較簡單,可易于實現USB接口、 LVDS接口對多種接口的轉換。

由于串口通信協議的物理層信號較為復雜,FPGA直接與其物理層信號進行數據交互比較難以實現,難以做到時序同步,而采用專用的轉換器將串行信號轉換成并行數據信號,則大大簡化邏輯門陣列編程。該系統合理使用USB3300和SN65LV1023與 SN65LV1224接口器件使得邏輯門陣列的編程易于實現,也可使用其他的專用轉換器,實現不同接口的轉換。