文獻標識碼: A

文章編號: 0258-7998(2015)03-0055-03

0 引言

隨著CMOS技術和高水平硅集成電路的發展,片上數據傳輸率相比于十年前已經有了很大的提高。高的片上數據傳輸率直接大幅度提高了高端微處理器、智能路由器、光纖傳輸等產品處理和傳輸數據的能力。這也使電路對芯片外數據傳輸率的要求越來越高。但是CMOS和硅集成電路技術的發展對提高芯片外信號的傳輸速度影響甚微。普通的I/O接口電路要想提高數據傳輸速率就要消耗更高的功率,并以提高IC封裝和PCB板電路的復雜度和成本為代價[1]。在這種情況下普通的I/O接口已經遠遠不能滿足不斷提高的高速傳輸數據的需要。同時隨著便攜式無線通信的發展,在高速傳輸數據的同時,對電路的功耗也提出了更高的要求。

1 LVDS技術

1.1 LVDS技術簡介

LVDS接口技術正是在這樣的背景下產生,并被廣泛地接受。它是一種低振幅差分信號技術,這種技術使用的信號幅度非常低,通過一對差分PCB走線或平衡電纜進行數據的傳輸,具有低功耗、低輻射、高抗噪聲等特點。

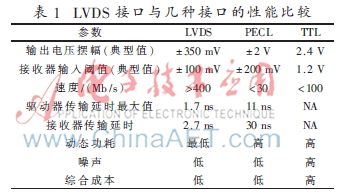

表1提供了LVDS接口和其他兩種接口的比較。從表中可以看出,同為差分接口,LVDS與PECL相比,在傳輸速率、功耗、接收靈敏度方面都具有較大的優勢。與TTL/CMOS相比,在高速、低抖動及其對共模特性較高的系統應用場合具有較大的優勢。基于以上的優點,LVDS技術成為當今高速I/O接口中的首選技術[2]。

1.2 典型的LVDS接口電路及其局限性

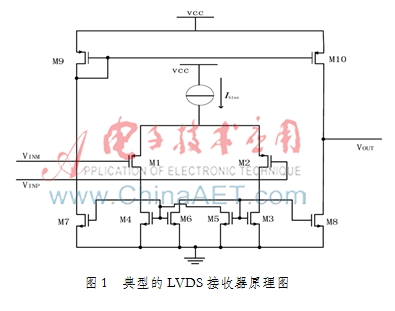

經典的LVDS接收器電路如圖1所示。輸入端輸入的LVDS差分信號通過M1到M6組成的第一級放大器進行放大。第一級放大器的輸出驅動反相器連接的M8和M10管,提高了輸出信號的擺幅。這款經典的LVDS接收電路在輸入信號的共模電壓保持一個合適的范圍時,基本能滿足高速LVDS接口電路的要求,但是如果電路要滿足LVDS接口標準,輸入的共模電壓在0.05 V~2.4 V之間發生變化時,就會存在若干問題[3-4]。

首先,如果沒有采用低閾值的器件,當輸入的共模電壓達到最小值0.05 V時,M1和M2會進入到線性區,這將會導致放大器增益的下降,使第一級的放大器不足以去驅動第二級的輸出反相器,而使輸出信號的幅度大大減小。其次在放大器共模輸入電壓的變化引起增益的變化的同時,也會導致放大器延時發生較大變化,在高速傳輸數據的情況下,這將導致高的誤碼率。用軌到軌輸入的全差分放大器可以解決這個問題,但是這將會導致電路功耗大大提高。

2 LVDS接收器的設計

接收器支持輸入共模電壓的范圍為0.05 V~2.4 V,最小的差模輸入電壓的幅度為100 mV,最高傳輸數據率在600 M/s以上。這款接收器相比于文獻[3]、[4]設計的接收器具有更低的功耗。此外這個接收器通過使用3.3 V器件和1.2 V器件,把信號轉換到1.2 V水平,以提供給后續核心邏輯模塊應用。

2.1 LVDS接收器原理圖設計

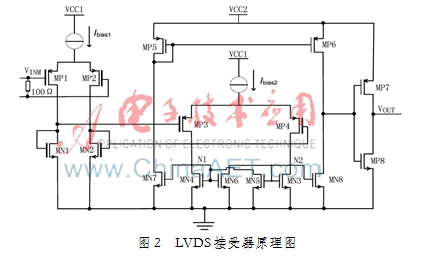

根據LVDS I/O接口標準的規定,LVDS接收器要滿足輸入差分信號的共模電壓范圍為0.05 V~2.4 V,輸入信號的差模電壓范圍為100 mV~400 mV[5-7]。LVDS接口標準要求所設計的LVDS接收器要在很寬的共模輸入電壓范圍下工作。然而一般的差分放大器共模輸入電壓在這么寬的范圍內發生變化時,放大器的增益也會發生很大變化,同時放大器增益的變化也會引起放大器的延時隨之發生變化。在高速數據傳送的情況下,放大器延時較大的變化,會使接收端接收的數據出錯,從而影響到數據的傳輸。為滿足LVDS接口標準的要求,設計的LVDS接收器采用了兩大部分,第一部分為一個差分放大器,對輸入信號進行預放大;第二部分為比較放大器。第一部分的差分放大器主要考慮共模輸入電壓在大范圍發生變化時,放大器的增益盡量保持一個常數,并提高放大器的增益帶寬積;第二部分的比較放大器主要考慮提高放大器的增益和輸出信號的擺幅,使輸出信號的幅度滿足后續電路的要求,并把信號轉換到采用1.2 V電源供電的電路所需要的水平,以供后續電路使用。LVDS接收器原理圖如圖2所示。

2.2 LVDS接收器原理圖分析

在第一級差分放大器中,由于輸入端共模輸入電壓范圍為0.05 V~2.4 V,因此第一級差分放大器采用了3.3 V(VCC1)電源供電,使用了SMIC 0.13 μm工藝提供的厚柵氧化(3.3 V)器件,在電路中用粗的柵符號表示,電路中其余的器件為薄柵氧化(1.2 V)器件。本設計中的第一級放大器選用了OTA結構,為了滿足LVDS接口標準對輸入共模電壓范圍的規定,采用了兩個PMOS管(PMOS1和PMOS2)為差分輸入管,兩個NMOS(NMOS1和NMOS2)管連接成二極管的形式做負載。此差分放大器的增益只與輸入管和負載管的寬長比有關,而與共模輸入電壓范圍幾乎無關,具有很高的線性度和增益帶寬積,此外輸出的差分信號共模分量也與輸入共模電壓幾乎無關,為下一級放大器提供一個較為穩定的共模輸入電壓。

LVDS接收器的第一級放大器雖然有很高的線性度和增益帶寬積,但是卻以犧牲增益和輸出信號的擺幅為代價,所提供的信號增益和擺幅十分有限。為了提高放大器的增益,第二級比較器的第一級在OTA結構的基礎上,加入了Hysterics結構(NMOS3到NMOS6,如圖2所示。輸入管PMOS3和PMOS4采用厚柵氧化器件,負載管NMOS3到NMOS6采用薄柵氧化器件,由于0.13 μm工藝中要求薄柵NMOS器件的漏極電壓不高于1.4 V,因此在設計時應該選擇合適的工作點,保證電路工作時N1點和N2點的電壓在任何情況下都低于1.4 V。比較放大器的第一級由于采用了OTA結構,因此輸出的擺幅受到限制,為了提高輸出信號的擺幅,加入了由NMOS7、NMOS8、PMOS5、PMOS6薄柵氧化器件構成的第二級放大器,并由1.2 V電源電壓(VCC2)供電,提高輸出擺幅的同時也使輸出信號滿足該工藝常用的1.2 V電源供電電路的需要。在比較放大器之后接入由一級反相器構成的緩沖器,為后續電路提供所需要的矩形波信號。

3 后仿真結果

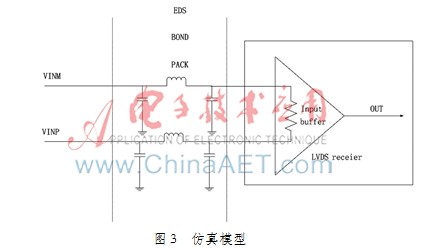

設計采用SMIC 0.13 μm CMOS工藝,并用Cadence提供的spectra進行仿真。為了減小ESD保護電路和封裝電路對接收電路的影響,在仿真時加入了焊盤、ESD保護電路和封裝電路的模型。ESD電路的寄生電容選為2 pF,封裝電路的寄生參數為2 nH和5 pF[3],等效電路如圖3所示。

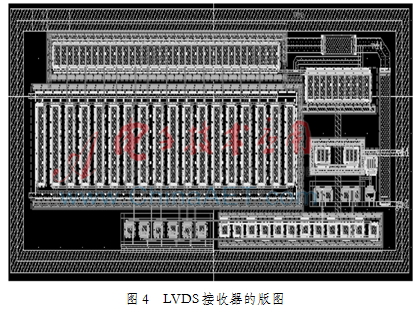

本次設計的版圖如圖4所示。版圖不包括焊盤的面積為90 μm×30 μm。

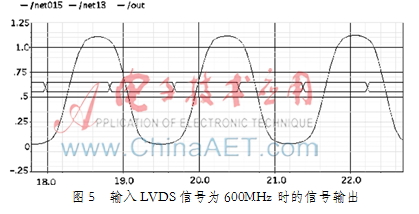

圖5給出了該電路在數據傳輸速度為600 Mb/s時的輸出信號瞬態后仿真結果。圖中輸入的LVDS差分信號幅度為100 mV,頻率為600 MHz。

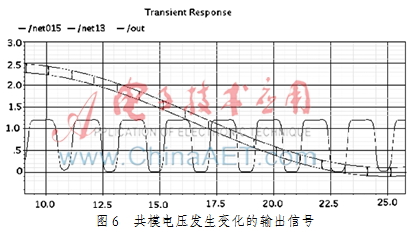

圖6為該電路在輸入共模電壓發生變化時輸出信號的瞬態后仿真結果。其中輸入的共模信號為30 MHz的正弦波,變化范圍為0 V~2.4 V,輸入的差模信號頻率為500 MHz,Vp-p幅度為200 mV。從仿真結果可以看出,當輸入的共模電壓從0 V~2.4 V發生變化時,芯片仍能正常工作。

4 結論

本文采用LVDS信號(低電壓差分信號)進行數據傳輸,設計低功耗高速LVDS接收器,相比于常用的ECL技術,在提供傳輸速度的同時,能夠較大地降低功耗。設計在不同的工藝角下進行仿真,數據傳輸率都能達到600 Mb/s以上,共模電壓輸入范圍為0.05 V~2.4 V,差模輸入電壓范圍為100 mV~400 mV,符合LVDS接口標準的規定,同時芯片的功耗僅為1.26 mW。

參考文獻

[1] Chen Mingdeng.Low-voltage,low-power circuits for data communication systems[D].Texas A&M University,2003.

[2] 譚煒峰.高速LVDS發送器設計[D].成都:電子科技大學,2009.

[3] BONI A,PIERAZZI A,VECCHI D.LVDS I/O interface for Gb/s-per-pin operation in 0.35-μm CMOS[J].Solid-State Circuits.2001.

[4] Zhao Fei,Xu Yong,Li Miaoying,et al.A LVDS transceiver chip design in 0.5μm CMOS Technology[C].Congress on Image and Signal Processing,CISP,2008.

[5] MANDAL G,MANDAL P.Low-power LVDS receiver for

1.3Gbps physical(PHY) interface[C].IEEE International Symposium on Circuits and Systems(ISCAS),2005.

[6] TIA/EIA-644-A,TIA/EIA,standard,Electrical characteris-tics of low-voltage differential-signaling(LVDS) interface circuits[S].2001.

[7] 1596.3 SCI-LVDS Standard.IEEE Std.1596.3-1996.IEEEstandard for low-voltage differential signals(LVDS) for scalable coherent interface(SCI)[S].1996.