文獻標識碼: A

文章編號: 0258-7998(2015)02-0042-03

0 引言

隨著圖像傳感器的快速發展,成像質量和圖像幀率得到快速提升,高分辨率的圖像給人們的生活帶來了極大的便利。但與此同時,快速、實時的傳輸圖像數據成了難題。傳統的顯微鏡系統主要使用人工操作,對操作人員的經驗和知識量要求比較高,并且存在很多不定因素。采用自動對焦則大大解決了以上問題,目前國內外顯微鏡自動對焦在算法上都比較成熟,但圖像的分辨率并不是很高[1]。而提高圖像分辨率不僅提高了自動對焦的精準度,并且可以采集到樣品更多的細節,給研究者提供更多的信息。鑒于以往顯微鏡圖像采集系統的不足,針對高分辨率圖像的數據采集,本文選擇了基于PCI Express(PCIe)總線的圖像采集系統實現顯微鏡圖像的采集。

目前計算機使用最為廣泛的PCI總線接口最高工作頻率能達到66 MHz,峰值帶寬理論上可以達到532 MB/s,但這種并行總線的傳輸速度和帶寬已逐漸滿足不了高速傳輸的要求。相比傳統的PCI總線,21世紀初提出的高速差分總線PCIe采用點對點串行連接、全雙工的傳輸方式大大提升了傳輸速度和帶寬。本文實現的1.0版本x4規格通道理論帶寬可達到2 GB/s,比USB3.0快,更是千兆以太網傳輸速度的8倍。

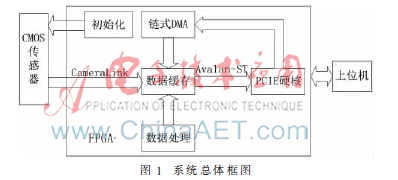

1 系統總體設計

設計的整體結構如圖1所示,系統給PCIe采集系統提供5 V電源,FPGA正常工作后開始執行芯片的固化程序。首先通過IIC對CMOS傳感器進行初始化,CMOS傳感器開始拍攝細胞的圖像,同時通過Cameralink接口將圖像數據送至系統數據緩存。FPGA將接收到的4對差分數據解析得到圖像數據,接著以鏈式DMA傳輸方式將數據直接送至IP硬核,然后將數據打包送至上位機,上位機通過應用軟件將圖像顯示并保存。

2 系統硬件設計

2.1 CMOS成像模塊

本系統的圖像傳感器采用Aptina公司生成的MT9-F002I12STCU芯片。FPGA通過IIC協議對CMOS芯片進行初始化,配置相關寄存器。初始化之后,圖像尺寸為4 096H×3 072V,每幀圖像大小為12 MB,每秒可生成15幀圖像。該模塊固定在顯微鏡上,單獨為其提供5 V電源,模塊內部可轉換2.8 V和1.8 V電壓為傳感器供電。CMOS傳感器的初始化程序以及圖像數據都是通過Cameralink傳輸。

2.2 PCIe總線接口

PCIe總線采用串行連接的方式,并使用數據包進行數據傳輸。數據報文首先在設備的核心層中產生,然后再經過設備的事務層、數據鏈路層和物理層,最終發送出去,接收端的數據也需要通過物理層、物理鏈路層和事務層,并最終到達核心層。目前主流的PCIe總線接口方法有兩種,方法1:用PEX8311芯片,該方法實現了物理層、數據鏈路層和事務層的控制邏輯,簡單易實現,但是缺乏靈活性和可配置性[2]。方法2:利用FPGA芯片內部集成IP硬核,IP硬核完成了物理層和數據鏈路層的協議,用戶需自行設計PCIe的應用層協議和TLP,開發難度較大,但可以根據需求合理配置[3]。本系統采用方法2,選用Altera公司的EP4CGX30CF23C8芯片,該芯片內部集成了IP硬核模塊,可以實現x4通道的PCIe接口。

3 系統軟件設計

3.1 鏈式DMA傳輸設計

圖像數據傳輸采用DMA技術保證其實時性[4],利用鏈式DMA技術提高DMA執行效率并配合SGDMA技術解決計算機離散物理頁的DMA傳輸問題[5]。鏈式DMA區別于普通DMA的最大特點就是可以一次執行多次DMA,因此執行效率非常高,非常適合于上位機上物理分頁地址不連續的DMA數據傳輸。本系統中僅用到DMA寫模塊,數據由FPGA流向計算機。具體實現的方法是:在主機端開辟一塊內存區域,用來存儲描述符表。描述符表是用來描述在主機與外設之間數據傳輸有關的地址與長度信息的,它由一個表頭和多個描述符組成。數據傳輸前,用戶將控制參數、端點地址、內存物理地址寫入并啟功傳輸。鏈式DMA控制器會及時從內存中讀取描述符表來指揮DMA的傳輸過程。

3.2 驅動程序設計

驅動程序采用Jungo公司開發的Windriver軟件,并利用其特有的KernelPlugln(KP)技術實現高效的中斷數據采集服務。主要依靠3個函數:KP_IntAtIrqt、KP_IntAtDpc、KP_Call。

KP_IntAtIrqt:高優先級中斷服務程序,硬件中斷產生時,該函數被調用。當返回值大于零時繼續調用KP_IntAtDpc。本項目中,數據采集的全部工作都在該函數里面完成。當一幅圖像采集完成后返回1以便繼續調用IntAtDpc低優先級中斷。

KP_IntAtDpc:低優先級中斷服務程序,KP_IntAtIrqt返回值大于零時被調用,本項目中不做任何處理,返回值永遠大于零以調用用戶模式下的中斷服務程序。

KP_Call:主要用于用戶模式與KP通信,本項目中用來傳遞數據緩沖區以及描述符表的地址,需要注意的是用戶應用程序與KP驅動程序擁有不同的虛擬地址系統,因此應用程序的地址在驅動程序里不能直接使用,需要經過地址轉換才能使用。

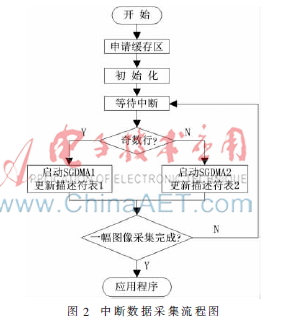

圖2是中斷數據采集的流程圖。為提高數據采集效率,采用兩片緩沖區交替緩沖機制,應用程序首先申請兩片數據緩沖區,并且對其初始化。然后通過KP_Call函數將緩沖區的地址及其頁表信息等傳入驅動程序內核模式下的KernelPlugln,用于鏈式DMA描述符表的更新。圖像采集卡每采集到3行圖像數據發送一次中斷,中斷服務程序立刻響應中斷。首先讀取BAR2空間偏移地址0x40處的32 bit狀態寄存器,根據其值判斷當前數據位于圖像的奇數行或偶數行。中斷程序維護兩個鏈式DMA描述符表,然后根據狀態寄存器的值判斷啟動對應的鏈式DMA以及更新下次將要使用的鏈式DMA描述符表,圖像采集卡將根據描述符表將數據寫入相應數據緩沖區的對應地址。最后,再次根據狀態寄存器的值判斷一幅圖像是否采集完成,若完成則通知應用程序并繼續等待下一次中斷,否則直接等待下一次中斷。

4 實驗結果分析

采集圖像之前先通過Altera公司設計的PCIe測速軟件在1小時內對采集系統進行了6次測試,測試得到的結果如表1所示。

由表1的測試結果可以看出,DMA寫的速度已經達到理論帶寬的80%以上,DMA讀的速度大約為580 MB/s。經過分析,測試速度較理論速度偏低大致有以下3個原因:(1)DMA讀取為非轉發事務,所以讀的速度比寫的要慢;(2)中斷響應和配置DMA寄存器延時造成速度降低;(3)計算機本身硬件條件導致傳輸速度偏低。相比于成像模塊每秒產生15幀12 MB的圖像,采集系統能夠很好地完成實時采集成像模塊生成的圖像。

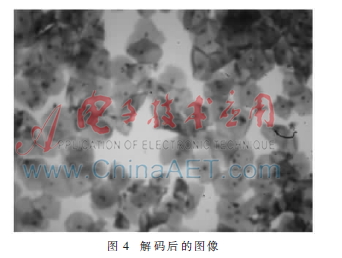

將采集系統應用于顯微鏡自動對焦圖像采集,經過長時間的采集測試,未出現丟幀現象,采集系統正常工作。圖3是采集的未經解碼的原始圖像數據。圖4是通過快速插值解碼之后的彩色的圖像。兩幅圖中的黑點是鏡頭未清潔干凈導致。實驗結果表明,本系統能夠很好地采集顯微鏡自動對焦成像模塊生成的高分辨率圖像,性能穩定,適用于大數據量的實時快速采集。

5 結束語

本文詳細介紹了基于PCI Express的圖像采集系統,為大數據量的實時快速傳輸提供了有效的方案。并通過測試證明了該系統能很好地應用于顯微鏡自動對焦成像模塊的圖像采集,實現了高分辨率圖像的實時顯示。相對于熱門的USB3.0以及千兆以太網,本設計在傳輸速度上有明顯的優勢,并且當傳輸速度有更高的要求時,還可以將x4通道擴展成x8或x16通道,得到更高的傳輸速度。

參考文獻

[1] 張磊.顯微鏡用數碼相機硬件結構及其視頻流算法實現與應用[D].杭州:浙江大學,2011.

[2] 安駿.基于橋接芯片PEX8111的PCIE總線接口設計[J].科技資訊,2010(3):23-24.

[3] 沈輝,張萍.FPGA在PCI Express總線接口中的應用[J].計算機應用技術,2010,33(14):109-111.

[4] 李木國,黃影,劉于之.基于PCIe總線的高速數據采集卡設計與實現[J].測控技術,2013,32(7):19-22.

[5] 黃世中,金志剛.利用WinDriver實現鏈式DMA[J].電子設計工程,2013,21(8):6-9.