摘 要: 研究了一種基于Vivado HLS加速OpenCV程序的方法,其核心是利用Xilinx高層次綜合工具Vivado HLS,將C++編寫(xiě)的OpenCV程序按照Vivado HLS處理規(guī)范進(jìn)行修改,進(jìn)而將代碼轉(zhuǎn)換為硬件描述語(yǔ)言,可快速生成IP核。結(jié)合Xilinx Zynq SoC架構(gòu)和其視頻圖像處理方面的優(yōu)勢(shì),通過(guò)軟硬件協(xié)同的方法,實(shí)現(xiàn)OpenCV程序算法向高性能處理平臺(tái)Zynq SoC系統(tǒng)的移植和加速。該方法對(duì)圖像處理軟件設(shè)計(jì)的硬件化加速具有重要的應(yīng)用價(jià)值。

關(guān)鍵詞: 開(kāi)源計(jì)算機(jī)視覺(jué);圖像處理;高層次綜合;加速

0 引言

開(kāi)源計(jì)算機(jī)視覺(jué)庫(kù)OpenCV是目前最受歡迎的開(kāi)源計(jì)算機(jī)視覺(jué)軟件函數(shù)包[1],為計(jì)算機(jī)視覺(jué)的研究和圖像處理應(yīng)用提供了很大的便利。然而,OpenCV程序算法都是在PC上通過(guò)軟件運(yùn)行的方式實(shí)現(xiàn),存在處理實(shí)時(shí)性差、適用范圍有限等問(wèn)題,尤其是在高清圖像處理方面經(jīng)常受到外部存儲(chǔ)器性能的限制,存儲(chǔ)帶寬經(jīng)常成為其程序優(yōu)化的瓶頸,并且存儲(chǔ)訪問(wèn)也限制了功耗效率[2]。

基于FPGA可用全硬件實(shí)現(xiàn)圖像處理算法,在嵌入式系統(tǒng)應(yīng)用中得天獨(dú)厚,所以很值得嘗試?yán)每删幊踢壿嬘布?lái)加速OpenCV。Vivado HLS是Xilinx最新開(kāi)發(fā)的一種高級(jí)綜合工具,可以直接將C/C++編寫(xiě)的算法程序進(jìn)行仿真綜合成RTL,從而可以在FPGA上實(shí)現(xiàn)圖像處理算法。Vivado HLS具有專門(mén)的圖像處理庫(kù),與OpenCV函數(shù)對(duì)應(yīng)。

本文主要研究高層次綜合工具Vivado HLS及Xilinx Zynq SOC全可編程處理平臺(tái)、Vivado圖像視頻函數(shù)庫(kù),并通過(guò)高級(jí)綜合工具Vivado HLS將OpenCV轉(zhuǎn)化為RTL處理流程,在Xilinx Zynq SoC系列全可編程處理平臺(tái)上實(shí)現(xiàn)OpenCV程序算法的硬件加速。以邊緣檢測(cè)為例說(shuō)明加速流程。

1 Zynq SOC與HLS

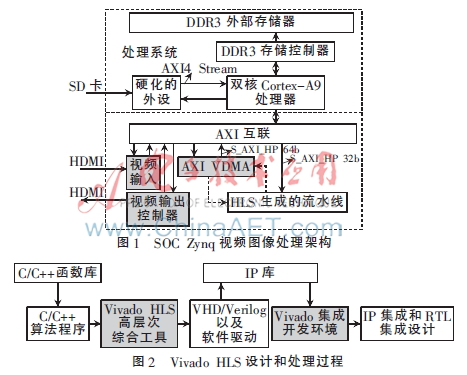

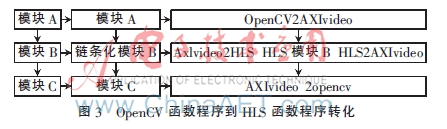

Xilinx Zynq SOC是具有ARM+FPGA架構(gòu)的全可編程處理器,集成了雙核Cortex-A9處理系統(tǒng)、FPGA邏輯和一些關(guān)鍵外設(shè),提供了軟硬件和I/O可編程性。Zynq SOC具有64位高性能端口,可以實(shí)現(xiàn)對(duì)外部存儲(chǔ)器的訪問(wèn);還有32位通用端口實(shí)現(xiàn)控制寄存器的訪問(wèn),并且使用AXI4-Stream能更好地解決高清視頻流速度問(wèn)題。處理子系統(tǒng)、FPGA邏輯和外設(shè)在Zynq SOC中的高度集成性確保了相對(duì)于采用分離式組建設(shè)計(jì)的系統(tǒng)而言提高數(shù)據(jù)傳輸速率,高度的軟硬件集成性能幫助設(shè)計(jì)人員實(shí)現(xiàn)極為高效的嵌入式視覺(jué)系統(tǒng),降低功耗和材料清單成本。Zynq SoC視頻圖像處理架構(gòu)如圖1所示[3]。為了全面利用Zynq SOC的諸多性能,Xilinx推出了以IP設(shè)計(jì)為中心的設(shè)計(jì)環(huán)境Vivado設(shè)計(jì)套件,該套件可加速集成和設(shè)計(jì)實(shí)現(xiàn)。而Vivado HLS作為該套件的一個(gè)重要組件,能幫助設(shè)計(jì)人員將采用C/C++語(yǔ)言的開(kāi)發(fā)的算法編譯為RTL,以便在FPGA邏輯中運(yùn)行。在圖像處理復(fù)雜算法中,通過(guò)C/C++創(chuàng)建算法原型,再利用Vivado HLS將算法或者算法的一部分編譯為RTL,進(jìn)而確定哪些函數(shù)更適合在FPGA邏輯中運(yùn)行,哪些函數(shù)適合在ARM上運(yùn)行,這樣更能集中精力設(shè)計(jì)出最佳性能的基于Zynq SOC的視覺(jué)系統(tǒng)。利用高級(jí)綜合工具Vivado HLS開(kāi)發(fā)的流程如圖2所示。

2 OpenCV算法程序到Vivado HLS程序的修改

對(duì)OpenCV程序的硬件加速,實(shí)際上是將OpenCV轉(zhuǎn)化為可綜合的代碼,用可綜合的Vivado HLS視頻庫(kù)函數(shù)代替OpenCV函數(shù)。VIvado HLS具有專門(mén)支持OpenCV的視頻函數(shù)庫(kù),這些函數(shù)可以代替OpenCV函數(shù),并且能很好地綜合為RTl代碼,進(jìn)而可以利用Zynq全可編程SoC的優(yōu)勢(shì)實(shí)現(xiàn)圖像或者視頻的處理。

2.1 OpenCV與Vivado HLS視頻函數(shù)庫(kù)

Vivado HLS高級(jí)語(yǔ)言綜合工具包含了專門(mén)的OpenCV視頻庫(kù),通過(guò)HLS庫(kù)中的函數(shù)代替原本OpenCV算法程序中的函數(shù)便可以完成由OpenCV到HLS的轉(zhuǎn)化,在Zynq上硬件化后,提高OpenCV應(yīng)用效率[4]。

OpenCV經(jīng)常用到的數(shù)據(jù)類型有Mat、CvMat和IplImage[5],VivadoHLS視頻處理函數(shù)庫(kù)使用hls::Mat<>數(shù)據(jù)類型,這種類型用于模型化視頻像素流處理,等同于hls::steam<>流的類型,而不是OpenCV中在外部memory中存儲(chǔ)的matrix矩陣類型。因此,在用Vivado HLS實(shí)現(xiàn)OpenCV的設(shè)計(jì)中,需要將輸入和輸出HLS可綜合的視頻設(shè)計(jì)接口修改為Video stream接口,也就是采用HLS提供的Video接口可綜合函數(shù),實(shí)現(xiàn)AXI4 Video stream到Vivado HLS中hls::Mat<>類型的轉(zhuǎn)換[6]。

從軟件到RTL過(guò)程中,最關(guān)鍵的是接口問(wèn)題,而HLS創(chuàng)建的硬件專注于硬件接口,Vivado HLS支持以相對(duì)較小的可以輕松創(chuàng)建AXI的從接口,從而使硬件加速器設(shè)計(jì)變得簡(jiǎn)單。在視頻處理中,Xilinx通過(guò)AXI4流協(xié)議來(lái)實(shí)現(xiàn)像素通信,以更小的元素來(lái)傳輸視頻幀,可以不用知道視頻流的大小或者圖片的尺寸,大大簡(jiǎn)化了視頻處理計(jì)算。

2.2 OpenCV程序修改方法

使用HLS加速OpenCV時(shí),需要先用I/O函數(shù)提取FPGA實(shí)現(xiàn)部分,用可綜合的Vivado HLS函數(shù)庫(kù)函數(shù)代替OpenCV函數(shù)。在Zynq開(kāi)發(fā)中使用Vivado HLS實(shí)現(xiàn)OpenCV的設(shè)計(jì)流程如下[7]:

首先,開(kāi)發(fā)OpenCV的應(yīng)用,編寫(xiě)源碼和測(cè)試文件,并且采用C++編譯器進(jìn)行編譯、仿真和調(diào)試,產(chǎn)生可執(zhí)行文件。

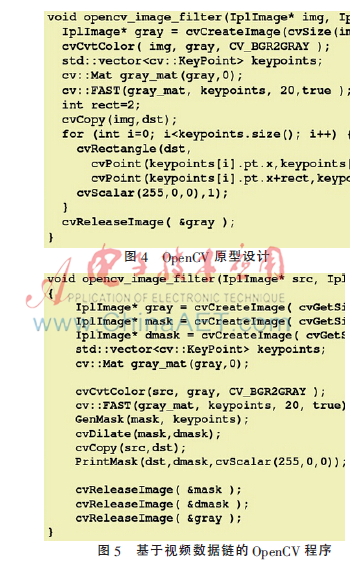

其次,使用I/O函數(shù)抽取FPGA實(shí)現(xiàn)部分,并且使用可綜合的Vivado HLS庫(kù)函數(shù)代碼代替OpenCV函數(shù)的調(diào)用。其流程如圖3所示。

最后,運(yùn)用HLS生成的RTL代碼,在Vivado HLS工程中啟動(dòng)co-sim,HLS工具自動(dòng)重用OpenCV的測(cè)試激勵(lì)驗(yàn)證產(chǎn)生的RTL代碼。在Xilinx的Vivado集成開(kāi)發(fā)環(huán)境中做RTL集成和SOC/FPGA實(shí)現(xiàn)。

3 硬件加速OpenCV程序應(yīng)用

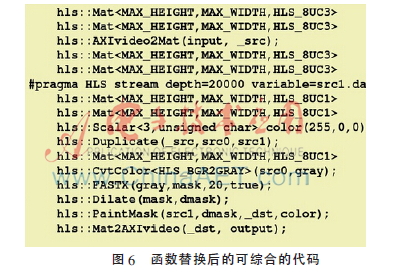

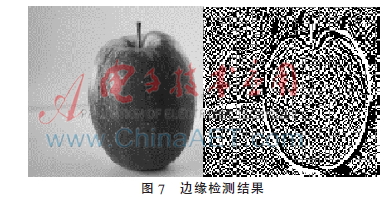

本文通過(guò)邊緣檢測(cè)算法來(lái)介紹硬件加速OpenCV應(yīng)用。根據(jù)前面介紹的方法,利用OpenCV庫(kù)函數(shù)先設(shè)計(jì)出邊緣檢測(cè)算法原型,如圖4所示,并使用基于OpenCV的測(cè)試激勵(lì)驗(yàn)證這個(gè)算法。再改寫(xiě)前面設(shè)計(jì)好的OpenCV算法程序,按照視頻數(shù)據(jù)鏈的形式重新改寫(xiě),如圖5所示,這樣與HLS視頻庫(kù)處理機(jī)制相同,方便函數(shù)替換。最后將改寫(xiě)好的OpenCV程序中的函數(shù)替換為HLS提供的相應(yīng)功能的函數(shù),如圖6所示,并且使用Vivado HLS工具綜合,綜合之后生成IP,在Vivado集成開(kāi)發(fā)環(huán)境中以IP為核心完成設(shè)計(jì),在SDK中利用原OpenCV測(cè)試激勵(lì)進(jìn)行測(cè)試,基于邊緣設(shè)計(jì)應(yīng)用測(cè)試結(jié)果如圖7所示。

4 結(jié)論

使用高層次綜合工具Vivado HLS結(jié)合邏輯可編程FPGA或者Zynq SOC實(shí)現(xiàn)OpenCV在高分辨幀率的實(shí)時(shí)視頻處理是解決目前OpenCV軟件程序速度優(yōu)化瓶頸問(wèn)題的有效方法。采用Vivado HLS視頻庫(kù)能加快OpenCV函數(shù)向可綜合邏輯器件Zynq SOC或FPGA的映射。同樣,也可以利用Zynq SOC結(jié)合Vivado HLS工具的方法,來(lái)硬件加速其他計(jì)算機(jī)軟件設(shè)計(jì)。該方法對(duì)加速優(yōu)化高速算法軟件設(shè)計(jì)具有一定的參考價(jià)值。

參考文獻(xiàn)

[1] 張秀榮,孟和達(dá)來(lái).數(shù)字圖像處理系統(tǒng)開(kāi)發(fā)與研究[J].湖南師范大學(xué)學(xué)報(bào)(自然科學(xué)版),2011,34(6):35-39.

[2] BRADSKI G, KACHLER A. Learning OpenCV(1st Edition)[M]. O′Reily Media, Inc., 2008.

[3] Xilinx Inc.Accelerating OpenCV applications with zynq-7000all programmable SoC using Vivado HLS video libraries[Z]. http://www.xilinx.com/support/documentation/application_notes/xapp1167.pdf. 2014.

[4] Xilinx Inc. Vivado design suite tutorial high-level synthesis[Z]. http://www.xilinx.com/support/documentation/sw_manuals/xilinx 2012_4/ug871-vivadohigh-level-synthesis-tutorial. pdf. 2014.

[5] 郭暉,陳光.基于OpenCV的視頻圖像處理應(yīng)用研究[J].微型機(jī)與應(yīng)用,2010,29(21):14-20.

[6] 叢秋波.Vivado設(shè)計(jì)套件將可編程系統(tǒng)集成度和實(shí)施速度提升4倍[J].電子設(shè)計(jì)技術(shù),2012(6):22-24.

[7] 何賓,張艷輝.Xilinx FPGA數(shù)字信號(hào)處理權(quán)威指南[M].北京:清華大學(xué)出版社,2014.