文獻標識碼:A

DOI: 10.19358/j.issn.2096-5133.2018.08.016

中文引用格式:馮傳均,何泱,戴文峰.基于FPGA的猝發多脈沖產生系統設計與實現[J].信息技術與網絡安全,2018,37(8):70-72.

0 引言

脈沖功率技術是一種功率壓縮技術,以較低的輸入功率將能量緩慢存儲起來,隨后在極短時間內釋放,以獲得極高的峰值輸出功率。該技術是應國防科技需要而發展起來的一門新興科學技術,是獲得高電壓、大電流等極端電磁參數的重要手段,被廣泛應用在科學研究和工業生產等諸多領域中[1-3]。

脈沖功率裝置一般由初級能源系統、中間儲能系統、脈沖形成系統、開關轉換系統和負載系統5個子系統組成。工作時,初級能源系統用于為脈沖功率裝置供能,將能量輸送至中間儲能系統中;中間儲能系統常見遠重頻或猝發脈沖功率裝置,通過初步功率壓縮為脈沖形成系統供能;脈沖形成系統充電完成后,通過開關轉換系統將能量快速傳遞給負載系統,實現脈沖功率輸出。

猝發脈沖是指脈沖功率裝置在一次工作周期中輸出的多個相同的高功率脈沖,是為了滿足特定的工業及科研需求而發展起來的一種脈沖功率技術。要實現猝發脈沖方式工作,脈沖功率裝置各個子系統需要按照一定的時序協調工作。為此需要研制一套猝發多脈沖產生系統,控制脈沖功率裝置各個子系統按要求工作,同時要實現可調的猝發脈沖參數。

本文采用FPGA控制芯片作為猝發多脈沖產生系統控制中樞,接收上位機控制命令,實現猝發多脈沖信號產生。該系統可輸出2路猝發多脈沖信號,猝發脈沖串個數1~5個可調,猝發脈沖串間隔1~200 s可調,猝發脈沖串內部脈沖個數1~5個可調,猝發脈沖串內部脈沖頻率1~100 Hz可調,猝發脈沖串內部脈沖寬度等參數可以調節[4-6]。

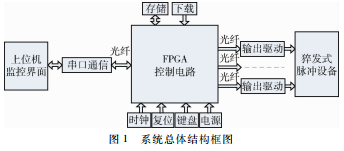

1 系統總體結構

猝發多脈沖產生系統包括:上位機監控界面、串口通信電路、FPGA控制電路、輸入/輸出隔離電路4個部分。系統總體結構框圖如圖1所示。其中上位機監控界面基于Visual Basic(VB)軟件進行可視化編程實現,通過上位機監控界面可以完成串口通信協議設置、猝發多脈沖信號的參數設置以及系統啟動/停止、系統自檢等狀態控制;上位機和FPGA控制芯片采用RS232串口通信協議,串口通信電路包括:FPGA串口(UART)模塊、MAX232芯片和上位機串口三部分,MAX232芯片實現電平轉換,解決FPGA的信號電平與RS232的標準不一致的問題;FPGA芯片采用Altera CycloneIV系列,FPGA控制電路包括時鐘電路、電源電路、程序下載電路、SDRAM和Flash存儲電路、復位電路等;輸入/輸出隔離電路包括:串口接收信號、串口發送信號和脈沖輸出信號,為了增強系統的抗干擾性,FPGA輸入/輸出信號均采用光纖傳輸實現。

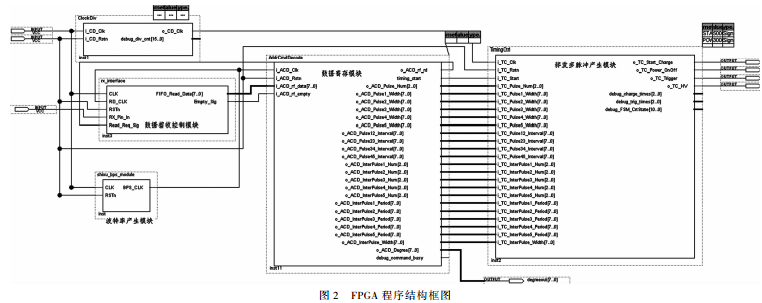

2 FPGA中控系統程序設計

FPGA采用硬件邏輯實現控制功能,具有功耗低、速度快、工作頻率高、集成度高等特點,可以完成極其復雜的時序與組合邏輯。本文中FPGA控制電路主要功能有:通過UART模塊從串口接收上位機發送的數據,并對接收的數據進行緩存、解析和存儲處理,根據控制命令輸出2路猝發多脈沖信號。FPGA控制程序采用Verilog HDL硬件描述語言編寫,在Quartus II 11.0軟件平臺開發,核心內容包括:UART數據接收模塊、數據寄存模塊、猝發多脈沖產生模塊三部分。FPGA程序結構框圖如圖2所示。

2.1 UART數據接收模塊

本文設計的UART數據接收模塊主要包括波特率產生模塊和數據接收控制模塊。功能是從串口接收上位機發送的串行數據。

2.1.1 波特率產生模塊

在電子通信領域,波特率即調制速度,它是對符號傳輸速率的一種度量,1 b/s表示每秒傳輸1個符號。波特率產生模塊的功能是產生與RS-232串口通信波特率同步的時鐘,其基本思路是對系統輸入時鐘進行分頻得到需要的波特率。本設計中FPGA輸入時鐘為50 MHz,波特率選擇9 600 b/s。

2.1.2 數據接收控制模塊

數據接收控制模塊主要實現對串行數據的串并轉換,轉換的串行數據按照既定的數據幀格式進行輸出。UART數據接收協議采用1位起始位、8位數據位、1位停止位、無奇偶校驗位的格式,在9 600 b/s波特率下,UART數據采集步驟如下:

(1)空閑狀態,等待數據起始位0;

(2)根據起始位的標志,判斷UART時序起始;

(3)由低到高位串行接收8位數據;

(4)判斷結束位1,一幀數據接收完畢。

2.2 數據寄存模塊

UART數據接收模塊接收的數據經過緩存、解析后,按地址存入相應的數據寄存器中。寄存器作為數據存儲的數字設備,2路猝發多脈沖信號參數包括猝發脈沖個數、猝發脈沖間隔、猝發脈沖串脈沖個數、猝發脈沖串脈沖頻率、A猝發脈沖串脈寬、B猝發脈沖串脈寬等,共需要21個計數寄存器。

2.3 猝發多脈沖產生模塊

猝發多脈沖產生模塊根據設置的參數輸出猝發脈沖信號,其脈寬以及脈沖個數等參數是通過對數據寄存器保存的數據進行計數來實現的。本文采用有限狀態機方式實現猝發多脈沖產生模塊的控制。

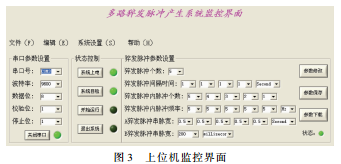

3 上位機監控界面設計

上位機監控界面采用VB軟件編程實現,通過調用MSComm串口通信控件設置通信協議,實現與FPGA建立數據通信。操作者通過監控界面預置2路猝發多脈沖信號參數,輸入完成后點擊參數下載按鈕,再點擊開始運行按鈕后,FPGA開始猝發多脈沖信號的生成。上位機監控界面如圖3所示。

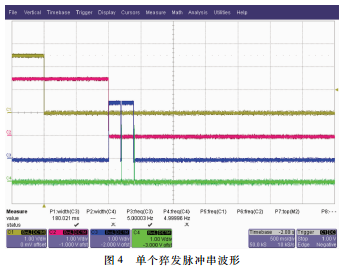

4 實驗調試

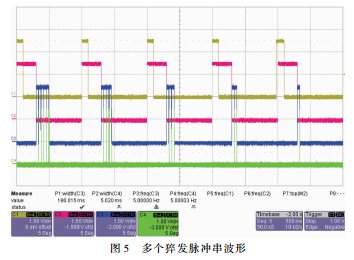

通過上位機監控界面設置串口通信協議,與FPGA控制芯片實現串口數據通信;然后設置猝發多脈沖串的參數,完成后點擊數據保存按鈕,將數據保存到上位機數據文件;點擊數據下載按鈕,將設置的數據通過串口發送到FPGA控制芯片;點擊開始運行后系統開始猝發脈沖的輸出。調試實驗中設置猝發脈沖個數為1個,猝發脈沖串內脈沖個數為2個,猝發脈沖串脈沖頻率為5 Hz,A猝發脈沖串脈寬為180 ms、B猝發脈沖串脈寬為5 ms,單個猝發多脈沖串波形如圖4所示。設置猝發脈沖個數為5個,猝發脈沖串內脈沖個數分別為5、4、3、2、1個,猝發脈沖串脈沖頻率為5 Hz,A猝發脈沖串脈寬為180 ms、B猝發脈沖串脈寬為5 ms。多個猝發多脈沖串波形如圖5所示。

5 結論

本文所研制的基于FPGA的猝發多脈沖產生系統能夠輸出2路猝發多脈沖信號,脈沖參數可以調節。該系統利用FPGA內部控制模塊實現多路脈沖時序輸出和UART接口控制,簡化了硬件電路設計;上位機通過VB軟件編程的人機交互界面,與FPGA之間采用串口通信,實現遠程控制。系統實現遠程控制功能,采用模塊化設計,可擴展性強。這一設計方案也可以運用到其他時序控制電路中。

參考文獻

[1] 劉錫三.高功率脈沖技術[M].北京:國防工業出版社,2005.

[2] 倪晉平,李亞勝,田慧.一種多路時間序列控制儀的設計與實現[J].西安工業大學學報,2012,32(2):88-92.

[3] 羅通頂,郭明安.遠程控制高時間分辨率多通道脈沖發生器設計 [J].計算機測量與控制,2015,23(8):2921-2923.

[4] 陳伯俊,周俊敏,馬軍勇.基于FPGA的高精度多路同步脈沖產生系統研究[J].科學技術與工程,2010,10(19):4794-4796.

[5] 劉紀斌,郭超,羅中省.基于FPGA的多路脈沖同步器設計[J].電子工程師,2008,34(7):3-5.

[6] 王鵬,呂志剛,杜衛東.基于FPGA與ARM的多路時序控制系統設計與實現[J].計算機測量與控制,2012,20(6):1540-1543.

(收稿日期:2018-04-17)

作者簡介:

馮傳均(1989-),男,本科,主要研究方向:脈沖功率技術應用。