為了兼具可擴展性和數據處理速度,對于各種應用,如圖像數據偵錯、視頻數據壓縮、音頻數據增益、馬達控制等,可編程數據處理模塊(Programmable Data Processing Module)是時勢所需。

在處理的數據量越來越大的情況下,所需的內存容量隨之增大,以往的先進先出隊列(First-In-First-Out, FIFO)無法滿足其高速度與大容量的需求,許多硬件工程師開始考慮使用 DRAM 的可能性。

DRAM 具備可快速存取、可依照設計者規劃使用空間、大容量等優點,但是內存數組需要重新充電,而雙倍數據速率同步動態隨機存取內存( DDR SDRAM)有數據相位同步等不易控制的問題,不如 FIFO 使用方便。因此,在使用 FPGA 進行設計時,搭配其供貨商所提供的 RAM 控制 IP,再加上硬件工程師所開發的控制邏輯,是當前數據控制存取的發展趨勢。

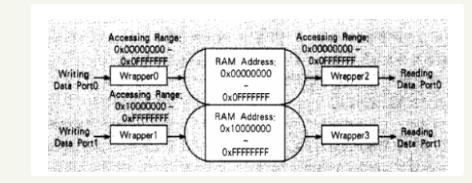

本文的構想是在此 DRAM 控制 IP 上增加一層包裝(Wrapper),使之擁有 FIFO 接口,具有多端口內存存取控制(MPMA: Multi-Port Memory Access)功能。既可以保持大容量、存取速度快等優點,也可增添 FIFO 接口容易的優點。在設計過程中,DRAM 空間可隨設計師的定義而擁有更高的彈性。如圖 1 所示,此 DRAM 擁有兩個寫入端口和兩個讀出端口。對于每個寫入端口,其數據可以從起始地址連續寫入,直到結束地址之后,再從起始地址繼續寫入,形成循環式(Circular)寫入方式。對于每個讀出端口,其數據的讀出可使用類似于循環寫入的方式,而且只要寫入到內存的數據數量比讀出的數據數量多,即是合理的類 FIFO 存取方式。

圖 1 有兩個寫端口和兩個讀端口的 DRAM 控制槽

MPMA 如何應用于數據處理模塊

在許多需要對大量信息進行運算處理的應用中,需要極大的緩存,與一個 4KB FIFO 的價格相比,買一個 32Mb 的 DRAM 更合適些。不過,其復雜的存取控制是一大問題。所以在編寫 FPGA 的 HDL 算法時,可利用 FPGA 供貨商所提供的 IP 構成解決方案。

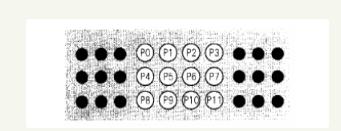

對于所需處理的數據量重復性較高的應用,例如圖 2 所示的圖像原始數據用圖像偵錯處理算法來偵測 P4 點是否錯誤,需要將它周圍的 8 個點當作參考數據來對比,若使用 FIFO,可能無法同時存取到此三條線(Line)的數據,所以使用 DRAM 存取大量的數據。

圖 2 圖像原始數據點數組

由于 DRAM 的控制方式比較復雜,每存取一次就要重新計算其欲存取的數據地址,根據其數據地址的連續性,可在圖像原始數據寫入后,分為三個端口以連續地址的方式讀出。如圖 2 所示,第一端口連續讀出 P0、P1、P2,第二端口連續讀出 P4、P5、P6,第三端口連續讀出 P8、P9、P10,則可以完成 P5 點偵錯的計算;而在計算 P6 點是否出錯時,第一端口只要再讀出 P3,第二端口讀出 P7,第三端口讀出 P11,就可以完成計算前數據的完備,大大提高了數據的使用率,采用連續讀取的機制,不用在每次計算前計算數據地址,只要每一端口均先連續讀取數據即可完成,也降低了 DRAM 控制的復雜度。

MPMA 的實現

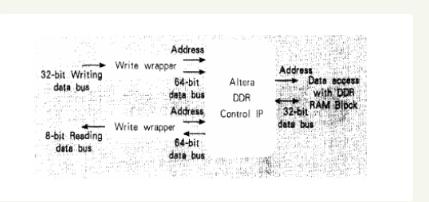

下面以 Altera MegaCore IP Generator 產生的 DDR DRAM 控制器為例,再加上自創的 Wrapper 邏輯,構建一進(32 位進)一出(8 位出)的 MPMA 存取端口,圖 3 為其方塊架構圖。

圖 3 一進一出的 MPMA 存取端口

在此架構中,Altera DDR DRAM 控制與寫 / 讀 wrapper 間的數據帶寬為 64 位,而通過 wrapper 邏輯,更可自由地編寫輸入與輸出帶寬。在寫 / 讀 wrapper 中,數據的地址計算采用累進式累加方式,其存取接口類似于 FIFO 的存取,因而更容易實現大容量數據的存取。

每個 wrapper 中有一個小容量的 FIFO、封裝(packing)/ 反封裝(un-packing)機制以及地址累進計數器。FIFO 用于調節使用者接口與 DRAM 頻域的差異;封裝 / 反封裝機制用于將輸入 / 輸出接口數據總線寬度調整至與 DRAM 控制 IP 接口相同的水平,以利于提高寫入 / 讀出 DRAM 數據的效率。地址累進計數器是每個 wrapper 的 DRAM 地址產生器,只要寫入 wrapper 里的計數器數字大于讀出 wrapper 里的計數器,則所讀出的必為先前已經寫入 DRAM 里的合法數據,不會存取到錯誤地址的數據。

MPMA 提高效率

以圖 2 的點 P5 為例,若不使用 wrapper,則此點數據會被寫入 1 次,而在運算的時候被讀出 1(當作主要運算點)+8(當作參考數據點)次。當一幅有 n 點數據的圖像需要做偵錯處理時,則需要 n*(1+1+8)次的數據存取,還不包括地址計算所造成的延遲。

當使用一進三出的 MPMA wrapper 時,P5 點只需要被寫入 1 次,而在運算的時候被讀出 3(3 個讀 wrapper 各需要讀取 1 次)次,則同樣的 n 點數據作完偵錯處理只需要 n*(1+3)次的數據存取,并且采用累進式的 DRAM 地址計算,不需要花費額外的延遲時間。由此可知,MPMA 設計可提高 2 倍以上的數據存取效率。