由于新冠疫情的原因,2020年的第66屆IEDM轉(zhuǎn)為線上舉辦,但是這并沒有影響IEDM對于半導(dǎo)體制造行業(yè)的重要性,今年的IEDM依然看點(diǎn)眾多。2020 IEDM Press kit今天剛剛披露了會議的重點(diǎn)文章簡介和會議環(huán)節(jié),以下簡單介紹一下本次會議中筆者認(rèn)為較為有趣的幾份技術(shù)更新。

40 kV Silicon Vacuum Transistor

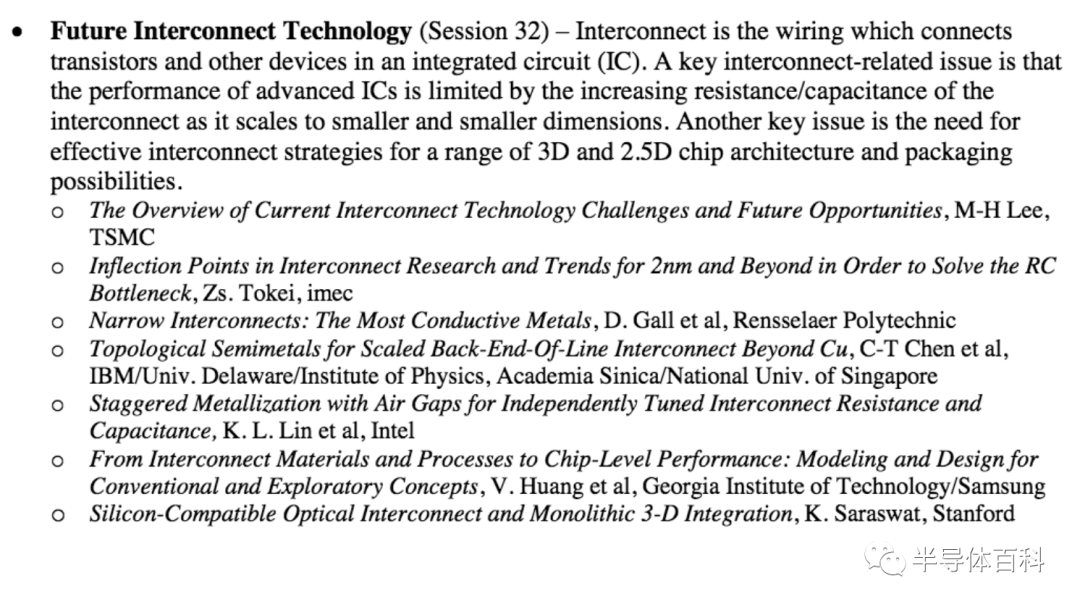

硅基真空電子管示意圖

文章編號5.2,“Demonstration of a ~40 kV Si Vacuum Transistor as a Practical High Frequency and Power Device,” W. Chernet al, MIT/ Harvard/ Massachusetts General Hospital。

由MIT的團(tuán)隊(duì)帶來的第一個工作在約40 kV的Si真空晶體管。這樣的高電壓電平通常采用SiC和GaN等寬帶隙材料。該Si真空晶體管由門控場發(fā)射陣列(FEA,電子源),真空漂移區(qū)和金屬陽極組成。電子通過隧道從門控場發(fā)射陣列發(fā)射到真空中并在陽極被收集。真空度決定了傳輸特性和高壓隔離度。他們說,這些器件的高臨界電場和無限制的載流子速度可以導(dǎo)致緊湊的高性能真空設(shè)備在所有指標(biāo)上均能勝過固態(tài)器件,從而使其適用于一系列大功率和高頻應(yīng)用,也可以用作下一代X射線源。

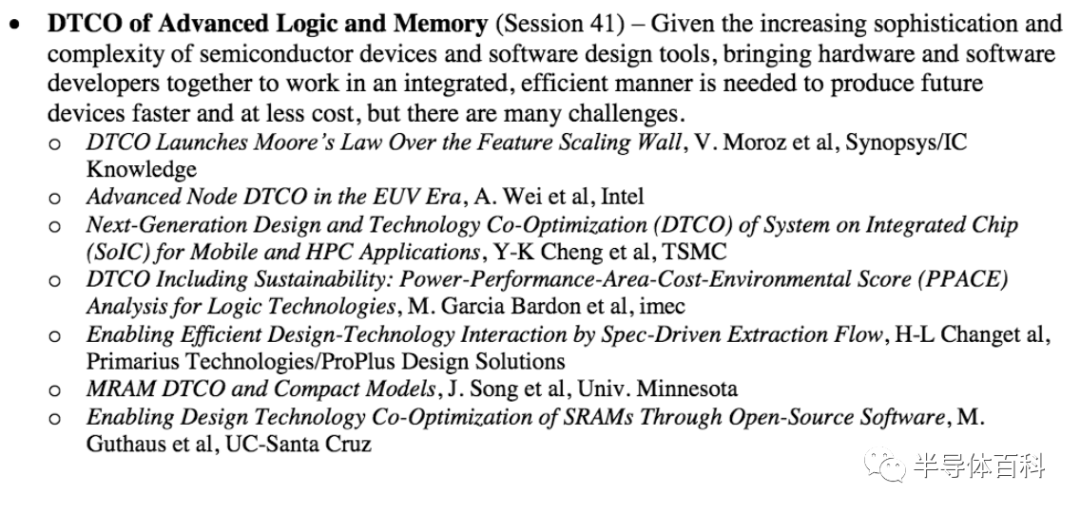

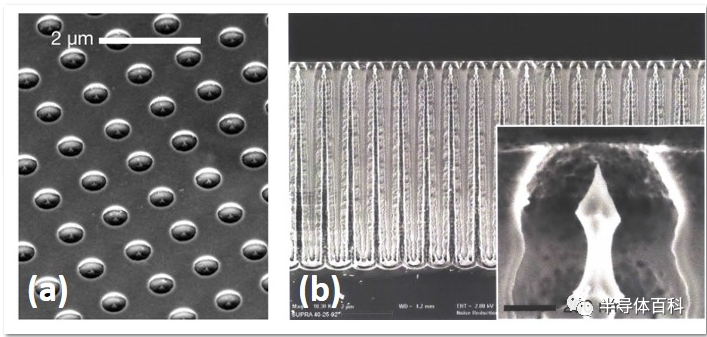

圖1,不同真空器件測試設(shè)置的示意圖。在這兩種方法中,F(xiàn)EA電子源都位于真空中的金屬陽極下方,從而形成了垂直器件。在器件A中,將直徑為1mm的浮球陽極移動到距離FEA芯片一段距離d。在器件B中,固定的45度鉬陽極距離FEA約為1.5厘米。

圖2,(a)通過自對準(zhǔn)制造工藝形成的?200-300nm孔徑的門控尖端陣列 (b)直徑為200 nm的納米線(約6-10μm高)。在該納米線的頂部,存在一個尖銳的尖端,以集中周圍多晶硅柵極的電場。

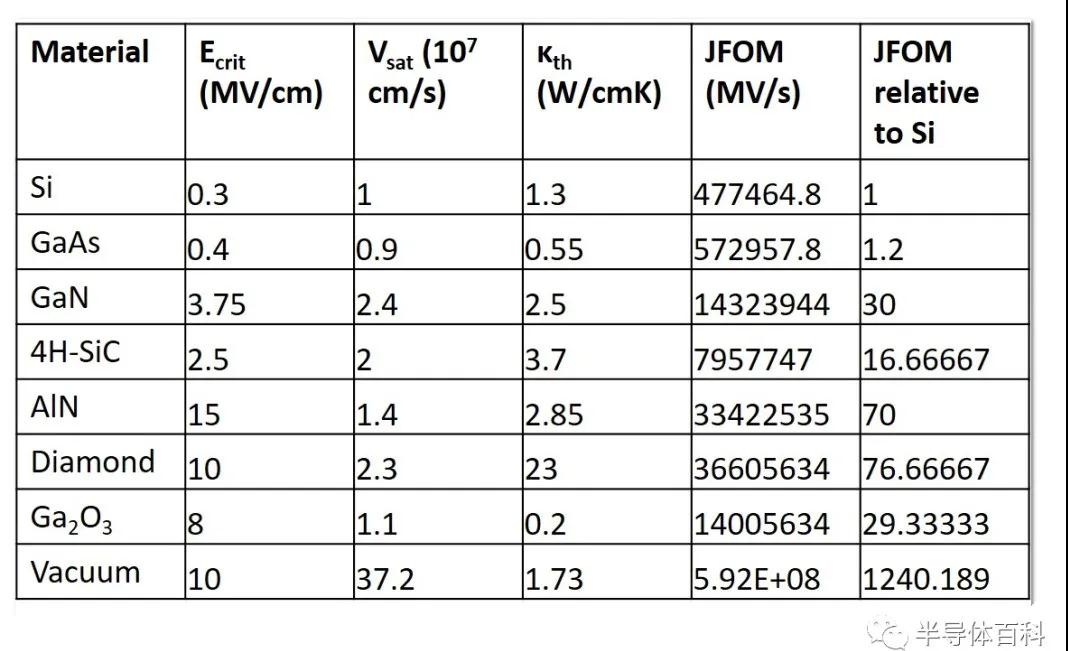

表1,表格比較了各種半導(dǎo)體材料的基本材料特性及其Johnson品質(zhì)因數(shù)(JFOM,這是一種衡量半導(dǎo)體材料對高頻功率晶體管應(yīng)用的適用性的指標(biāo))。它表明,由于真空晶體管的高飽和速度和臨界電場,其真空晶體管的JFOM遠(yuǎn)遠(yuǎn)超過了任何半導(dǎo)體。

Stacked NMOS-on-PMOS Nanoribbons

文章編號20.6,“3-D Self-Aligned Stacked NMOS-on-PMOS Nanoribbon Transistors for Continued Moore's Law Scaling,”C.-Y. Huang et al, Intel。

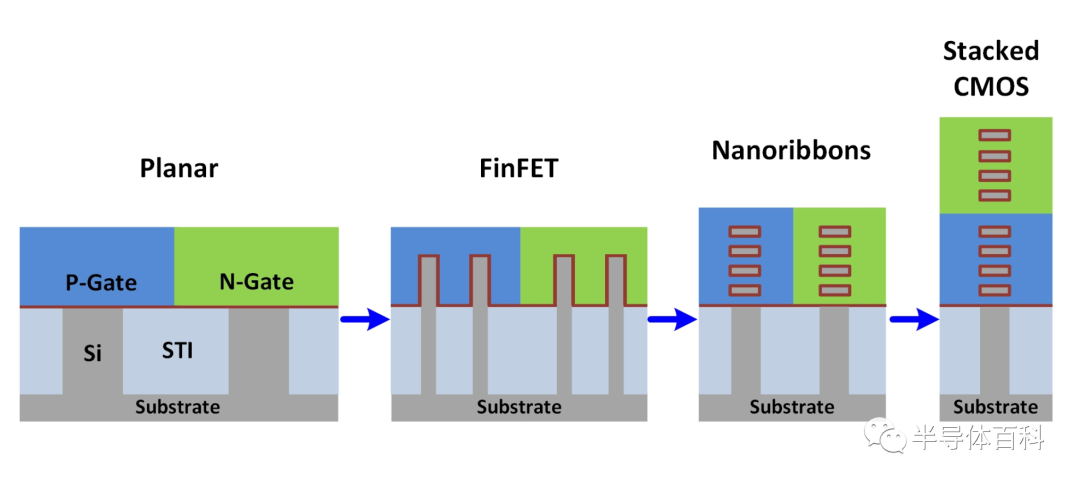

從平面MOSFET到FinFET,再到GAAFET,新穎的晶體管體系結(jié)構(gòu)在推動摩爾定律預(yù)測的性能方面發(fā)揮了關(guān)鍵作用。英特爾研究人員認(rèn)為這一發(fā)展的下一步:由多個自對準(zhǔn)堆疊納米片構(gòu)建的NMOS-on-PMOS晶體管。該架構(gòu)采用垂直堆疊的雙源極/漏極外延工藝和雙金屬柵極制造工藝,能夠構(gòu)建不同導(dǎo)電類型的納米片,以便可以對頂部和底部納米帶進(jìn)行閾值電壓調(diào)整。該方案獲得了出色的電性(亞閾值擺幅<75 mV / dec)和DIBL(對于≥30nm的柵極,<30mV / V),并由于自對準(zhǔn)堆疊而顯著減小了單元尺寸。他們成功采用該架構(gòu)制作了具有良好平衡電壓傳輸特性的功能性CMOS反相器。

附圖:

圖1,晶體管從平面到3D堆疊CFET

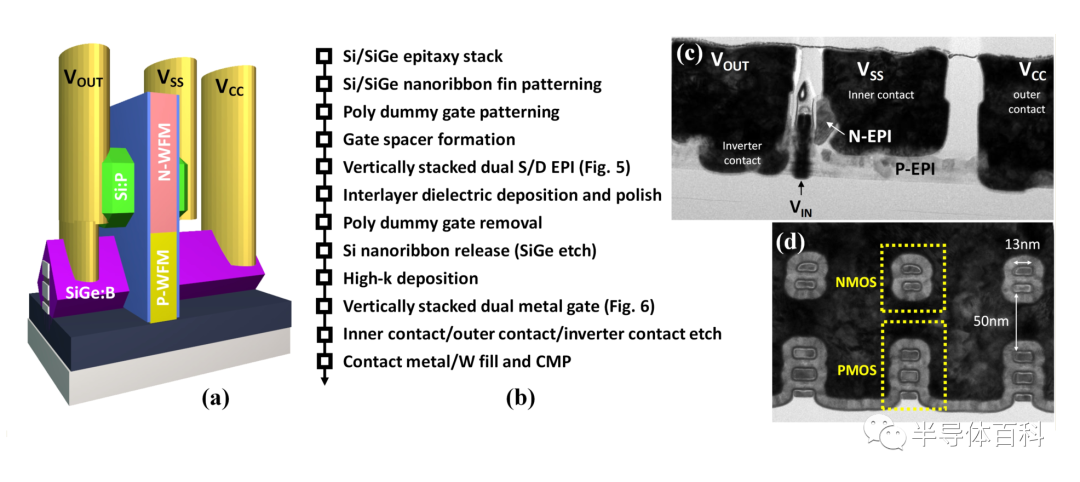

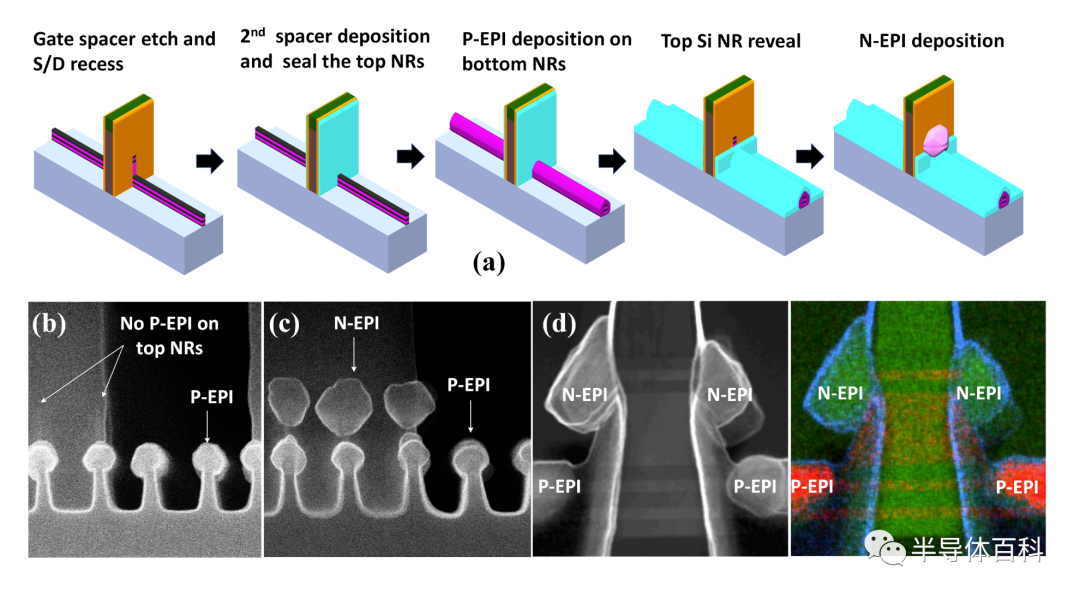

圖2(a)GAA NMOS 堆疊在GAA PMOS上的3D示意圖(b)該工藝流程(c)是具有40nm柵極長度的該CFET的TEM圖像(d)3個Si納米片的GAA PMOS 上堆疊2個Si納米片的GAA NMOS的TEM圖像。

圖3(a)是垂直堆疊雙S / D EPI工藝的工藝流程(b)在底部三個納米片上選擇性生長的P-EPI(c)在頂部兩個納米帶上選擇性生長的N-EPI(d)TEM和EDS圖像顯示在堆疊的納米帶晶體管上選擇性生長的N-EPI和P-EPI。

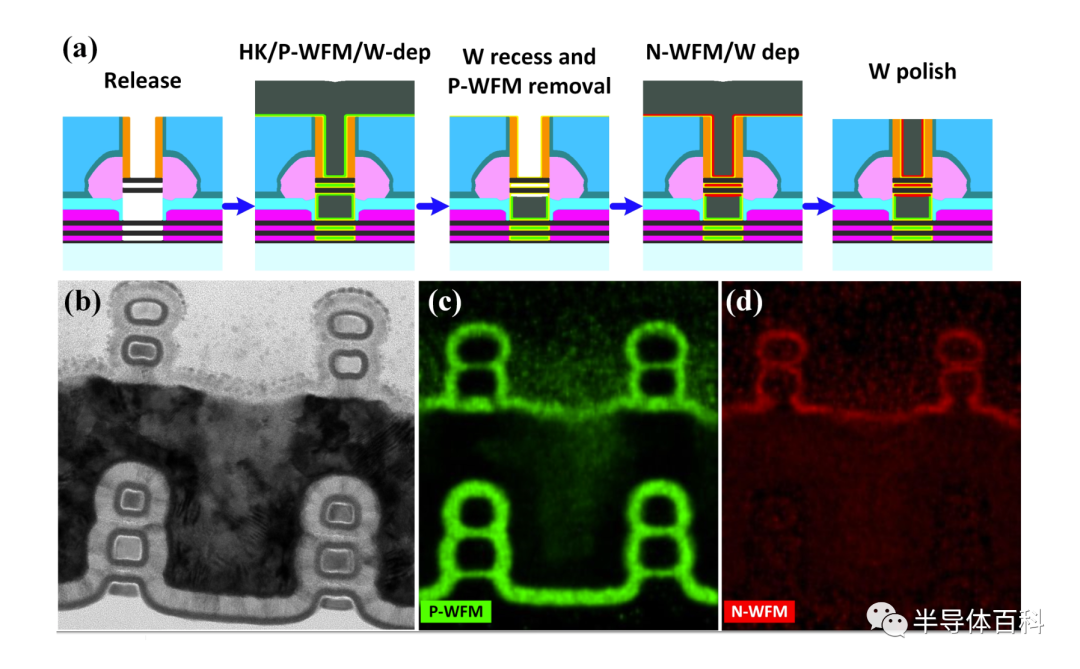

圖4(a)是垂直堆疊雙金屬柵極工藝的工藝流程;(b)TEM圖像(c,d)N-WFM,P-WFM的EDS圖像。

Large-Area Active-Matrix Microfluidics Platform

操作過程演示動態(tài)圖

文章編號35.5 “Large-Area Manufacturable ActiveMatrix Digital MicrofluidicsPlatform for High-Throughput Biosample Handling,”H. Ma et al, Suzhou Institute/Acxell Tech/Hangzhou Linkzill Technology/Univ. Cambridge/ShanghaiJiao Tong Univ。

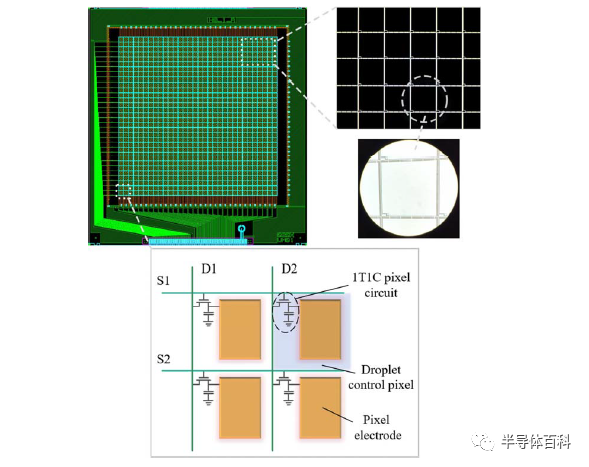

由中科院蘇州醫(yī)學(xué)工程技術(shù)研究所主導(dǎo)的基于電潤濕(Electrowetting)及多晶硅薄膜晶體管的生物樣品的可編程操作技術(shù)。電極陣列按順序在特定位置施加電壓信號,使得表面上的液滴跟隨電場而移動,合并,混合和/或分離。該團(tuán)隊(duì)使用FPD有源矩陣技術(shù)制造了一個芯片,該芯片在10平方厘米的有源區(qū)域中包含一個32×32像素陣列(即電極陣列)。每個像素都可以單獨(dú)或同時尋址,并實(shí)現(xiàn)了在單像素水平上約1%的體積變化系數(shù)的液滴操作。

附圖:

圖1,有源矩陣電介質(zhì)上電潤濕(AM-EWOD)器件的圖像,版圖和像素示意圖。

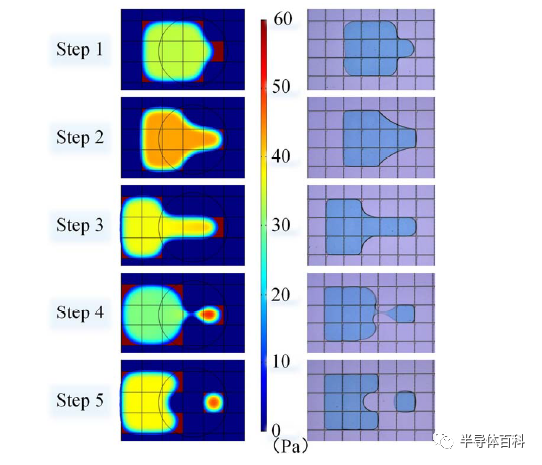

圖2,五步單滴生成方法,其中包含F(xiàn)EA模擬和真實(shí)設(shè)備圖像。

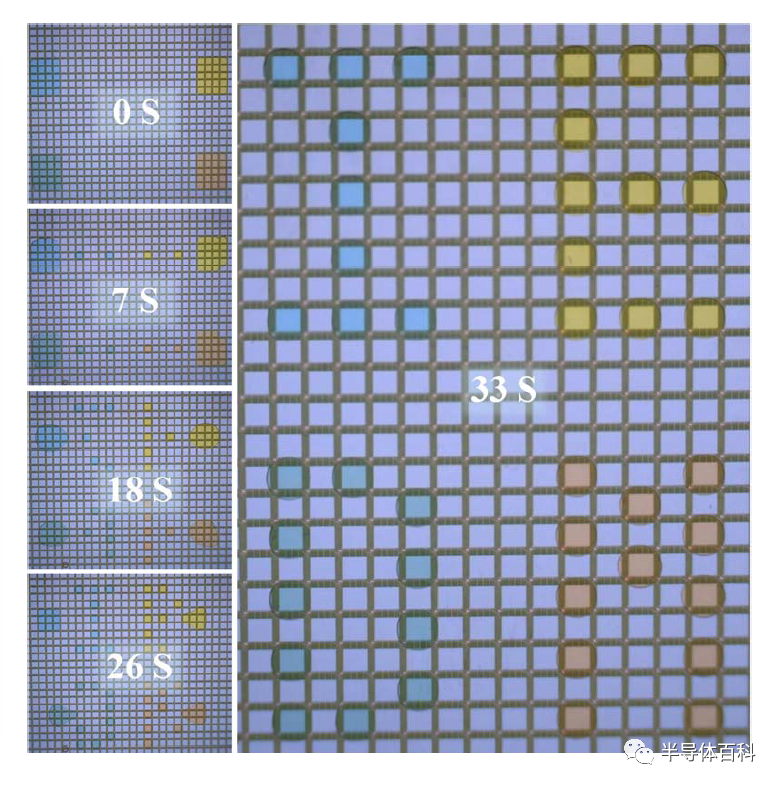

圖3,數(shù)字墨滴在AM-EWOD設(shè)備上形成“ IEDM”。 同時在芯片上實(shí)現(xiàn)并行墨滴生成和大規(guī)模墨滴處理。

當(dāng)然作為半導(dǎo)體制造業(yè)最重要的會議,今年的IEDM上各家公司也都帶來了他們對于邏輯微縮的新看法和技術(shù),以下是重點(diǎn)環(huán)節(jié)預(yù)告,敬請期待。