在今年芯片工業界最重要的會議之一HOTCHIPS上,高級封裝成為了最熱門的議程之一,Intel、TSMC、AMD等業界巨頭都紛紛亮相。事實上,高級封裝正在逐漸取代晶體管特征尺寸縮小,而在成為新的芯片進步的驅動力。

在過去的數十年中,半導體業界公認的主要技術進步推動力是摩爾定律,即周期性地縮小半導體工藝的特征尺寸,從而提升芯片集成度,降低成本,并且提高芯片性能。值得注意的是,降低特征尺寸能降低整體成本是摩爾定律能維持的首要經濟學邏輯,正是它推動了半導體行業幾十年來的高速發展。

然而,在近幾年中,隨著半導體工藝的特征尺寸縮小逐漸接近飽和,再進一步縮小半導體特征尺寸在降低成本方面的獲益已經越來越小(新工藝研發成本極高,導致mask一次性NRE成本過高,僅僅只有極少數芯片公司能從新工藝中獲取成本收益),同時在性能提升方面的收益也越來越小。這個時候,高級封裝就成了延續半導體進步的新驅動力。

高級封裝最關鍵的能力在于提供了一條進一步提升芯片集成度并且降低成本的技術路徑。與摩爾定律試圖縮小晶體管體征尺寸以提升芯片上晶體管數量并提升集成度不同,高級封裝技術使用封裝的形式來提升集成度,并不需要縮小晶體管特征尺寸,因此避開了半導體工藝上一些最難啃的骨頭。除此之外,高級封裝還通過chiplet(芯片粒)的方式進一步提升先進工藝下的芯片良率并降低成本,這一點更進一步地強化了高級封裝技術演進背后的經濟學動力。在傳統的SoC中,如果由于半導體工藝導致的某一個地方出現了瑕疵,那么整個SoC芯片就無法使用。舉例來說,如果整個晶圓上一次能生產10塊大型SoC,同時在成產過程中出現了兩個瑕疵分布在兩塊不同的SoC上,那么就只剩下8塊SoC可以用了,良率為80%。這個良率問題在最新半導體工藝中尤其嚴重。另一方面,如果我們把SoC拆成很多面積較小的chiplet(例如一塊晶圓上可以生產20個這樣的chiplet),那么扣除兩個因瑕疵無法使用的chiplet之后,仍然有18個chiplet可以使用,良率就提升到了90%。在之后,可以使用高級封裝技術把多個chiplet互聯并封裝到一起,能實現和大型SoC一樣的集成度和性能。從這個例子中我們可以看出,高級封裝技術能夠在提升集成度的同時降低成本,從而維護了摩爾定律的基本邏輯。

除了提升集成度和降低成本之外,高級封裝還能提供更高的性能。在人工智能和高性能計算成為半導體市場主要引擎的時代,我們認為IO密度,尤其是計算邏輯和存儲單元之間的IO密度和通信帶寬,已經成為了決定計算性能的主要因素。在這樣的情況下,高級封裝能提供遠超傳統方式的IO密度和通信帶寬,從而能進一步驅動芯片系統的性能。

如上所述,在今天,高級封裝已經能完全實現當年摩爾定律背后的幾大要素:提升集成度,降低成本,以及提升性能,因此它在今天已經成為半導體行業公認的新驅動力。最積極推動高級封裝的廠商包括Intel,以及AMD和TSMC的聯盟,而Intel和AMD恰恰是目前高性能計算的最主流廠商,這也和符合我們之前分析的高級封裝帶來的芯片系統性能提升對于高性能計算應用獲益最大。

高級封裝的“摩爾定律”

在上一代摩爾定律中,集成度、成本、性能等多個因素最后都轉換成了一個指標即特征尺寸,那么在高級封裝領域有沒有類似的單一代表性指標呢?我們認為,在高級封裝領域,這個指標就是芯片間互聯的間距。

隨著芯片間互聯間距的降低,芯片間的IO密度提升,同時芯片間通信的帶寬也相應提升。在高級封裝時代,由于主要的推動力和推動廠商來自于高性能計算領域,因此高級封裝對于芯片系統性能帶來的提升得到了更多關注。而如前所述,IO密度和通信帶寬恰恰是高級封裝給芯片系統帶來性能提升的關鍵,而這樣的性能提升都可以歸結到芯片間互聯的間距這個指標上。

除此之外,芯片間互聯還將影響高級封裝系統的集成度和集成顆粒度。AMD在今年的HOTCHIPS上的演講中,提出了隨著芯片間互聯間距的減小,高級封裝之間芯片堆疊的顆粒度也會越來越細,從之前的處理器核之間的堆疊,逐漸繼續細化到IP和IP之間的堆疊,以及更進一步把單個IP拆到不同的堆疊芯片間,直至實現晶體管顆粒度的堆疊。這樣的進一步細分可以擁有傳統2D集成電路無法實現的能力(例如不同IP之間通過3D堆疊可以大大降低走線長度),從而最終實現傳統2D電路無法實現的集成度。

而高級封裝中芯片間互聯間距的路線圖,TSMC也在今年的HOTCHIPS上給出了規劃,即滿足互聯密度每兩年翻一倍。這樣一來,高級封裝的摩爾定律的所有要素都已經齊全:半導體芯片進化的方向,背后的經濟學邏輯,關鍵指標,以及技術演進時間規律(兩年翻一番)。我們認為,高級封裝的摩爾定律將會在芯片集成度和性能方面慢慢獲得更多的權重,最終實現和半導體器件特征尺寸的摩爾定律一起成為下一代半導體行業的演進規律。

高級封裝的競爭格局

如前所述,目前高級封裝的市場上,高性能計算處理器芯片廠商是主要的玩家,其中就包括了負責芯片、工藝和封裝設計的Intel,而另一方面AMD則和TSMC結成了聯盟,共同開發高級封裝技術以及相關的芯片設計。

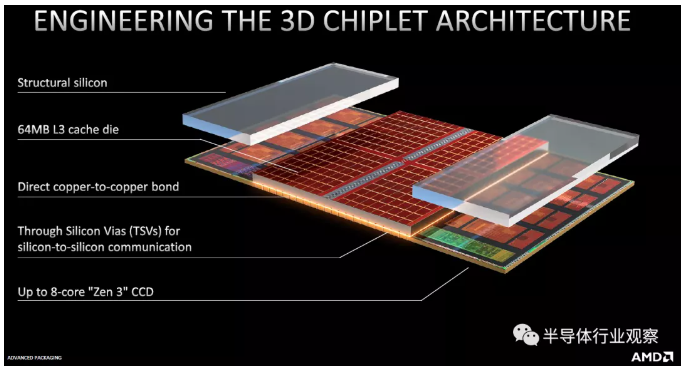

目前,Intel和AMD+TSMC的技術路線基本都已經到了2.5D+3D混合系統集成的階段。所謂的2.5D+3D混合集成,首先使用3D堆疊技術實現多個chiplet的縱向堆疊,之后再把多個經過縱向堆疊的chiplet再使用2.5D封裝技術集成在一起。

AMD通過與TSMC合作,早在幾年前就實現了基于2.5D封裝的chiplet技術(Zepplin),而在今年早些時候更是發布了基于2.5D+3D混合系統集成的3D Chiplet技術,實現了大容量緩存和處理器芯片粒的3D+2.5D集成,其原型芯片在游戲等高性能應用中獲得了顯著的性能增益。TSMC無論是2.5D封裝(InFO和CoWoS)還是3D堆疊技術(SOIC)都處于領先地位,而AMD通過與TSMC的深度合作可望也能實現芯片性能的領先地位。

Intel方面,其2.5D技術是EMIB,通過把互聯優化集中在芯片互聯邊緣處以優化成本,而其3D堆疊技術則是Foveros。今年Intel也公布了其下一代混合2.5D+3D的芯片Ponte Vecchio,通過集成近50個芯片粒,實現超1000億晶體管的超高集成度。

Ponte Vecchio計劃可謂是雄心勃勃,但是如果我們量化比較AMD+TSMC和Intel的高級封裝技術,尤其是比較兩者最關鍵的指標——互聯間距,我們仍然可以看出AMD+TSMC領先一些。在AMD+TSMC已經完成的3D Chiplet原型芯片中,其芯片互聯間隔僅為9um;相對而言,Ponte Vecchio中使用的芯片互連間距為36um。Intel預計在其下一代Foveros Omni中把互聯間距減小到25um,而到達9um則要在更下一代的Foveros Direct。由此,我們認為在未來幾年內,AMD和TSMC的高級封裝技術仍將保持領先狀態,而在這之后的競爭格局,我們還需拭目以待。