“你驗完了沒有?”“芯片還存不存在bug?”

這是芯片驗證團隊經常直面的兩個靈魂問題,這樣的問題,實際上也是對EDA驗證能力的拷問。

5月10日,在南京EDA公司芯華章舉辦的研討會上,多位芯片資深從業者對驗證EDA的痛點和破局之徑進行了深入交流。中興微電子有線系統部部長賀志強談道,隨著集成電路規模、復雜度提升,芯片的“一版成功”已是最低要求。芯片驗證不僅要質量,還要在有挑戰的時間窗內完成。

市場競爭加劇,正進一步壓縮芯片研發周期。燧原科技資深架構師鮑敏祺對此感受深刻,以前做大芯片流片大約需要一年半,現在則可能得縮短至一年。

也就是說,芯片工程師要在更短時間內,做更多門級的驗證工作。芯片規模變大后,整個驗證亦從單點功能升級到整個系統級、場景級的需求。

這些挑戰,正推動著驗證EDA工具加速進化。

EDA(電子設計自動化)軟件被譽為“芯片之母”,是整個集成電路產業鏈“金字塔尖”般的存在。芯片工程師正是借助EDA工具,才得以完成單芯片集成了千億顆晶體管的復雜電路設計。

“沒有好的EDA軟件,我們不可能制造出好的芯片。”合肥市微電子研究院院長陳軍寧說。EDA工具的使用,能極大避免芯片電路設計和布局的錯誤,而高成功率,便意味著更少的損失。

芯片流片費用高到驚人——低端芯片流片一次花費數十萬元,先進制程更是上億。對于一些中小企業來說,如果流片失敗兩三次,它們就可能面臨破產。這要求芯片驗證環節,必須萬無一失。

但在賀志強看來,如何度量質量與效率,仍要打一個問號。其中既有主觀的數據,又有客觀的數據,在各種數據之間如何佐證不同的流程、不同的方法,不同的工具之間又如何關聯,這是留給驗證的問題,亦是給EDA廠商的問題。

EDA集體面對的挑戰,也是國產EDA企業突圍的機會所在。

本文福利:全球EDA行業呈現寡頭壟斷趨勢,國產EDA工具市占率較低,個別點工具成為未來突破口。推薦精品研報《EDA深度報告:半導體賦能基石,國產突圍勢在必行》,可在公眾號聊天欄回復關鍵詞【芯東西261】獲取。

01.

國產EDA風起:

起點高、包袱輕、貼近客戶

國內外動蕩的貿易背景,加速了國內芯片產業對國產EDA的迫切需求。盡管國際三巨頭占據了主要的EDA市場,但隨著技術的飛躍發展,創新產品和新興初創公司仍不斷涌現,國產EDA企業正面對一個前所未有的市場機遇。

據中國半導體行業協會(CSIA)統計,2020年中國EDA行業市場規模約93.1億元,同比增長27.7%,其中我國本土EDA工具市場份額約為12%。

▲2015-2025年中國EDA行業市場規模統計及預測(圖源:概倫電子IPO文件,數據來源:CSIA)

合肥市微電子研究院院長陳軍寧談道,國內EDA公司在全流程工具方面與國際巨頭差距尚存,但在許多點工具方面已與國際水平相當,甚至領先于國際水平。

“國產EDA公司擁有高技術起點和貼近本地市場的優勢,能夠基于客戶的痛點進行開發,將經驗與解決方案集成到工具當中。”中興微電子有線系統部部長賀志強分析說。

起步較晚,使得國產EDA缺乏長期的技術、生態積累及工程經驗,卻也帶來“包袱較輕”的優勢,因而得以輕裝上陣,去破解一些傳統EDA難解的問題。

其中,能檢測芯片各項指標、及時發現缺陷的驗證環節,儼然是EDA亟待優化的重點方向之一。

在陳軍寧看來,下一代EDA工具的挑戰主要來自三方面:(1)新工藝節點不斷涌現,帶來物理驗證和可測性設計方面的挑戰;(2)不斷攀升的設計規模,導致高階綜合功能驗證和物理驗證等運行時長更長;(3)從片上系統到系統對接帶來的設計方法學和驗證方法學的革命性變化。

與此同時,人工智能、5G通信、智能汽車等新應用領域正快速發展,對芯片性能的要求越來越高,功耗、成本的要求趨于分化,導致芯片設計驗證的成本隨之急劇上升。

而復雜且費時費力的調試工程,又是關鍵驗證工作的重中之重。

02.

無法替代的調試工作

在典型的芯片設計過程,驗證占據了約70%的工作量,其中的調試(debug)就占了40%。

驗證包含的原型驗證、硬件仿真、軟件仿真、形式驗證等環節都需要調試。調試在其中穿針引線、綜合資料,然后加以分析,進而達到有效的診斷。

“在整個設計驗證的流程中,debug是不可欠缺、無法替代的。”芯華章科技研發副總裁林揚淳記得,即便是非調試的場景,客戶也常常利用調試工具來檢視和理解整個設計。

但據其調研,調試產品的供需存在著極大落差。

原因有三。一是缺乏創新,人工智能、機器學習和云計算已是不可逆的趨勢,而市面上的產品卻甚少掌握,頂多只是“沾點皮毛”。

二是資料的碎片化、凌亂甚至矛盾。點、步驟之間常常需要轉換,不僅耗時,更容易出錯。“造成如此現象最根本的原因,就是缺乏整體性的規劃,僅憑商業并購,將不同公司的工具拼湊在一起造成的。”林揚淳強調。

兼容性會直接影響芯片工程師的體驗,這是驗證過程中經常遇到的問題。中興微電子有線系統部部長賀志強對此進一步拆解,它既包括不同EDA廠商的工具的兼容性,也包括同一家廠商工具的不同驗證手段的兼容性。后者相對來說沒有太高的技術壁壘,但前者很難做到統一。

三是設計日新月異,規模和復雜度不斷增加,對調試產品的性能要求也不斷提高。

好的調試系統,不僅能確保項目的成功,更可以有效提高SoC芯片的設計和驗證效率,降低芯片設計成本,這將對芯片工程師大有裨益。

03.

走向下一代設計驗證工具

為了適應接踵而至的挑戰,陳軍寧認為下一代EDA設計驗證工具會呈現兩大趨勢:智能化與上云。

EDA智能化,涉及廣義上一切減少人力投入的改進,包括高度并行化的EDA計算、求解空間探索、設計自動化、數據模型化及機器學習等。

新一代EDA將大幅減少芯片架構探索、設計驗證布局布線等工作中的人力占比,把設計經驗和數據吸收到EDA工具中,形成智能化的EDA設計。

另一個趨勢是上云。隨著芯片設計復雜度提升,芯片設計公司將面臨計算資源需求激增、EDA峰值性能需求難以滿足、工藝數據遷移耗費成本巨大、多項目并行發生的資源搶奪以及辦公地點限制帶來的效率影響等問題,進而影響芯片研發周期及成本。

芯片設計如能上云,則可以平滑多項目并行帶來的資源搶奪問題,降低EDA購買成本和維護費用,保障企業研發生產效率,擺脫物理環境束縛,并有助于支持EDA在教育領域的應用。

當前,云平臺的模式還在探索和發展的初期,它不是簡單地將現有EDA放到云計算平臺上,而需采用適合于云平臺的EDA軟件架構、高可靠的安全保證,并要解決其付費模式和使用模式的創新問題。現在已經有混合云、全云等靈活的方式,來滿足芯片設計公司的各種需求。

電子科技大學電子科學與工程學院副教授黃樂天一直在做大規模系統級集成電路設計,他重點提到要增強EDA工具間的融合問題:

首先是加強軟件提前介入驗證的能力,在早期提供方便的虛擬原型驗證環境,使得芯片設計之初即可實現對整體功能進行全面驗證。“目前來看,虛擬原型的驗證環境各家做的都還不夠好,設計方法推廣的也還不夠多。”黃樂天說。

其次是在虛擬原型驗證的基礎上,找到能快速驗證大規模設計的方法學,尤其要加強驗證各IP間、各子系統間交互設計的一些方法,并加強芯片設計和其他外圍系統的一些交互驗證。

他希望將仿真、形式化驗證、原型驗證、調試工具等形成一個完整的整體平臺,或是成系列的一個整體驗證方法學,將各環節的驗證有機協同,相互補充,來極大減少驗證的投入。

更進一步來說,以Chiplet為代表的新一代集成電路的設計方法學正在迭代,其設計空間又增加了一個新維度,隨著設計規模越來越大,軟件結合更為緊密,新的驗證方法學或驗證EDA工具還有很大的改進和整合空間。

04.

多重創新技術加持

芯華章的驗證調試秘招

針對驗證調試方面的挑戰,一些國產EDA企業正為此付諸努力。2020年3月創立的芯華章便是其中的代表之一。過去兩年,芯華章已發布仿真驗證、形式驗證、場景驗證、FPGA原型驗證系統等產品。

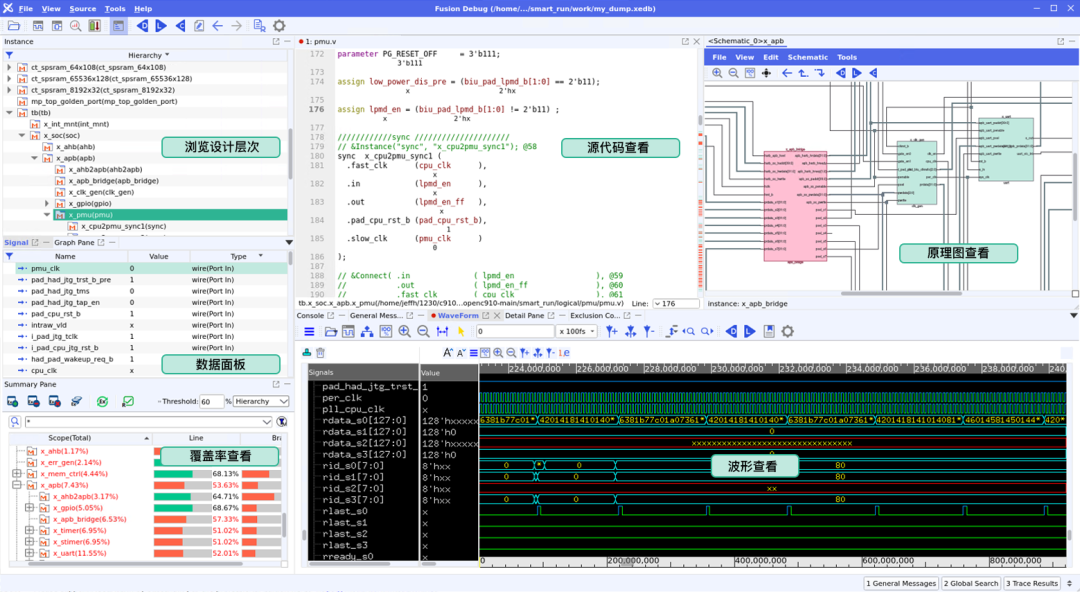

芯華章科技研發副總裁林揚淳也分享了他們的解題思路:其昭曉Fusion Debug是一款基于創新架構的數字驗證調試系統,有創新性、易用性、高性能等特點,提供快速代碼解析、波形查看、設計原理圖探索、覆蓋率數據分析等多種先進技術,能夠幫助工程師簡化調試任務,提高設計和驗證的效率。

除了獨立使用外,該系統還可以配合芯華章智V驗證平臺的所有產品混合使用。它也提供了豐富、可編程的數據接口,以供用戶針對不同調試場景的多樣化需求進行定制化。

據林揚淳回憶,從一開始,芯華章就花心血致力于底層框架、基礎平臺的研發,尤其是精簡連貫一致,形成共同數據庫,其中包括XCDB/XNDB/XEDB/XCovDB。XCDB存儲了design HDL的信息,XNDB記錄了design analyst,XEDB壓縮存儲了信號波形,XCovDB則記錄了覆蓋率。

相比于國際主流數字波形格式,昭曉Fusion Debug采用完全自研的高性能數字波形格式XEDB。該波形格式借助創新的數據格式和架構,具備高性能、高容量、高波形壓縮比等特點,在實際測試中可帶來比國際主流數字波形格式超8倍的壓縮率。

與其它商業波形格式相比,XEDB的讀寫速度快至3倍,并支持分布式架構,能夠充分利用多臺機器的物理資源來提升整體系統的性能,實測中表現出的波形寫入速度可以比單機模式提高5倍以上。

▲Fusion Debug GUI界面

在提供完整調試解決方案的同時,昭曉Fusion Debug也支持統一且高性能的編譯,可供快速加載仿真結果和信號顯示,輕松進行信號連接跟蹤和根本原因分析。根據實際項目數據,在完整的設計及原理圖模塊化加載中,昭曉Fusion Debug的速度比其他商用EDA工具快至5倍,能滿足大規模SoC設計調試的需求,大幅提高驗證效率。

林揚淳談道,智能化是芯華章的優勢之一。昭曉Fusion Debug便融合了先進的機器學習框架,以解決當前產業調試方案缺乏創新、數據庫碎片化及性能局限等多重挑戰,從而降低調試難度,進一步優化驗證效率與操作體驗。

05.

結語:EDA后浪們,正走出自己的路

盡管曾錯失歷史發展良機,如今伴隨著新興技術的成熟、利好政策的相繼落地以及資本熱錢的涌入,國產EDA企業正如雨后春筍般涌現。

后摩爾時代愈發復雜的芯片設計,在給整個EDA產業提出新挑戰的同時,也敞開了技術迭代的新機會窗口。無論是解決各種EDA工具固有的頑疾、更迭設計方法學,還是引入機器學習、云計算等新技術,EDA企業們可以探索的創新方向正趨于豐富。

從長遠來看,國產EDA的發展,不應僅滿足于成為“替代品”,更多要結合EDA多年的發展,在一些新的技術條件和需求上,抓住時間窗口。

誠然,對于國產EDA企業而言,短期內要比肩三大國際巨頭尚是一種奢望。但通過對點工具的鉆研,國產EDA企業已陸續輸出了一些成果。隨著其產品將從客戶側匯集的經驗沉淀到一代又一代的工具迭代中,這些后起之秀正走出自己的路。