在近期激烈的全球競爭中,國產芯片產業(yè)迎來一項重要利好,中國首個原生Chiplet 技術標準正式審定發(fā)布!

在12月16日舉辦的“第二屆中國互連技術與產業(yè)大會”上,由中國集成電路領域相關企業(yè)和專家共同主導制定的《小芯片接口總線技術要求》團體標準正式通過工信部中國電子工業(yè)標準化技術協(xié)會的審定并發(fā)布。

對中國芯片產業(yè)而言,該團體標準是中國首個小芯片(Chiplet)技術標準,意義十分重大,這無疑是一大好消息。

小芯片(Chiplet)技術到底是什么?

所謂的小芯片(Chiplet)技術,在近兩年里收到了業(yè)內的熱烈關注和探討。

小芯片Chiplet又被稱為“芯粒”,Chiplet將復雜芯片拆解成一組具有單獨功能的小芯片單元die(裸片),通過die-to-die的結構將模塊芯片和底層基礎芯片封裝組合在一起。

Chiplet的主要優(yōu)勢包括:

1.可以大幅提高大型芯片的良率;

2.可以降低設計的復雜度和設計成本;

3.還能降低芯片制造的成本。

為什么小芯片被這么多企業(yè)重視呢,原因是因為小芯片Chiplet架構在制程工藝難以進步的情況下,可以實現(xiàn)晶體管密度的突破,因此對于半導體行業(yè)來說非常重要。

早在2010年,蔣尚義先生提出通過半導體公司連接兩顆芯片的方法,區(qū)別于傳統(tǒng)封裝,定義為先進封裝 。

2015年Marvell創(chuàng)始人之一周秀文(Sehat Sutardja)博士曾提出Mochi(Modular Chip,模塊化芯片)架構的概念,這是芯粒早期雛形。

而AMD是率先將芯粒技術大規(guī)模應用于商業(yè)產品的公司之一,在第三代銳龍(Ryzen)處理器上AMD便是復用了第二代霄龍(EPYC)處理器的IO Chiplet。直到2019年,國內華為等公司也在產品中使用芯粒技術。

在2022年舉辦的基金委雙清論壇上,孫凝暉院士、劉明院士、蔣尚義先生等討論提出了“集成芯片”概念,也是對芯粒集成芯片的概括和定義。不過,網(wǎng)上也有一些值得關注的觀點。清華大學魏少軍教授指出,Chiplet處理器芯片是先進制造工藝的“補充”,而不是替代品。“其目標還是在成本可控情況下的異質集成。”

那么此次國內審定發(fā)布的《小芯片接口總線技術要求》中都講了哪些內容呢?

據(jù)悉,《小芯片接口總線技術要求》描述了 CPU、GPU、人工智能芯片、網(wǎng)絡處理器和網(wǎng)絡交換芯片等應用場景的小芯片接口總線(chip-let)技術要求,包括總體概述、接口要求、鏈路層、適配層、物理層和封裝要求等。

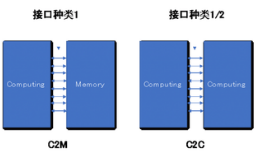

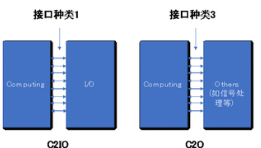

據(jù)介紹,小芯片接口技術有以下應用場景:

·C2M (Computing to Memory),計算芯片與存儲芯片的互連。

·C2C (Computing to Computing),計算芯片之間的互連。兩者連接方式:

·采用 并行單端 信號相連,多用于 CPU 內多計算芯片之間的互連。

·采用 串行差分 信號相連,多用于 AI、Switch 芯片性能擴展的場景。

·C2IO (Computing to IO),計算芯片與 IO 芯片的互連。

·C2O (Computing to Others),計算芯片與信號處理、基帶單元等其他小芯片的互連。

此標準列出了并行總線等三種接口,提出了多種速率要求,總連接帶寬可以達到 1.6Tbps,以靈活應對不同的應用場景以及不同能力的技術供應商,通過對鏈路層、適配層、物理層的詳細定義,實現(xiàn)在小芯片之間的互連互通,并兼顧了 PCIe 等現(xiàn)有協(xié)議的支持,列出了對封裝方式的要求,小芯片設計不但可以使用國際先進封裝方式,也可以充分利用國內封裝技術積累。

(《小芯片接口總線技術》標準概況圖)

換個角度來看,小芯片Chiplet技術其實就是模塊化的芯片技術,可以由多個不同制程、架構、功能的小芯片堆疊出全功能芯片,在半導體行業(yè)已經極為常見。此次中國發(fā)布原生Chiplet小芯片標準,無疑將推動本土半導體芯片這一領域的發(fā)展。

單片式SOC與Chiplet SOC的比較

Chiplego首席技術顧問曾在《揭秘后摩時代芯片產業(yè)方向:Chiplet技術》一文中提到,在不考慮制造成本的情況下,人們總是認為單片SOC可以比Chiplet SOC提供更好的性能和功耗。事實上,單片SOC中每個模塊都能以最小的延遲進行通信,這使得前者比Chiplet SOC的性能更好。然而,如果把制造成本作為一個芯片設計目標,那么有些單片SOC設計可能會成為一個不可能完成的任務。

他以AMD的64核Chiplet芯片設計為例:在7nm技術中,CPU Chiplet尺寸約為81mm^2;在12nm技術中,I/O芯片的尺寸約為125mm^2。如果采取單片設計方法,單片SOC的裸片尺寸應該在700mm^2到800mm^2之間。

(Chiplet與SoC的區(qū)別)

而在目前的EUV曝光機中,光掩模版尺寸約為858mm^2。在未來的High-NA EUV中,光掩模版可能會小于450mm^2。因此,無論采用哪種情況,AMD 64核SOC的單片設計都難以生產,即使單片設計能提供卓越的性能和功耗。如果人們仍然想以單片SOC中完成64個CPU Core的設計,只有通過減少高速緩存的大小,比如縮減一半甚至更多,這樣芯片尺寸就可以減少一半,單片SOC在7nm中可以達到400mm^2左右,但這種設計方案在生產成本方面并不合理。總而言之,在一個系統(tǒng)中,不同的功能和特性所需要的工藝技術往往是不兼容的。例如,DRAM和RF工藝技術與邏輯SOC就不兼容。在這種情況下,單片SOC是不可能的。如果想把這些功能塊集成到一個封裝中,Chiplet SOC是唯一的解決方案。

科技巨頭率先成立了Chiplet標準聯(lián)盟

整個芯片產業(yè)其實很早就做好了迎接Chiplet技術的準備。在今年3月,英特爾、AMD、ARM、高通、臺積電、三星、日月光、Google云、Meta(Facebook)、微軟等十大行業(yè)巨頭聯(lián)合成立了Chiplet標準聯(lián)盟(UCIe 聯(lián)盟),正式推出了通用芯粒互連技術(Universal Chiplet Interconnect Express)。該聯(lián)盟成立的目的旨在推動Chiplet接口規(guī)范的標準化,并已推出UCIe 1.0版本規(guī)范。

需要指出的是,通用芯粒互連技術(UCIe)是一個開放的芯粒互連協(xié)議,旨在芯片封裝層面確立互聯(lián)互通的統(tǒng)一標準,滿足客戶對可定制封裝要求。通用芯粒互連技術提供了物理層和die-to-die適配器。物理層包含裸片間通信的電氣信號、時鐘標準、物理通道數(shù)量等規(guī)范,可以包含來自多家不同公司當前所有類型的封裝選項,包括標準2D封裝和更先進的2.5D封裝。隨著3D芯片封裝的推出,UCIe標準還需不斷升級,未來也將最終擴展到3D封裝互連。

相比之下,國內本土半導體廠商在Chiplet這一塊一直以來都比較欠缺。據(jù)了解,UCIe聯(lián)盟成員共分為三個級別,分別是發(fā)起人、貢獻者(Contributor)和采用者(Adopter),發(fā)起人由董事會組成并具有領導作用,貢獻者和發(fā)起者公司可以參與工作組,而采用者只能看到最終規(guī)范并獲得知識產權保護。

目前,UCIe聯(lián)盟目前僅開放后兩個會員級別申請。此前已有芯原、芯耀輝、芯和半導體、芯動科技、芯云凌、長芯存儲、長電、超摩科技、奇異摩爾、牛芯半導體、OPPO等多家大陸企業(yè)先后宣布加入UCIe行業(yè)聯(lián)盟,隨著中國Chiplet生態(tài)圈不斷壯大,阿里巴巴也在今年8月入選了董事會成員,標志著UCIe進入一個新的里程碑。

有人認為,Chiplet對中國解決先進芯片技術瓶頸具有重要意義,是中國市場換道超車重要技術路徑之一。不過,清華大學教授魏少軍卻指出,Chiplet處理器芯片是先進制造工藝的“補充”,而不是替代品。“其目標還是在成本可控情況下的異質集成。”清華大學集成電路學院院長吳華強也表示,Chiplet不是先進芯片制造的替代品,但它們可能有助于中國建立“戰(zhàn)略緩沖區(qū)”,提高本地的性能和計算能力,以制造用于數(shù)據(jù)中心服務器芯片。

部分巨頭推出Chiplet相關產品

值得一提的是,小芯片Chiplet技術的落地并非是廠商們的空談,像英特爾、AMD、ARM等均已經推出了Chiplet小芯片架構。

英特爾在2021年架構日時就披露了有關其下一代至強可擴展平臺的功能,其中之一是向tiled架構的轉變。英特爾將通過其快速嵌入式橋接器組合四個 tile/chiplet,從而在更高的內核數(shù)下實現(xiàn)更好的CPU可擴展性。此舉也跟其他公司一樣,通過“更小的核心”或“連接在一起的單個chiplet”這兩種途徑之一,來實現(xiàn)更多的服務器平臺核心數(shù)量。

此前,AMD曾推出基于臺積電3D Chiplet封裝技術的服務器處理芯片。在今年11月,AMD正式發(fā)布了采用RDNA3架構的新一代旗艦GPU——RX7900XTX和RX7900XT。AMD表示,這是公司首度在GPU產品中采用小芯片(Chiplet)技術,即臺積電的“3D Fabric”技術,也是全球首個導入Chiplet技術的游戲GPU。與使用更傳統(tǒng)GPU設計的RDNA2相比,該款產品擁有多達580億個晶體管,每瓦特性能提升了54%,并且提供高達61TFLOP的算力;

同樣,在2019年美國圣塔克拉拉舉辦的開放創(chuàng)新平臺論壇上,知名IP大廠Arm與臺積電共同發(fā)表業(yè)界首款采用臺積電先進CoWoS封裝解決方案并獲得硅晶驗證的7nm小芯片Chiplet系統(tǒng),其中內建Arm多核心處理器。據(jù)悉,這款小芯片系統(tǒng)成功展現(xiàn)出結合了7nm FinFET制程及4GHz Arm核心所打造出的高效能運算的系統(tǒng)單芯片(SoC)關鍵技術,結合了臺積電創(chuàng)新的先進封裝技術與Arm架構卓越的靈活性及擴充性,為將來生產就緒的基礎架構SoC解決方案奠定絕佳基礎。

GPU、FPGA市場應用潛力巨大

目前Chiplet已經有少量商業(yè)應用,并吸引廣大國際芯片廠商投入相關研發(fā),在當前SoC遭遇工藝節(jié)點和成本瓶頸的情況下,Chiplet有望發(fā)展成為一種新的芯片生態(tài)。根據(jù)市場研究機構Omdia(原IHS)的預測,2024年Chiplet市場規(guī)模將達到58億美元,而到2035年則將達到570億美元。

其中,Chiplet在GPU、FPGA這兩個有著高算力特點發(fā)熱領域應用潛力巨大,具備芯片設計能力的IP供應商更有機會脫穎而出。但與此同時,Chipet未來充滿機遇的同時也有挑戰(zhàn)存在,技術層面上Chiplet面臨著連接標準、封裝檢測、軟件配合等幾方面的挑戰(zhàn)。

在連接標準上,不同供應商的Chiplet接口標準不同,比如OpenCAPI、Gen Z、CCIX、CXL等等。因此需要有統(tǒng)一的標準將不同制程/材質的die連接組成一個系統(tǒng);封裝檢測方面,芯片間支持的帶寬大小不同對應了不同的封裝技術,選擇封裝技術的時候需要綜合考慮成本和連接性能。在檢測方面,Chiplet需要在封裝前對裸片(Die)進行測試,相較于測試完整芯片難度更大,尤其是當測試某些并不具備獨立功能的Chiplet時,測試程序更為復雜;軟件配合方面,Chiplet的設計制造需要EDA軟件從架構到實現(xiàn)再到物理設計全方位進行支持,另外各個Chiplet的管理和調用也需要業(yè)界統(tǒng)一的標準。

更多信息可以來這里獲取==>>電子技術應用-AET<<