聲發射技術是光纖傳感技術和聲發射技術相結合的產物,是目前聲發射技術的發展趨勢。它將高靈敏度聲發射傳感器安裝于受力構件表面以形成一定數目的傳感器陣列,實時接收和采集來自于材料缺陷的聲發射信號,進而通過對這些聲發射信號的識別、判斷和分析來對材料損傷缺陷進行檢測研究并對構件強度、損傷、壽命等進行分析和研究。

在實際的構件檢測中,現場聲源信號通常是在100~800 khz之間的微弱高頻信號,而且材料損傷檢測、聲發射源定位往往需要多個傳感器形成傳感器陣列,而聲發射信號的數據傳輸系統必須達到640 mbps以上的數據傳輸能力;并應具有應付突發或長時間數據接收和存儲能力。本文就是利用CPLD來實現對聲發射信號的采集,從而有效解決了數據的實時傳輸和存儲問題。

1 系統方案設計

本方案采用fifo存儲器構成外部大容量數據緩沖區,而使用pci總線的dma傳輸方式與微機進行高速數據傳輸。現場聲發射信號經過ad轉換和驅動電路驅動后進入pci板卡,然后將部分數據鎖存,同時將并行信號轉換為串并行信號,通過cpld控制邏輯電路存入fifo。當fifo存儲器中的數據到達一定狀態時,cpld控制

邏輯會產生中斷信號給pci9054總線控制器,之后由后者啟動dma傳輸將數據傳人計算機內存中。dma傳輸完成后,pci9054產生通道中斷,并由計算機將數據從內存取出存入硬盤。該數據存儲傳輸模塊的總體框圖如圖1所示。

2 fifo數據存儲電路設計

fifo是一個先人先出的雙口緩沖器,為保證整個系統正常工作,fifo存儲器允許系統進行dma操作,以提高數據的傳輸速度。否則,數據傳輸將達不到傳輸要求,而且會大大增加cpu的負擔,甚至無法同時完成數據的存儲。

本設計在數據傳輸系統中采用了六片idt72281芯片來緩存數據,并將其分成兩組,其中由三片fifo進行字寬擴展,圖2所示是其緩存傳輸示意圖。按照這種設計,其字寬可達27位,可以傳輸24位數據和兩個otr位。

3 cpld邏輯控制

本系統中由于要對高速信號進行處理,因此,對控制信號的時序要求比較嚴格。在控制芯片的選擇上要盡量選用時延小、速度快的芯片。本設計采用美國altera公司的max7000s系列可編程邏輯器件epm7128slc84-15,并采用max+plusⅱ來完成系統的輸入、編譯、驗證及編程,進而完成向量測試及仿真.最后的數據可通過下載線傳輸到芯片中來完成芯片的配置。

3.1 cpld邏輯控制電路

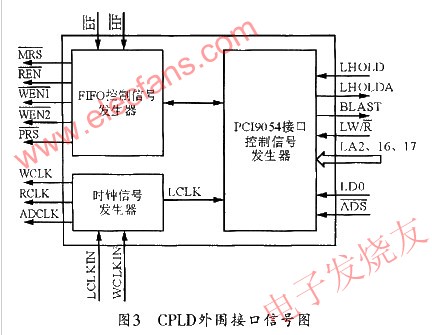

cpld為采樣控制器的核心,數據傳輸所要求的嚴格時序控制關系就由cpld負責處理。它在本系統中主要負責產生與pci9054的握手信號、數據存儲器的片選信號和讀寫控制信號。cpld的外圍信號接口如圖3所示。

cpld可根據fifo存儲器的時序控制要求產生控制信號,并在第一個時鐘周期中將數據分別存入fifo和數據鎖存器74ls373中,而在第二個時鐘周期將鎖存器中的數據再存入fifo,從而完成并行數據向串行數據的轉換。同時根據存儲器的相關信號向pci9054控制器發出中斷請求,并在pci9054讀取數據時產生相應的控制邏輯。

3.2 cpld控制邏輯

當并行數據進入板卡后,cpld首先將一部分數據存入鎖存器,而將另一部分數據直接存入fifo。但此時必須將寫時鐘信號wclk進行二分頻,以便在一個ad轉換周期內完成兩次fifo寫操作。當fifo數據到達半滿時,cpld便向pci9054發出中斷申請,并由pci9054將該申請傳入計算機。若系統響應該中請,則在中斷響應程序內發出讀命令,以讀取字節數和地址信號等。

pci9054通過lhold申請local總線控制權,而cpld則通過lholda響應,以使pci9054能得到局部總線的控制權。pci9054首先將pci地址窄間映射到本地地址空間,接著啟動本地總線的散聚dma周期。cpld收到讀信號(lw/r)、地址選通信號(ads)和地址(la16、la17)后便開始傳送數據。當la16位為0,la17位為1時,系統將使能后三片fifo的讀使能端(ren2),以使后三片fifo數據線上的q0~q31有效而同時也使pci9054的準備好信號(ready)有效,開始數據傳送。在最后一個數據傳送之前,blast信號有效,之后,cpld將在一個時鐘周期后使fifo的讀使能(ren1或ren2)無效,從而完成一次數據傳送過程。

3.3 控制程序設計

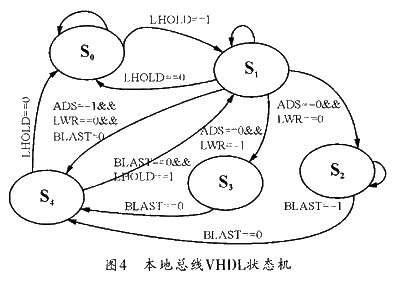

pci9054單周期讀、寫和dma讀的vhdl語言時序控制狀態機設計如圖4所示。圖中,s0為空閑狀態。當本地總線請求信號lhold被置1時轉到s1,否則留在s0。s1為總線保持狀態,此狀態下應將本地總線響應信號lholda置1。如ads信號為0且lw/r為1則轉到s3,如ads信號為1且lw/r和blast為0則轉到s4,這種狀態表明此次讀操作為單周期讀。s2為dma讀狀態,在此狀態下應將ready信號和fifo讀使能信號ren1置0。如blast為1,則表明此次dma讀取還未完成,應繼續留在s2,如blast為0,則表明此次dma讀取完成,可轉到s4。s3為單周期寫狀態,此狀態下也要置ready信號為0以表示寫數據有效,并在blast為0時轉到s4。s4為讀寫操作完成狀態,當lhold被置0時,表明pci9054不再請求本地總線,此時應轉到s0,當blast為0且lhold為1時,表明pci9054還要進行數據讀寫,故應轉到s1繼續操作。

3.4 控制程序邏輯的仿真結果

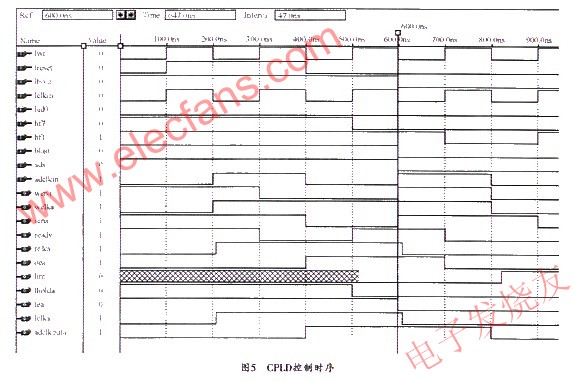

max+plusⅱ是開發aletra公司的fpga/CPLD系列產品的軟件工具,本設計利用此工具提供的設計環境和設計工具來對cpld控制程序進行開發和調試。其功能時序如圖5所示。

cpld的設計是用vhdl編程實現的。本設計的操作代碼都已經過仿真,并在實際調試中得到應用。

4 系統驅動程序設計

本設計使用driv erworks的driverwizard來創建wdm框架程序。可根據設計需求添加程序代碼,從而完成pci設備的dma傳輸系統驅動程序,以執行dma操作、訪問i/o端口和存儲器空間、處理器中斷和訪問pci。根據系統需要,驅動程序的關鍵是三個方面:硬件訪問、中斷處理和dma傳輸。

kdmaadapter類可用于建立一個dma適配器,以標明一個dma通道的特性和提供串行化訪問服務;kdmatransfer類則用于控制dma的傳輸和啟動dma傳輸,以傳輸dma數據緩沖區物理地址和字節數,dma傳輸結束后,數據將由公用緩沖區拷貝到應用數據緩沖區;kcommon dmabuffer用于實現公用緩沖區的操作。對于dma操作,本系統還提供了一個特殊的內存,即公用緩沖區。應當說明的是,公用緩沖區是稀有的系統資源,應該避免浪費使用。

5 結束語

本文給出了數據緩存、傳輸模塊控制電路的設計,并采用vhdl語言和cpld很好的完成邏輯控制任務和系統驅動程序的編寫與調試。實驗結果表明,該數據存儲傳輸模塊的硬件、軟件工作十分可靠、穩定,可實現640 mbps(80 mbyte/s)以上實時數據的存儲與傳輸,完全能滿足聲發射信號采集的要求。