引 言

RC6是作為AES(Advanced Encryption Standard)的候選算法提交給NIST(美國國家標準局)的一種新的分組密碼。它是在RC5的基礎上設計的,以更好地符合AES的要求,且提高了安全性,增強了性能。根據AES的要求,一個分組密碼必須處理128位輸入/輸出數據。盡管RC5是一個非常快的分組密碼,但它處理128位分組塊時用了2個64位工作寄存器;而AES目前在講究效率和簡潔方面不支持64位操作,于是RC6修正這個錯誤,使用4個32位寄存器而不是2個64位寄存器,以更好地實現加解密。利用FPGA來實現RC6算法,可以提高運算速度。芯片設計為RC6算法處理器,輔助計算機處理器完成加解密操作,可以方便地實現對加解密的分析和研究。因此,此芯片可以作為協處理器來看待。

1 RC6算法

1.1 RC6算法概述

RC6秉承了RC5設計簡單、廣泛使用數據相關的循環移位思想,同時增強了抵抗攻擊的能力,改進了RC5中循環移位的位數不依賴于寄存器中所有位的不足。RC6新的特色是輸入的明文由原先2個區塊擴展為4個,另外在運算方面則是使用了整數乘法,而整數乘法的使用則在每一個運算回合中增加了擴散(diffusion)的行為,并且使得即使很少的回合數也有很高的安全性。同時,RC6中所用的操作可以在大部分處理器上高效率地實現,提高了加密速度。RC6是一種安全、架構完整而且簡單的區塊加密法。它提供了較好的測試結果和參數方面相當大的彈性。RC6可以抵抗所有已知的攻擊,能夠提供AES所要求的安全性,可以說是近幾年來相當優秀的一種加密法。

RC6不再使用2個64位工作寄存器,而是用4個32位寄存器。這就使得在每次循環中要進行2次循環移位操作,讓更多的數據位來決定循環次數。RC6把明文分別存在4個區塊A、B、C、D,剛開始分別包含明文的初始值,加密運算后則為4個密文的輸出值。

1.2 RC6的工作原理

RC6是參數變量的分組算法,實際上是由3個參數確定的一個加密算法族。一個特定的RC6可以表示為RC6一w/r/b,3個參數w、r和b分別為字長、循環次數和密鑰長度。AES中,w=32,r=20。本設計中,密鑰長度b為128位(16字節)。RC6用4個w位的寄存器A、B、C、D來存放輸入的明文和輸出的密文。明文和密文的第一個字節存放在A的最低字節,經過加解密后,得到的明文和密文的最后一個字節存放在D的最高字節。

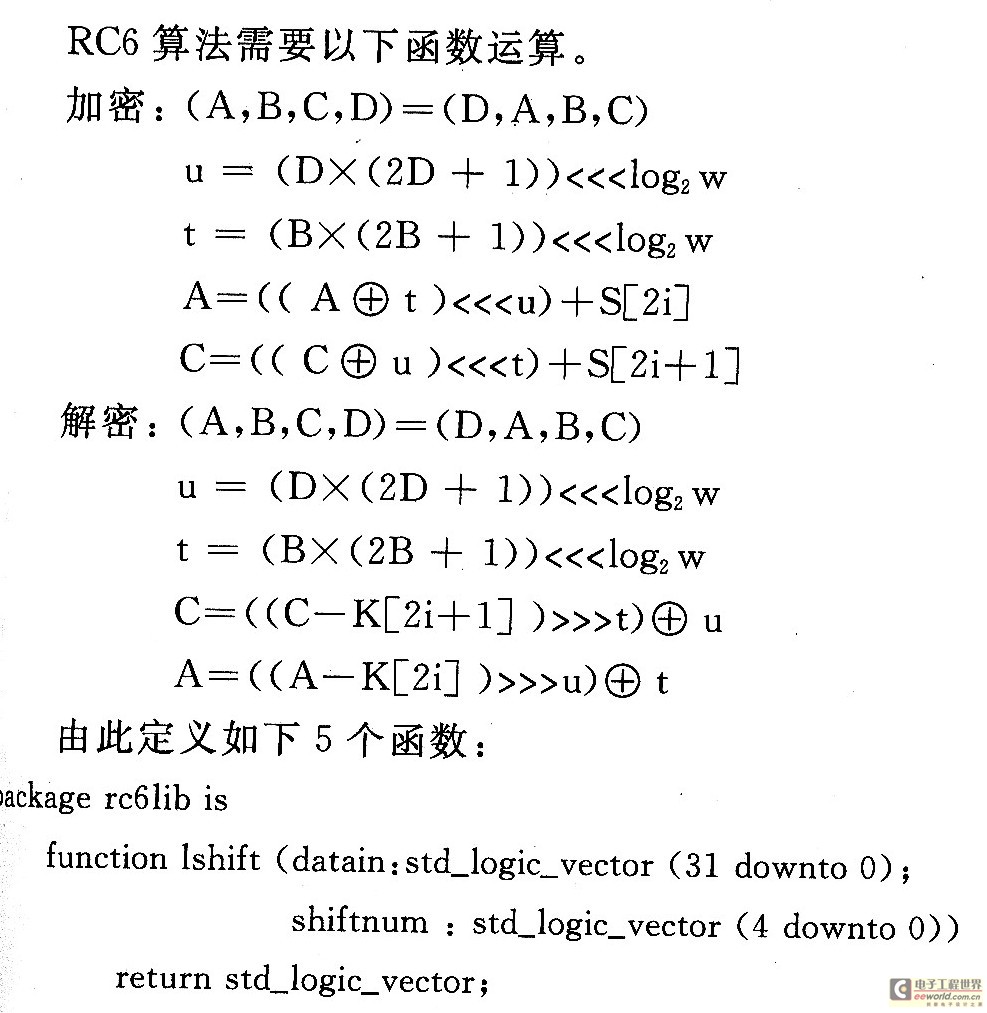

1.2.1 RC6一w/r/b基本運算

基本運算共有如下6種:①模2w加算運算,表示為“+”;②模2w減法運算,表示為“一”;③逐位異或運算,表示為“⊕”;④循環左移,字a循環左移b位表示為“a<<

1.2.2 RC6一w/r/b加密算法

輸入:明文存放在4個w位輸入寄存器A、B、C、D

式中:e一2.782 818 284 59…(自然對數);φ=1.618 033 988 749…(黃金分割)

當w分別為16、32、64時,常數Pw、Qw分別如表1所列。在本設計中,w=16,輸入為128位的主密鑰,得到的是44個32位子密鑰。

2 RC6加解密算法協處理器設計

2.1 RC6協處理器的頂層結構設計

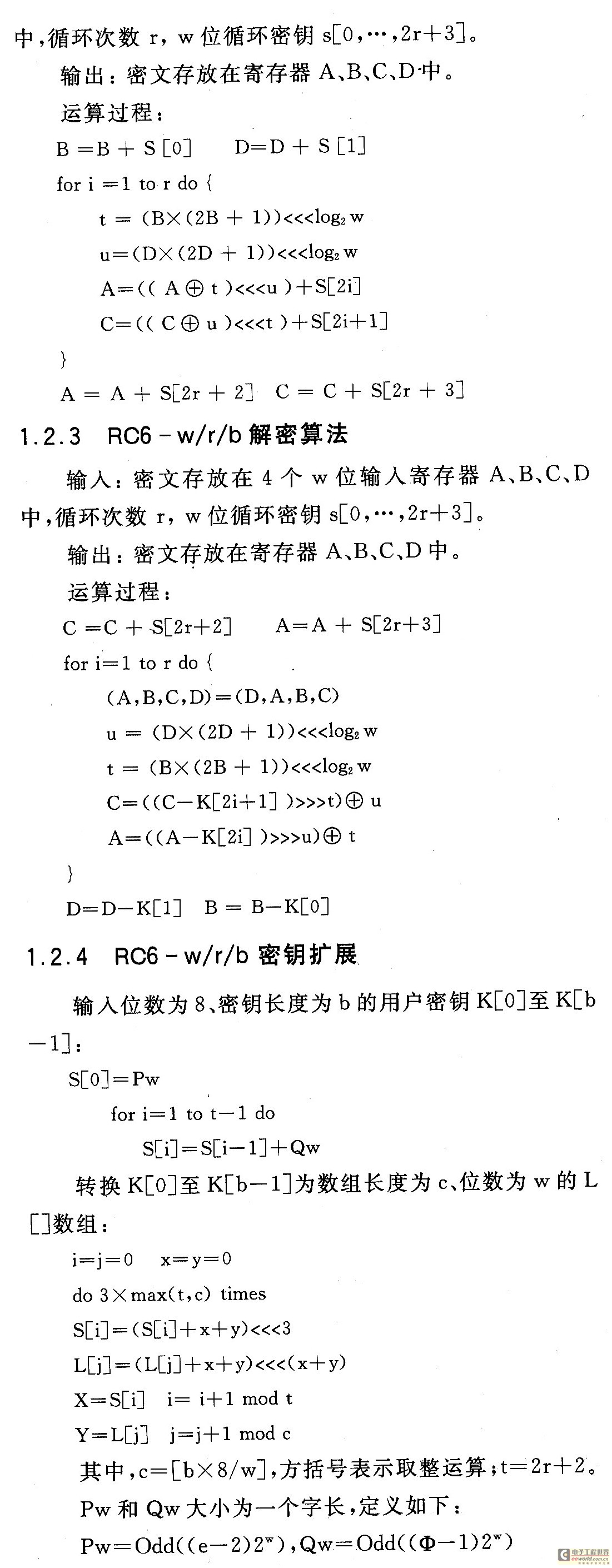

RC6協處理器包含以下3個模塊:加解密模塊,加解密函數模塊和ROM模塊。頂層結構如圖1所示。

加解密模塊:包括輸入和輸出、加/解密選擇、狀態機,以及函數調用聲明和ROM調用取址。用于輸入128位明文或密文,并且利用一個狀態機定義程序順序執行和保證循環控制,實現對ROM的44個子密鑰讀取,以及將數據輸入函數中進行處理。由于輸入ROM的地址是在一個時鐘控制下,子密鑰數據的輸出有一定的延時,所以利用一個控制變量cnt實現地址提前一個時鐘左右輸入ROM,ROM接收到后輸出子密鑰,使在進行數據加解密處理時,已經有準備好的子密鑰調用。

加解密函數模塊:利用work用戶自定義函數庫,定義算法中用到的函數。其中包括5個函數,分別是:RFunct、afunct、cfunct、lshift、rshift。頂層文件循環調用此函數21次,進行加解密運算。

ROM模塊:先在QuartusII里面將預定義的子密鑰輸入rc6keyrom.mif文件中,調用QuartusII的MegaWizardPlug—In Manager,自動生成ROM,供頂層文件調用。需要提前利用QuartusII建立一個.mif文件,將子密鑰的數據輸入。

2.2 RC6協處理器的頂層原理圖

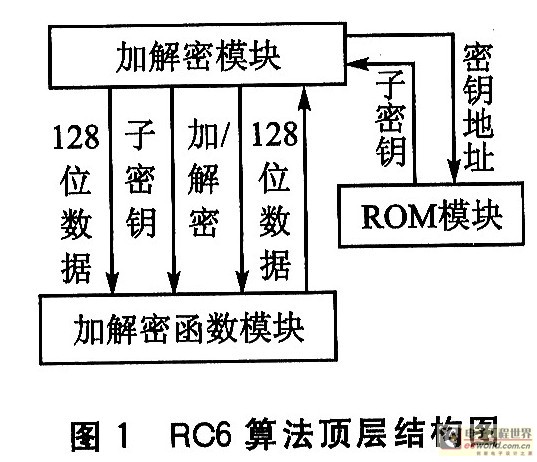

如圖2所示,基于FPGA的RC6算法協處理器分3個模塊:頂層模塊、RC6加解密函數模塊和ROM模塊。共有260個I/0口,包括131輸入端口和129個輸出端口。

2.3 各模塊的功能及實現

2.3.1 ROM模塊

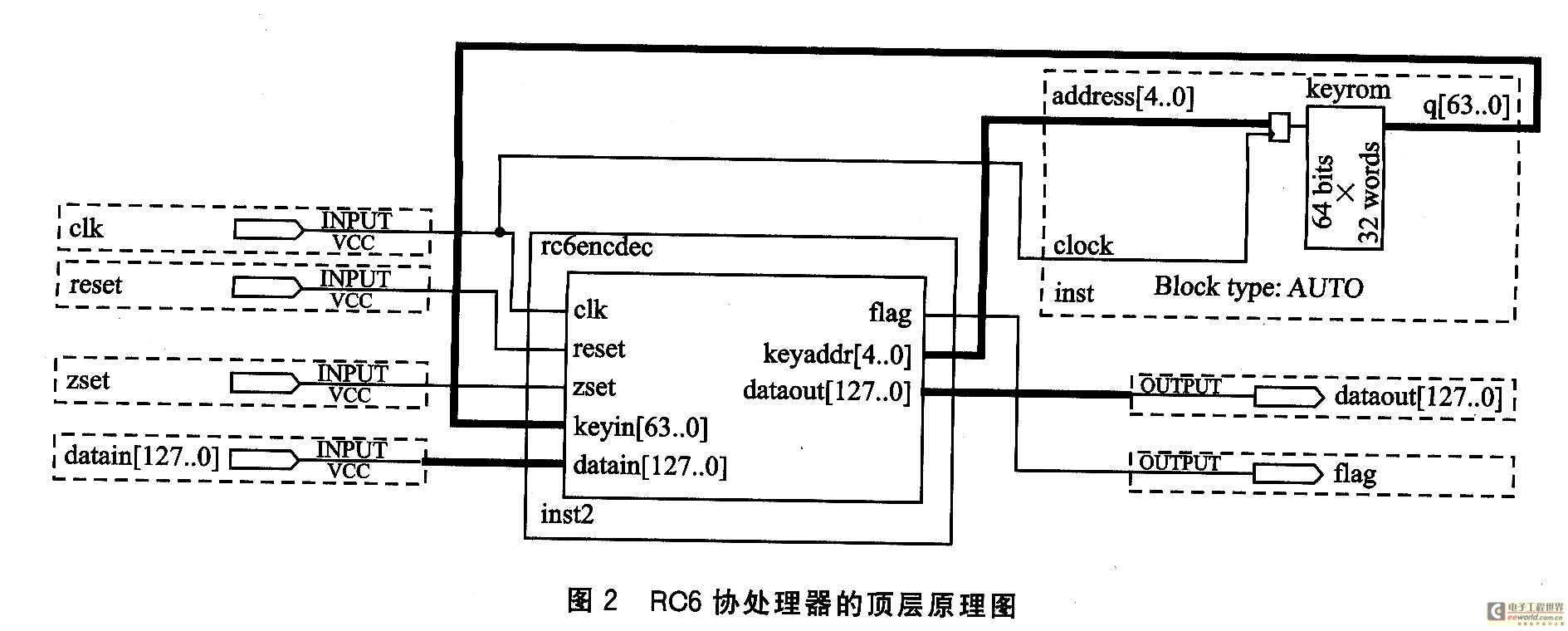

圖3為QuartusII自動生成的ROM模塊。ROM取址需要由加解密模塊提供地址輸入,然后輸出子密鑰。輸入地址為address[4..0],輸出為q[63..0]兩個子密鑰一起輸出到主程序中進行。

ROM模塊在輸入地址和得到子密鑰數據之間,有一定的延時,從地址“00”輸入,開始讀取到輸出子密鑰總時間約一個時鐘周期左右。所以在主函數調用ROM時,需提前1~2個時鐘輸入地址。

由以上5個函數和加解密控制信號,可以實現此算法的一次計算。主函數將需要進行計算的128位數據da—tain、2個子密鑰keyl和key2,以及加解密控制信號輸入到RFunct函數里;函數rfunct將其分配到a、b、c、d四個寄存器,計算b=(b+b+1)×b和d=(d+d+1)×d;然后調用左移函數計算templ=b<<<5和temp2=d<<<5,調用afunct和cfunct計算a和c,再重組a、b、c、d為dataout,結束運算后輸出dataout。

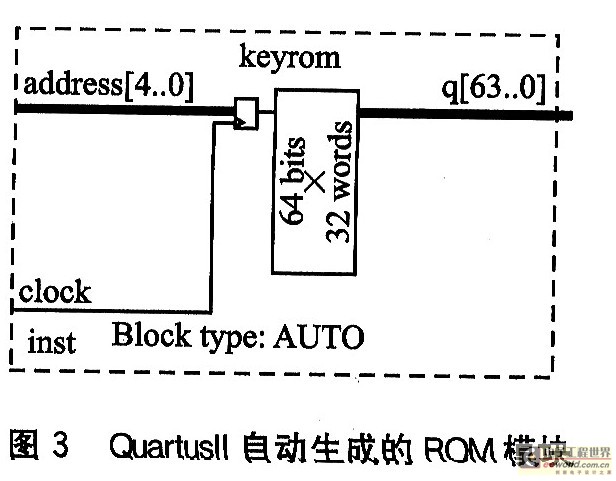

2.3.3 加解密控制模塊

如圖4所示,RC6加解密端口定義為:

輸入端口

- reset:復位信號,高電平有效。

- clk:工作時鐘。

- zset:加解密選擇信號,高電平為加密操作,反之則為解密操作。

- keyin[63..O]:從ROM輸入的子密鑰輸入。

- datain[127..O]:待加解密數據的輸入端。

輸出端口

- flag:加解密結束信號,高電平有效。

- keyad出[4..O]:向ROM輸入5位的地址信號。

- dataout[127..O]:RC6加解密模塊輸出的128位加解密后的數據。

模塊功能

從ROM模塊中,接收包含2個子密鑰的數據keyin,并在前32位和后32位分別為一個32位子密鑰,根據zset信號對密鑰和數據進行加解密操作。

在主程序中利用一個狀態機來實現加解密運算:第1個狀態進行數據的初步處理,將128位數據分成4個32位數據保存在a、b、c、d這4個寄存器中;第2個狀態進行數據的初步運算,將結果保存在128位寄存器data中;第3個狀態和第4個狀態控制循環運算與ROM進行20次交互,一邊接收ROM子密鑰數據,一邊對data進行運算,最后一個狀態,接收最后2個密鑰,進行最后的加解密運算,得到新的a、b、c、d,重新組合成加/解密后的數據,將其輸出。

2.3.4 加解密頂層模塊

RC6加解密算法的頂層模塊包括了加解密控制模塊和ROM模塊。輸入/輸出信號描述如下:

輸入信號

- reset:復位信號,高電平有效。

- clk:工作時鐘。

- zset:加解密選擇信號,高電平加密操作,反之則為解密操作。

- datain[l27..0]:待加/解密數據的輸入端。

輸出信號

- flag:加解密結束信號,高電平有效。

- dataout[l27..0]:128位加解密后得到的數據。

此加解密模塊需要260個I/0端口,如果加入串口通信,可將128位的輸入信號和輸出信號分別利用l位的輸入端口和1位的輸出端口來實現數據傳輸,非常方便。

2.4 仿真結果分析

圖5為RC6加解密算法的功能仿真圖,輸入和輸出是128位。當輸入明文為128位全零數據時,得到的加密結果是36A5C38F78F781564EDF29C11EA44898,解密結果是全零。另外,還測試了其他的一些數據,根據官方公布的標準,此加解密模塊功能正確。

在進行仿真時,RC6加解密模塊工作時鐘周期為100ns,頻率為10 MHz。從reset低電平開始后的第一個時鐘上升沿(0.45μs),至加解密運算結束并輸出結束信號flag(上升沿,8.958 376μs),總共耗時約為8.5μs。

圖5 RC6加解密算法功能仿真圖

結 語

本文基于FPGA技術,實現了RC6算法。整個設計包括加解密函數模塊、加解密控制模塊、ROM模塊、UART模塊、輸入/輸出控制模塊等,通過軟件的仿真,并將程序下載到FPGA芯片進行硬件調試,驗證了設計的正確性和有效性。