摘 要: 隨著電子信息技術的不斷發展,電子系統模塊化的設計思想已經深入人心。因此,加強軟件和硬件模塊設計經驗的相互借鑒意義重大。針對這種情況,借助于有限狀態機理論,提出了一種將C程序轉化成Verilog HDL描述的具體方法。同時,詳細介紹了有限狀態機理論,分析了在利用有限狀態機進行設計時應該遵循的準則,并給出了一個具體的轉化實例和最終的仿真結果。從仿真結果可以看出此方法是可行的。

關鍵詞: 有限狀態機(FSM);Verilog HDL;硬件設計;C程序

0 引言

近年來,電子系統的模塊化設計思想越來越成熟,在一些實際的電子系統設計過程中,通常將整個系統分成軟件和硬件兩個系統分別進行設計,然后再進行整合,而一些比較成熟的綜合開發工具使得軟件和硬件的設計流程更加統一。在硬件設計過程中主要使用可編程邏輯器件(PLD),形成電路網表結構,實現具體的邏輯,這樣的配置可以實現用于軟件用途的硬件[1]。

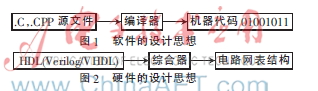

但是,軟件設計的思想和硬件設計的思想是截然不同的。軟件設計過程中首先是通過具體的算法描述實際的問題,再通過一些具體的編程語言去編寫程序,然后通過相應的編譯器編譯連接,生成機器可以識別的二進制代碼,最后這些代碼在具體的微處理器上執行[2]。而對于硬件的設計則是通過一些比較成熟的綜合工具將HDL編寫的代碼綜合成實際的電路網表結構,最終形成具體的電路結構。圖1和圖2分別表示了兩者設計思想之間的區別。

因此,如何實現C程序和Verilog HDL之間的轉化就尤為重要。下文將重點論述如何借助于有限狀態機,將C程序轉化為Verilog HDL,并給出了其理論依據和具體的實現步驟。

1 有限狀態機理論

有限狀態機(Finite State Machine,FSM)是表示有限個狀態以及在這些狀態之間的轉移和動作等行為的數學模型,狀態機用來描述發生有先后順序或者有邏輯規律的事情。狀態機是對一些具有邏輯順序或具有時序規律的事件進行描述的一種方法。

利用有限狀態機進行設計有以下幾個優點:綜合器易于進行優化;較容易構成性能良好的時序邏輯模塊;整個結構模式簡單,層次分明,易讀易懂,而且容易進行排錯;運行模式類似于CPU的運行模式,可以進行順序控制;系統的可靠性高,運行狀態穩定。

有限狀態機設計的重點在于狀態的劃分、過程的描述方式和狀態的編碼方式。在狀態的劃分過程中要明確每個狀態的輸入輸出和狀態之間的轉移條件。

有限狀態機的過程描述方式可分為單過程描述、雙過程描述和三過程描述。在實際的有限狀態機設計時更多的是采用雙過程和三過程進行描述。雙過程的描述有利于綜合器優化代碼,也便于閱讀和維護,缺點是組合邏輯的輸出可能會產生毛刺[3];三過程的描述與雙過程描述相比,雖然代碼的結構較復雜,但是沒有毛刺的輸出,而且有利于綜合;單過程的描述會使得代碼相對比較冗長,難以修改和調試,不利于代碼的長期性維護,不利于附加約束,優化綜合效果差,會導致邏輯速度變慢,資源消耗增多,一般情況下不采用這種過程描述方式[4-5]。

通常對于FPGA器件來說,采用一位熱碼編碼可以有效提高電路的速度和可靠性,也有利于提高器件資源的利用率。在實際的設計過程中,更多的是采用One-Hot編碼方式進行編碼[6]。

2 理論依據和具體實現步驟

C語言作為一種面向過程的程序設計語言,在程序設計的過程中首先要分析出解決問題所需要的步驟,然后用函數把這些步驟一步一步地實現,在使用時逐步去調用這些函數,從而解決這些問題[7]。有限狀態機正是將一個Verilog HDL程序中要表述的問題劃分成不同的狀態進行解決,通過狀態的不斷轉換從而實現分步解決問題的目的,這與C程序的語句執行方式是相同的。因此,可以借助于有限狀態機,用Verilog HDL去實現C程序。下面是將C程序轉化為Verilog HDL進行描述的具體步驟:

(1)對于一個完整的C程序,先用算法流程圖將其整個程序流程詳細表述出來;

(2)根據程序的實際要求,將整個算法流程分成若干個狀態,確定好每個狀態的輸入輸出和狀態之間的轉換條件,用狀態轉移圖描述整個算法流程圖;

(3)用Verilog HDL描述其狀態轉移圖,然后進行綜合,最后進行仿真驗證;

(4)在劃分狀態時應注意相同狀態的合并,減少不必要的狀態,簡化程序。

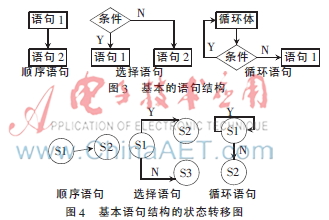

可以根據下面的基本單元模塊用狀態轉移圖描述算法流程圖。圖3所示的順序語句、選擇語句和循環語句是構成一個C算法流程圖的基本單元,圖4是其基本單元的狀態轉移圖。

3 設計舉例及其C程序表示

下面講述一個利用C語言編寫的、以51單片機作為微處理器實現的一個汽車尾燈控制程序,已知汽車左右兩側各有4個尾燈。要求:(1)當汽車正常行駛時所有的燈全滅;(2)剎車時所有的燈全亮;(3)左拐彎時,只有左側四個燈閃爍;(4)右拐彎時,只有右側的四個燈閃爍。先畫出整個程序的算法流程圖如圖5所示,其中S1用來檢測剎車信號,S2用來檢測左拐彎信號,S3用來檢測右拐彎信號。

如下是用偽代碼表示的為51單片機編寫的C程序:

#include<reg52.h>//頭文件

/*用開關S1產生剎車信號,開關S2產生左拐彎信號,開關S3產生右拐彎信號*/

sbit S1=P2^0;//開關S1按下表示產生剎車信號

sbit S2=P2^2;//開關S2按下表示產生左拐彎信號

sbit S3=P2^4;//開關S3按下表示產生右拐彎信號

void keyscan();//按鍵信號檢測

void main()

{

while(1)//循環檢測

{

keyscan();//不斷掃描按鍵,檢測是否有信號產生

switch(k)//判斷檢測到的信號類型

{

/*P1口的低四位表示左側的四個燈,高四位表示右側的四個燈,低電平點亮*/

case1:P1=0x00;break;//剎車信號,所有燈全亮

case2:P1=0xF0;break;//左拐彎信號,左側燈閃爍

case3:P1=0x0F;break;//右拐彎信號,右側燈閃爍

default:P1=0xFF;break;//正常行駛,所有燈全滅

}}}

4 Verilog HDL描述及其仿真

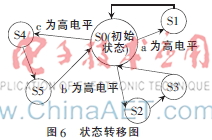

下面用Verilog HDL來描述上述C程序。首先根據圖5的算法流程圖畫出狀態轉移圖,如圖6所示。將其整個算法流程分成S0~S5共6個狀態,其中S0為初始狀態,檢測信號的產生;S1狀態用來處理剎車信號;S2、S3狀態用來處理左拐彎信號;S4、S5用來處理右拐彎信號。

用Verilog HDL描述圖6的狀態轉移圖,其完整代碼如下所示:

module ex(clk,qout,a,b,c);

/*輸入信號a,b,c為高電平時分別表示剎車信號,左拐彎信號和右拐彎信號*/

input clk,a,b,c;

/*輸出信號qout的低四位表示左側的四個燈,高四位表示右側的四個燈,其中低電平有效*/

output reg[7:0]qout;

reg[4:0]current_state,next_state;

/*采用One-Hot編碼方式進行編碼*/

parameter s0=5′b00000,s1=5′b00001,

s2=5′b00010,s3=5′b00100,

s4=5′b01000,s5=5′b10000;

always@(posedge clk)

current_state<=next_state;

always @(posedge clk)

begin

case(current_state)

s0:begin if(a)next_state<=s1;else if(b)

next_state<=s2;else if(c)

next_state<=s4;

end

s1:next_state<=s0;s2:next_state<=s3;

s3:next_state<=s0;s4:next_state<=s5;

s5:next_state<=s0;default:next_state<=s0;

endcase

end

always@(current_state)

begin

case(current_state)

s0:qout<=8′b11111111;

s1:qout<=8′b00000000;

s2:qout<=8′b11110000;

s3:qout<=8′b11111111;

s4:qout<=8′b11111111;

s5:qout<=8′b00001111;

default:qout<=8′bzzzzzzzz;

endcase

end

endmodule

圖7為波形仿真圖,從圖中可以看出:(1)當a為高電平時,產生剎車信號,qout信號在S1狀態輸出低電平;(2)當b為高電平時,產生左拐彎信號,qout信號的低4位在S2、S3狀態分別輸出低電平和高電平,產生閃爍信號;(3)當c為高電平時,產生右拐彎信號,qout信號的高4位在S4、S5狀態分別輸出低電平和高電平,產生閃爍信號;(4)從(1)~(3)可以看出其仿真結果是正確的,符合程序的基本要求,文中的方法是可行的;(5)用三過程進行描述時,無毛刺的輸出,而且容易進行綜合,采用One-Hot編碼方式可以提高電路的速度和可靠性,同時也可以提高器件資源的利用率。

5 結論

通過上文的表述,借助于有限狀態機,可以參考文中的方法實現用Verilog HDL描述C程序,從而可以通過實際的電路結構來實現軟件程序的功能,這種方法也可以實現Verilog HDL程序和C程序之間的相互轉換。同時,文中也歸納出在利用有限狀態機進行設計時應該遵循的原則。

參考文獻

[1] 楊海鋼,孫嘉斌,王慰.FPGA器件設計技術發展綜述[J].電子與信息學報,2010,32(3):714-723.

[2] 范華,秦茂玲,張俊.透視C程序設計語言[J].計算機技術與發展,2008,16(6):64-66.

[3] 王春旭,周曉平,王黎黎.基于FPGA的Verilog HDL語言設計優化[J].電子元器件應用,2009,10(11):45-47.

[4] 魏芳,劉志軍,王立華.基于Verilog HDL的可綜合有限狀態機設計[J].電子工程師,2006,32(6):8-10.

[5] 劉小平,何云斌,董懷國.基于Verilog HDL的有限狀態機設計與描述[J].計算機工程與設計,2008,29(4):958-960.

[6] 龔書濤,呂國強,彭良清.在FPGA中狀態機的編碼方式[J].電子工程師,2005,31(11):51-52.

[7] 丁亞濤.C語言程序設計(第二版)[M].北京:高等教育出版社,2006.